Speedster7t FPGA芯片中GDDR6硬核控制器详解

可编程逻辑

描述

作者:Achronix资深应用工程师 黄仑

1. 概述

为了适应未来硬件加速、网络加速对片外存储器的带宽需求,目前市面上的高端FPGA主要采用了两种解决方法。第一种最常见的就是HBM2高带宽存储器,2016年1月,HBM的第二代技术HBM2正式成为工业标准。集成了HBM2存储器的高端FPGA可以提供高达460GB/s的带宽,但是因为HBM2技术工艺要求高,目前芯片的良率和产量都会受到很大的影响,所以集成HBM2的高端FPGA成本一直居高不下。第二种是GDDR6存储器,2018年,GDDR6发布,数据速率达到了16Gbps。Achronix看中了GDDR6在数据存储中的带宽优势,在新一代7nm工艺的Speedster7t FPGA集成了GDDR6硬核控制器,最高可支持高达512GB/s的带宽,同时可以有效地控制使用成本。

2. Speedster7t FPGA中的GDDR6控制器

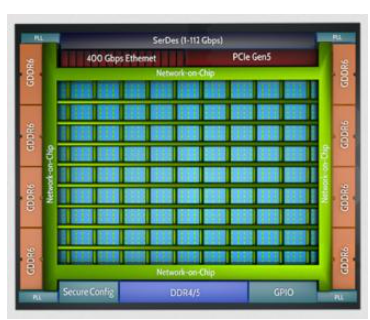

Achronix的Speedster7t FPGA集成了8个GDDR6的硬核,如图1所示。

图1 Speedster7t FPGA架构

每个GDDR6的硬核支持双通道。总的带宽是16Gbps x 16(位宽) x 2(通道) x 8(控制器)/8 = 512 GB/s,每个控制器有两个独立的访问通道,每个通道的数据位宽为16位。这些GDDR6 控制器和PHY都是硬IP,无需消耗FPGA中的可编程逻辑资源,也无需面对布局布线所带来的时序收敛挑战。这些特征共同使GDDR6方案成为当前高端FPGA性能和成本兼顾的绝佳选择。

3. GDDR6子系统概述

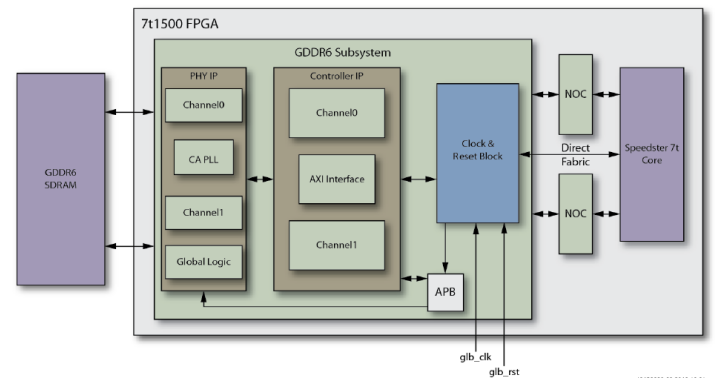

Achronix Speedster7t GDDR6子系统包括GDDR6 PHY和GDDR6控制器,全部采用了硬核设计。整个子系统包括GDDR6 PHY IP、GDDR6控制器IP、时钟和复位模块,APB接口和AXI4用户接口可以连接到二维片上网络(2D NoC)或者内部编程逻辑,如图2所示。

图2 Speedster7t GDDR6子系统框图

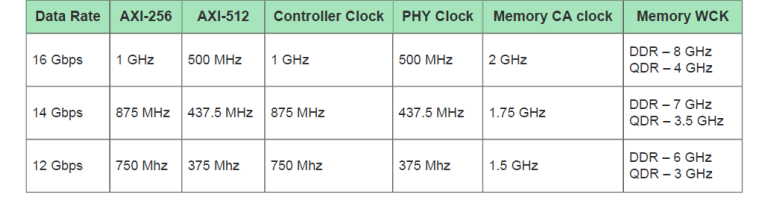

时钟和复位模块用来产生支持GDDR6 PHY和GDDR6控制器的时钟以及所需的复位信号,它的输入时钟来自于FPGA片上的PLL。对于数据速率为16Gbps的GDDR6,控制器时钟为1GHz,PHY时钟为500MHz,命令地址时钟跑在2GHz,word clk也就是WCLK运行在8GHz,其他速率需要的时钟如表1所示。

GDDR6控制器IP支持两个通道,每个通道为16bit位宽。两个通道独立访问不同的GDDR6空间。控制器的用户接口为标准的AXI协议,可以连接到二维片上网络上或者直接连到内部的可编程逻辑。在另外一边,控制器和PHY的接口为DFI4.0接口。

表1 GDDR6支持的时钟频率模式

PHY IP用来连接器件外围的高速GDDR6颗粒,它会像其他DRAM PHY一样产生PRECHARGE、ACTIVE和REFRESH等命令。

APB全称Advanced Peripheral Bus,字面上是先进外围总线的意思,该总线协议是ARM公司提出的AMBA总线结构之一,已成为一种标准的片上总线结构。APB总线接口工作在250MHz,用来配置GDDR6子系统的寄存器,Speedster7t FPGA的配置电路FCU可以在启动的时候通过APB总线接口配置GDDR6子系统的寄存器,用户逻辑模块也可以在FPGA运行的时候通过APB总线接口动态配置GDDR6子系统的寄存器。

4. GDDR6控制器结构

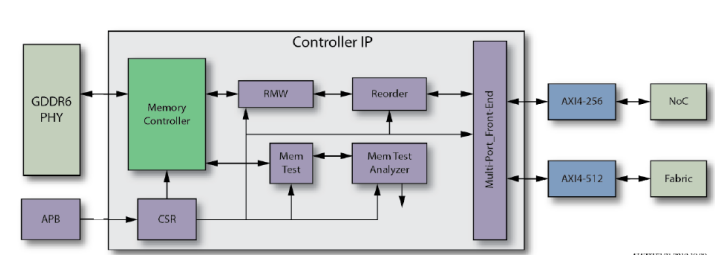

GDDR6控制器模块的详细结构如图3所示。它包括主控部分和其他的一些子模块,比如Multi-port front-end模块,Reorder模块,Read modify Write模块,内存测试模块和内存测试分析模块。

MPFE模块是前端多端口模块,Speedster7t上的GDDR6控制器为每个通道提供了两个MPFE端口,它们支持AXI4协议,每个端口能够提供最大256Gbps的带宽;其中一个AXI端口用于连接到二维片上网络上,位宽为256位,时钟是1GHz。另一个AXI端口用于直接连接到FPGA内部的可编程逻辑资源,位宽为512位,时钟是500MHz。

Reorder模块用来调整发给GDDR6控制器的用户请求的顺序。Reorder模块里有一个深度为64的队列,用于缓存用户请求,只要队列不满就可以接收新的用户请求。在接收到用户请求以后,Reorder模块可以调整用户请求的顺序,进而可以大大提高DRAM的访问效率。用户可以通过设置不同的参数来调整reorder的标准,同时这个模块也可以bypass掉,维持用户请求的原来顺序。

RMW模块是读-修改-写的模块,先读出内存中的数据内容,然后修改单个或者多个bit以后再整体写回。有了这个模块,GDDR6控制器支持将地址mask的功能。

Mem Test和Mem Test Analyzer是用于内存测试的模块,Mem Test内存测试模块支持生成不同的数据类型去写入GDDR6;Mem Test Analyzer内存测试分析模块将读到的数据与期望的数据进行比较,从而验证GDDR6的硬件接口和读写功能是否正常。

图3 Speedster7t GDDR6控制器框图

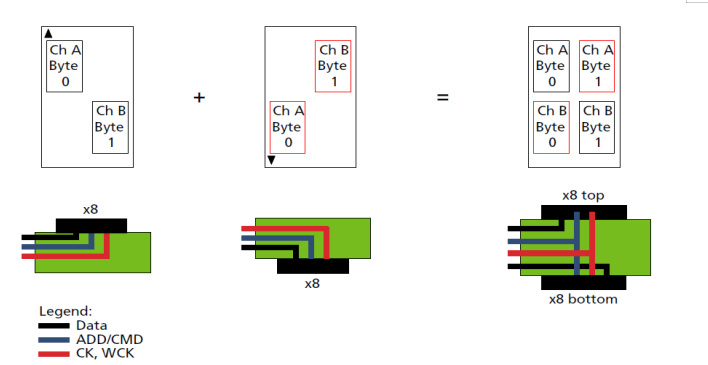

GDDR6控制器支持两种模式,正常x16模式和Clamshell x8模式。在x16模式下,控制器提供了每通道16位的双通道接口,可以连接一个GDDR6颗粒。在Clamshell x8模式下,如图4所示,控制器提供了每通道8位的双通道接口,可以连接两个GDDR6颗粒。Clamshell模式提供了一种在不改变控制器带宽的情况下,通过在两个GDDR6颗粒间share地址和命令总线将容量加倍的一种方法。

图4 GDDR6 Clamshell模式

后面我们还会继续深入了解Speedster 7t FPGA上的一些其他特性,以及这些特性如何运用在数据加速和网络加速应用中,敬请期待。如需更多信息或者有任何疑问您可以通过Achronix公众号里联系方式联系我们,也可访问Achronix公司官方网站http://www.achronix.com

参考文献:

1.Micron 8Gb/16Gb GDDR6 Product Brief

2.Achronix website www.achronix.com

-

Achronix Speedster7t FPGA如何运用GDDR6满足网络产品的高带宽需求2020-02-17 2068

-

紫光国芯发布GDDR6控制器芯片:12nm工艺 速率可达16Gbps2020-11-09 3555

-

利用NoC资源解决FPGA内部数据交换的瓶颈2020-09-07 2831

-

如何利用NoC资源去支撑FPGA中的创新设计2020-10-20 1687

-

如何缓解GDDR6 DRAM实施所带来的挑战2021-01-01 2217

-

请问在Speedster7t FPGA中增加NoC能带来哪些好处?2021-06-17 1416

-

探究GDDR6给FPGA带来的大带宽存储优势以及性能测试(上)2021-12-21 5990

-

探究GDDR6给FPGA带来的大带宽存储优势以及性能测试(下)2021-12-22 5914

-

Achronix推全新7nm FPGA 首度支持GDDR6高带宽存储2019-06-10 1651

-

Achronix联合BittWare推出了VectorPath S7t-VG6 PCIe加速卡2019-11-27 7855

-

凭借12nm工艺,国产芯片终杀进GDDR6存储控制器市场2020-11-07 4032

-

Achronix展示Speedster7t高性能接口 贸泽备货Molex电路板连接器2022-03-17 4528

-

Achronix Speedster7t FPGA芯片中2D NoC的设计细节2022-04-21 2468

-

Speedster7t FPGA中可编程逻辑的架构2022-07-05 2021

-

基于Achronix Speedster7t FPGA器件的AI基准测试2024-09-18 1773

全部0条评论

快来发表一下你的评论吧 !