基于TMS320F2812DSP的测频方法及数字频率计的方案

处理器/DSP

899人已加入

描述

本文给出一种基于TMS320F2812(简称F2812)DSP的一种简易测频方法。该方法有效利用F2812的片内外设事件管理器的捕获功能,在被测信号的有效电平跳变沿捕获计数,电路实现多靠软件设置,运算简单,实时性好,测量精度高。

1 测量方法

常用的测频方法主要有直接测频法、直接测周法以及多周期测量法。直接测频法虽在高频段的精度较高,但在低频段的精度较低,直接测周法则恰恰相反。多周期测量法是将被测信号和标准信号分别输入到两个计数器,其实际闸门时间不是固定值,而是被测信号周期的整数倍,因此消除了对被测信号计数时产生的±1 Hz的计数误差,其精度仅与闸门时间和标准频率有关。因此本设计采用多周期测量法作为具体的实施方案。

2 系统的设计

2.1 系统的硬件设计

硬件系统总体框图如图1所示。被测信号首先经过限幅放大、直流偏置、整形电路,变换为0~3.3 V的方波信号,然后再进入DSP,利用其定时器和捕获单元实现频率的测量。测量完成后,一方面可由键盘设置相关参数通过LCD显示测量结果,另一方面可通过RS一232传送给PC机显示测量结果。另外,为了提高系统的可靠性,增加了一个自我校准电路,即在测量之前,可通过软件设置产生1 MHz的标准脉冲信号,送到信号调理模块的输入端,检测测量结果是否正确,从而达到自我校准的目的。

本设计选用美国德州仪器公司(TI)的TMS320F2812 DSP作为核心处理单元。F2812是TI公司近几年推出的高速、高精度的工业控制DSP芯片。它运算速度快,工作时钟频率达150 MHz,指令周期可以达到6.67 ns以内,低功耗(核心电压1.8 V,I/O口电压3.3 V)。它采用哈佛总线结构,具有强大的操作能力;外围设备包括3个32位的CPU定时器,16通道的12位A/D转换器,串行外围接口(SPI),2个串行通信接口(SCI)等。其片内外设时间管理器含有2个模块(EVA和EVB),每个模块都包括2个通用定时器,3个全比较/PWM单元,3个捕获单元和 1个正交编码脉冲电路。本设计主要利用EVA中的2个通用定时器(T1和T2),2个捕获单元(CAPl和CAP3),EVB中的1个通用定时器 (T3)。具体测量原理如图2所示。

首先设定T3比较值(预置闸门时间为0.012 8 s),设定T1的比较值为1,使能CAPl。然后使能T1,当其接收到一个整周期的被测信号时即可产生比较输出,同时产生比较中断,读取CAPl的栈值 (即T2的初值t2_1),清T1、T2上溢次数,使能CAP3和T3。最后当T3定时结束,借助于D触发器在被测信号的下一个上升沿到来时,切断T1的比较输出,同时PDPINTA将被置位,然后记录T1和T2的上溢次数tlofcount、t2ofcount,读取CAPl的栈值(即T2的末值 t2_2)和CAP3的栈值(即T1的末值tl_2)。由所得数据计算频率,禁止T1、T2、CAPl和CAP3。频率计算公式为:

注意:CAPl的捕获时基为T2,CAP3的捕获时基为T1,标准频率信号为150 MHz时钟频率的8分频。

2.2 系统的软件设计

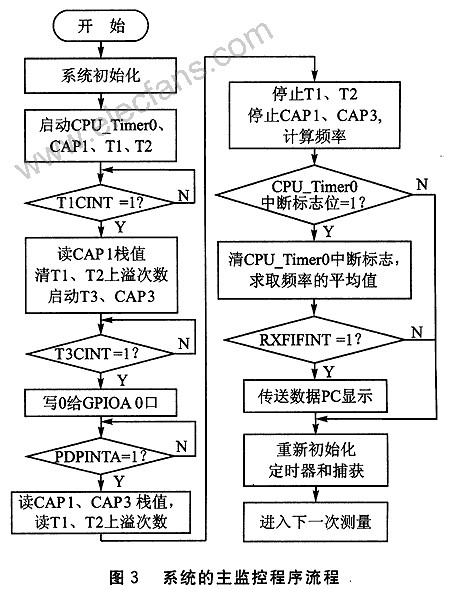

主监控程序是整个软件系统的总调度程序,它控制着程序的有序运行。系统在上电或复位后,主程序先调用各模块的初始化子程序,主要包括GPIO初始化、PIE初始化、EV初始化和SCI初始化。系统初始化完成之后,主程序启动CPU_Timer0,使能 T1、T2的上溢中断,启动CAPl,设置T1的比较值为1,等待T1CINT置位,开始测量频率。为减小测量过程中产生的随机误差,所测结果均取平均值。利用CPU_Timer0产生一定的时间段(O.6s)。该时段结束后(CPU_TimerO中断标志位置位),即对该段时间段内记录的测量结果求均值。此时,如果查询到上位机发出接收请求,则传送相应数据至PC显示。然,后,重新初始化定时器和捕获单元,进入下一轮测量。主监控程序流程如图3所示。

测频的部分源代码如下:

3 误差分析及测试结果

3.1 量化误差

设被测信号的频率为Fx,其真实值为Fxe,标准频率为Fs,在一次测量中,预置闸门时间为T′,Tpr为实际闸门时间,被测信号计数值为Nx,标准频率信号计数值为Ns。

Fx计数的起停时间是由该信号的上升沿触发的,在T′时间内对Fx的计数Nx无误差,对Fs的计数Ns假设相差N个脉冲,即|△et|≤n。

由于Fx/Nx=Fs/Ns,Fxe/Nx=Fs/(Ns+△et),根据相对误差公式有:

因此可以得到以下结论:

①相对测量误差与被测信号的频率无关。

②增大T′或者提高Fs,可以增大Ns,减少测量误差,提高测量精度。本设计方案中,预置闸门时间限定了最低的测量精度。

③误差分析中的n,主要由硬件切断T1PWM所需要的时间决定,为一个小整型常数。若预置闸门时间Tpr=O.012 8 s,则

即使n取不为l的小整型常数,仍可以使得精度维持在十万分之一以内,并且可以随着预置闸门时间的适当延长,得到进一步的提高。

3.2 测量的原理误差和标准频率误差

本测量原理类似多周期同步测量原理,主要的原理误差来自测量即将结束时,由D触发器产生低电平跳变来切断T1PWM,从而使其产生由CAPl和CAP3同时捕获上升沿的跳变。这段时间主要是由D触发器的反应时间决定。在测量过程中,针对这部分误差,可以通过适当增加预置闸门的时间来克服,同时考虑到DSP 内部高速的时钟频率,这并不会明显地增加测量耗时,但却达到了弱化此误差的影响、增加测量精度的目的。

标准频率误差为△Fs/Fs。因为晶体的稳定度很高,标准频率误差可以进行校准,并且已将DSP内部的高速时钟频率进行了适当的分频,所以相对于量化误差,校准后的标准频率误差可以忽略不计。

3.3 测试结果

用函数信号发生器(型号为Tektronix AFG3010;精度为O.000 1%)产生方波信号,用设计的频率计测出频率,求出误差。本测频系统的测量精度可达到O.01%。根据误差分析可知,系统的最大误差发生在预置闸门时间正好填充了整数个被测信号时,即频率为78.125 Hz或者其整数倍时,所以选择这些点进行测试。实际的测试数据如表1所列。

4 结论

本文着重分析了数字频率计的设计方案、硬件组成,以及采用Modbus协议实现上位机与下位机通信的软件设计。特点有:

①在频率测量原理方面,由于采用了多周期测量原理,消除了对被测信号计数时产生的±1个计数误差,其精度仅与闸门时间和标准频率有关,克服了传统的测频法或测周法的不足,实现了宽量程、高精度的频率测量。同时由于预置闸门时间的存在,保证了当被测频率在各频段之间来回切换时,系统反应灵敏,跟随性能好。

②在系统的总体设计方面,充分利用了F2812 DSP的内部资源,即使用事件管理器中的定时器、捕获单元完成频率的测量;使用PWM的输出实现自检电路的设计;使用串口通信模块完成上位机和下位机的通信。在测量结果的显示方面利用RS232,通信协议采用Modbus协议,实现下位机和上位机的通信,将测量结果在上位机中显示出来。

本文只探讨了如何对单路信号进行频率测量,而对于多路信号,可先使其经过一个与门,通过软件判断哪一路信号,然后再运用本设计方法进行测量。针对这种情况所产生的误差问题还需作进一步的探讨,本文只给出初步的探索。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- TMS320F281

- 数字频率计

-

数字频率计测频率的基本原理2008-12-01 4141

-

基于TMS320F2812的数字频率计2010-04-30 624

-

数字频率计电路图2009-04-11 6048

-

基于单片机的数字频率计的方案2010-03-24 6807

-

数字频率计2011-04-07 4255

-

设计简易数字频率计2011-06-28 8109

-

数字频率计的制作2015-11-20 1413

-

基于verilog语言的数字频率计设计2015-12-08 1655

-

简易数字频率计设计2015-12-14 1797

-

数字频率计设计论文2016-05-06 1103

-

基于Multisim的数字频率计2016-06-21 2664

-

基于FPGA数字频率计的设计2017-08-04 2218

-

基于数字信号控制器TMS320F2812芯片实现嵌入式数字频率计的设计2020-05-03 2934

-

基于TMS320F2812的简易数字频率计2021-06-16 1011

-

微波数字频率计的基本工作原理是什么?2023-12-21 1908

全部0条评论

快来发表一下你的评论吧 !

×

20

完善资料,

赚取积分

赚取积分