RISC-V批准的新规范意味着什么?

描述

美国时间12月2日,RISC-V国际基金会宣布其成员批准了15项新规范,包含了RISC-V指令集架构下的40多个扩展,其中重点强调的就是其矢量、标量加密和Hypervisor三条规范。RISC-V国际基金会表示,这些规范为AI、机器学习、IoT、汽车和数据中心等市场创建了新的机遇,那么对于RISC-V这个仍在蓬勃发展的架构来说,这些规范究竟意味着什么呢?

向量处理

过去向量计算往往只用于气象预报和声呐研究等细分市场,如今人工智能的兴起下,向量运算开始扩展到所有类型的应用和解决方案中,甚至在某些语音和视觉的机器学习推理中成了主要运算方式。

RISC-V的向量规范带来的RISC-V向量扩展,为数据运算密集的应用敞开了大门。该扩展已于今年9月进入冻结公共审核阶段,如今终于通过批准。RISC-V的向量扩展仅有100多条指令,但凭借这些指令,开发者就可以在RISC-V架构的处理器上迅速应对复杂的运算工作,比如稀疏矩阵运算等,并做到极低的延迟。

RISC-V向量扩展中还有针对嵌入式设备和MCU的扩展Zve,为性能不高的RISC-V CPU核心提供32/64整数、单精度和双精度的浮点向量运算,满足边缘端日益增长的算力要求。这样不论是消费级的IoT设备,还是工业级的机器学习应用,都能从中获利。

标量加密

安全是任何一个架构都不容小觑的一环,从支持安全的加密标准到防范x86曾遇到的Spectre和Meltdown等漏洞,RISC-V在加密上同样没有放松。

标量加密规范将为小规模的加密工作带来加速,这些扩展显著降低了物联网和嵌入式设备中安全高效的加速加密技术门槛。标量加密扩展的引入,使得RISC-V在实现某些标准的哈希加密或分组加密算法时,要比直接使用标准指令快一个数量级。

根据RISC-V国际基金会CTO Mark Himelstein的说法,在使用标量加密扩展后,64位的RISC-V运行AES128加密算法所需指令数从1145条下降至78条,提升性能的同时也加强了对边信道攻击的防范。除了性能和安全优势外,引入标量加密扩展所需成本也非常低,不需要像向量处理器一样占用芯片大量的逻辑空间,开发者可以将目前主流的加密算法集成到最小的设备中。

Hypervisor虚拟化

虚拟化支持也是如今常见的需求之一,无论是数据中心还是嵌入式设备,都开始引入虚拟化技术。RISC-V的虚拟化扩展已经停留在草案阶段许久了,如今终于获得批准,RISC-V社区已经完成了KVM的移植,Linux 5.16版本中的KVM也将正式支持RISC-V的hypervisor扩展,另一大开源虚拟机Xen也在今年三月宣布将考虑支持RISC-V的虚拟化。而SiFive在同一天公布的SiFive P650处理器,也声称支持虚拟化。

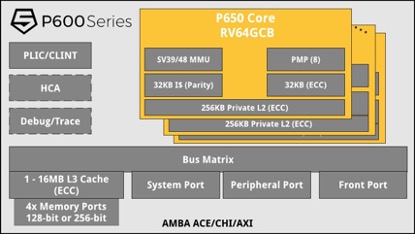

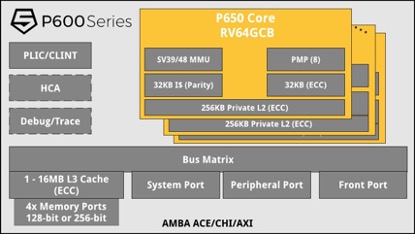

P650处理器 / SiFive

虚拟化技术主要是实现CPU、内存和I/O的虚拟化。RISC-V通过赋予敏感寄存器和指令特权的方式,实现了CPU的虚拟化。在内存虚拟化上,RISC-V和Arm/x86一样,选择实用多阶段页表来实现。RISC-V的Hypervisor规范将supervisor级的架构虚拟化,有效地以type-1或KVM这类type-2的形式托管运行客户操作系统。

RISC-V凭借其扩展性,已经展现了作为加速器的无限潜力,有了虚拟化技术的支持,RISC-V的硬件资源可以得到最大限度的利用,在数据中心的机器和网络基础架构中也将获得更多的机会。

除了数据中心,汽车和工业控制应用也已经全面铺开虚拟化技术,比如UI与控制应用的硬件隔离等等。这也是RISC-V存在感较小的两大市场,有了虚拟化技术的支持,相信RISC-V能够吸引到更多的行业玩家。

小结

尽管RISC-V仍是全球ISA市场中的一小部分,但根据调研机构近期发布的报告,RISC-V的处理器核心将在2022年和2023年实现翻倍式增长。尤其是在这些新规范和新扩展的加入下,欲求快速进入市场的初创小型公司更愿意选择这种开放式的架构。

打开APP阅读更多精彩内容

向量处理

过去向量计算往往只用于气象预报和声呐研究等细分市场,如今人工智能的兴起下,向量运算开始扩展到所有类型的应用和解决方案中,甚至在某些语音和视觉的机器学习推理中成了主要运算方式。

RISC-V的向量规范带来的RISC-V向量扩展,为数据运算密集的应用敞开了大门。该扩展已于今年9月进入冻结公共审核阶段,如今终于通过批准。RISC-V的向量扩展仅有100多条指令,但凭借这些指令,开发者就可以在RISC-V架构的处理器上迅速应对复杂的运算工作,比如稀疏矩阵运算等,并做到极低的延迟。

RISC-V向量扩展中还有针对嵌入式设备和MCU的扩展Zve,为性能不高的RISC-V CPU核心提供32/64整数、单精度和双精度的浮点向量运算,满足边缘端日益增长的算力要求。这样不论是消费级的IoT设备,还是工业级的机器学习应用,都能从中获利。

标量加密

安全是任何一个架构都不容小觑的一环,从支持安全的加密标准到防范x86曾遇到的Spectre和Meltdown等漏洞,RISC-V在加密上同样没有放松。

标量加密规范将为小规模的加密工作带来加速,这些扩展显著降低了物联网和嵌入式设备中安全高效的加速加密技术门槛。标量加密扩展的引入,使得RISC-V在实现某些标准的哈希加密或分组加密算法时,要比直接使用标准指令快一个数量级。

根据RISC-V国际基金会CTO Mark Himelstein的说法,在使用标量加密扩展后,64位的RISC-V运行AES128加密算法所需指令数从1145条下降至78条,提升性能的同时也加强了对边信道攻击的防范。除了性能和安全优势外,引入标量加密扩展所需成本也非常低,不需要像向量处理器一样占用芯片大量的逻辑空间,开发者可以将目前主流的加密算法集成到最小的设备中。

Hypervisor虚拟化

虚拟化支持也是如今常见的需求之一,无论是数据中心还是嵌入式设备,都开始引入虚拟化技术。RISC-V的虚拟化扩展已经停留在草案阶段许久了,如今终于获得批准,RISC-V社区已经完成了KVM的移植,Linux 5.16版本中的KVM也将正式支持RISC-V的hypervisor扩展,另一大开源虚拟机Xen也在今年三月宣布将考虑支持RISC-V的虚拟化。而SiFive在同一天公布的SiFive P650处理器,也声称支持虚拟化。

P650处理器 / SiFive

虚拟化技术主要是实现CPU、内存和I/O的虚拟化。RISC-V通过赋予敏感寄存器和指令特权的方式,实现了CPU的虚拟化。在内存虚拟化上,RISC-V和Arm/x86一样,选择实用多阶段页表来实现。RISC-V的Hypervisor规范将supervisor级的架构虚拟化,有效地以type-1或KVM这类type-2的形式托管运行客户操作系统。

RISC-V凭借其扩展性,已经展现了作为加速器的无限潜力,有了虚拟化技术的支持,RISC-V的硬件资源可以得到最大限度的利用,在数据中心的机器和网络基础架构中也将获得更多的机会。

除了数据中心,汽车和工业控制应用也已经全面铺开虚拟化技术,比如UI与控制应用的硬件隔离等等。这也是RISC-V存在感较小的两大市场,有了虚拟化技术的支持,相信RISC-V能够吸引到更多的行业玩家。

小结

尽管RISC-V仍是全球ISA市场中的一小部分,但根据调研机构近期发布的报告,RISC-V的处理器核心将在2022年和2023年实现翻倍式增长。尤其是在这些新规范和新扩展的加入下,欲求快速进入市场的初创小型公司更愿意选择这种开放式的架构。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

浅析RISC-V领先ARM的优势2024-06-27 1343

-

RISC-V现在发展得怎么样了?2024-06-07 1271

-

RISC-V的MCU与ARM对比2024-05-27 1872

-

RISC-V有哪些优缺点?是坚持ARM方向还是投入risc-V的怀抱?2024-04-28 2274

-

浅谈RISC-V微架构验证方式2024-04-15 1674

-

RISC-V生态强劲 RISC-V International会员超4000 超75个技术工作组2023-11-09 1831

-

RISC-V走向开放服务器规范2023-08-10 1686

-

两大架构RISC-V 和 ARM 的各种关系2023-06-21 1287

-

openEuler加入RISC-V Landscape2023-03-13 2142

-

RISC-V批准的新规范究竟意味着什么2021-12-09 2598

-

RISC-V规范的演进 RISC-V何时爆发?2021-02-11 4382

-

RISC-V 对中国科技界意味着什么?2020-08-21 3406

-

为什么选择RISC-V?2020-07-27 5004

-

正式的RISC-V基础指令集架构与特权架构规范来了,RISC-V基金会已正式批准2019-07-11 11464

全部0条评论

快来发表一下你的评论吧 !