采用CPCI总线的CPU主控模块原理设计

嵌入式新闻

描述

Compact PCI(简称CPCI)总线是“PCI总线工业计算机制造商组织”推出的一种工业计算机总线标准,近年来应用发展最为迅速。它由PC机上的通用总线PCI发展而来,既有PCI总线的高带宽高性能、即插即用、价格低廉等诸多优点,又有无源背板总线VME总线的可靠性。基于CPCI总线的主控模块主要完成通用的计算机主板功能,包括主处理器及相关的支持逻辑、主存储器、PCI总线仲裁器、系统中断控制器、PCI时钟发生器及通用I/0接口(IDE、USB、PS/2键盘鼠标等)功能,还集成了一片PCI-PCI桥PCI2050B,提供7个PCI外设卡的仲裁能力。

1 CPU主控模块原理设计

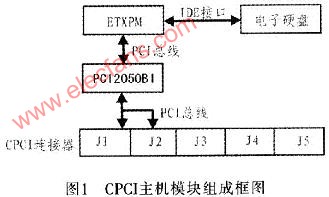

基于CPCI总线的主控模块设计主要采用2种方法:1)应用器件组进行系统板设计。这种方法的优点是逻辑清晰,在功能不正常时可以更换器件使其正常工作,设计出的系统板抗震动及机械冲击性能更强;其缺点是难度大、开发周期长,随着CPU速度的提高,设计难度更大,并且难以购买到温度宽泛的芯片组。2)采用嵌入式CPU模块。该模块集成度高、体积小,它集成了计算机几乎所有的功能,用户根据具体任务的要求,只需对其没有的功能在外部进行扩展就可以完成设计。这种方法的优点是设计和生产周期短,调试方便,易于升级,并且已有厂家提供温度宽泛的嵌入式CPU模块,也应用在对环境要求比较苛刻的军用领域。鉴于项目研发周期短,本设计采用第2种方法,基于CPCI总线主控模块采用控创(Kontron)公司的ETX(Embedded Technology eXtended)PM模块,并应用PCI扩展技术完成6U CPCI总线系统板的设计。CPCI主控模块组成框图如图1所示。

1.1 ETX模块

ETX嵌入式计算机模块具有完整的PC功能和高效的CPU性能,是一种高集成度的计算机系统,它采用的是x86 CPU。ETX PM的主频为1.0~1.8 GHz,内存可至1 GB。ETX结构主板主要面向专用计算机系统板的设计者,它的核心理念是“把PC像器件一样设计到客户的目标应用系统中”。在其114mm(长)x95 mm(宽)×16 mm(高)的尺寸上,集成了标准PC所有的功能,同时提供标准PC架构所具有的所有标准接口。

ETX模块上包含了高性能x86系列的CPU器件组、南北桥、显示器件、网络器件、音频控制器、Super I/0控制器等。背面采用高密度的表贴连接器,4x100引脚总线引脚定义PC的标准接口信号以及PCI和ISA信号等。在设计主控模块时,在主控模块上设计对应的4x100引脚插座,扩展的I/0功能可通过总线上的PCI或ISA实现。每个连接器所提供的信号如下:

1)ETX连接器X1:PCI总线(32位)、USB、声卡;2)ETX连接器X2:ISA总线(16位);3)ETX连接器X3:VGA、LCD(LVDS)、COMl、COM2、IrD-A、键盘/鼠标;4)ETX连接器X4:EIDE(×2)、以太网、电源管理等信号。

ETX:PM模块向外只提供4个PCICLK和4对REQ#/GNT#信号,因此它只能驱动4个PCI功能设备,若要满足CPCI总线主控模块驱动7个扩展插槽的要求,可以通过在ETX PM模块和CPCI系统总线连接器之间增加一个PCI-PCI总线桥来实现总线扩展。PCI-PCI总线桥作为上一级总线的一个负载,而向下可以驱动一个总线段。ETX PM模块可以在-40~85℃的条件下工作,而且ETX系列产品有较长的生命周期,可互换。

1.2 PCI桥的设计

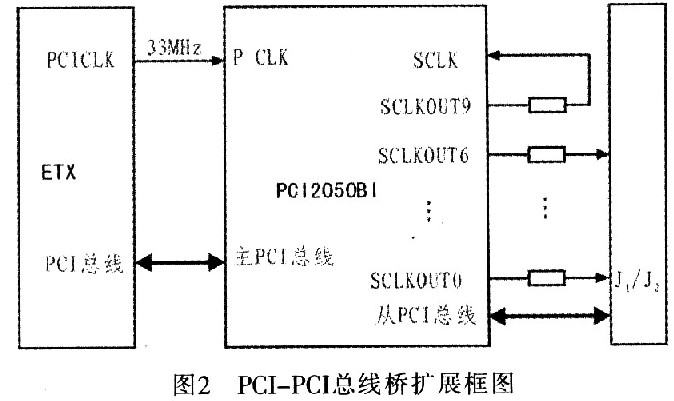

在本方案主控模块的设计中,选用Tl(Texas Instruments)公司的工业级PCI-PCI桥器件PCI2050BI,它在2个32位最高工作频率66 MHz的PCI总线之间提供桥连接。该桥支持突发模式(burst mode transfers),极大增加了数据的吞吐量,桥的总线数据路径(bustraffic paths)独立工作。桥的主、从PCI总线分别可以工作在3.3 V或者5 V的工作环境下,桥的核心逻辑工作在3.3 V以减少功耗。PCI2050BI可以带9个设备,除了为每个设备提供内部仲裁,也可由系统提供外部仲裁。PCI2050BI提供lO个设备时钟输出。使用PCI2050BI生行PCI-PCI总线桥扩展,其设计框图如图2所示。

本系统设计主要包括:

本系统设计主要包括:

1)PCI2050BI有2个独立的时钟域,主接口受主侧输入时钟P_CLK的控制,从接口受从侧输入时钟S_CLK的控制。这2个时钟可以相互独立,但必须保持同步,P_CLK与S_CLK的最大延时不得超过7 ns,S_CLK不能超前P_CLK;

2)PCI2050BI的从侧输出时钟,每个时钟只能驱动1个负载;

3)PCI2050BI的从侧有10个时钟输出S_CLK[9:0],其中的9个可以供给扩展的PCI槽,另一个S_CLK0UT9信号必须反馈给从总线的输入时钟S_CLK;

4)为了减小时钟的信号反射,输出到扩展槽的9个CLK必须在始端加串联电阻匹配,匹配电阻阻值与电路板特征阻抗大小有关.对65 Ω的传输线,选用50 ΩQ串联匹配电阻;

5)CPCI主控模块上的PCI从总线控制信号必须进行上拉,保证在没有设备使用时能保持稳定。这些信号包括:FRAME#,IRDY#,TRDY#,STOP#,DEVSEL#,PERR#,SERR#,L0CK#,INTA#~INTD#。电阻的大小根据设备的负载而定,本设计中电阻值使用典型值8.2 kΩ;

6)为了减少主控模块对底板的影响,除了CLK、REQ#和GNT#信号外,其他PCI信号都要串接10 Ω的终端匹配电阻;

7)要正确设置总线的信号环境。ETX PM的PCI总线信号环境为3.3 V,设计时,将PCI2050BI的P_VCCP连接到3.3 V;S_VCCP联接到背板的VIO上,根据背板VIO电压的设置,可能是3.3 V或5 V,由此完成对信号环境的设置。

1.3 IDE接口

在基于CPCI总线的主控模块上,扩展1个32GBr的宽温电子硬盘,采用IDE接口,作为操作系统或应用程序的存储空间。集成驱动器电路(IDE)适用于任何具有集成(内置)磁盘控制器的驱动器。IDE设备一般包括硬盘、光驱等。因为本设计的CPU主控模块主要应用于恶劣环境下的计算机中,电子盘的工作温度和抗振性要远远好于普通硬盘,所以系统引导时在基于CPCI总线的主控模块上扩展1个32 GB的宽温电子硬盘。ETX模块提供2个IDE通道(PRAMARY IDE和SEC0NDARY IDE),每个通道可以连接2个IDE设备。普通IDE设备的接口一般为40引脚的信号接端口,IDE设备的供电由另外一个单独的电源接口提供。而电子盘的IDE接口一般为44引脚,前40引脚与普通IDE设备接口的定义一致,最后4引脚为电子盘的供电接口,电子硬盘只使用5 V电源。所以本设计中将PRIMARYIDE-44引脚的接口形式置于CPU主控模块上,用于连接电子硬盘作为系统盘使用。SECONDARY IDE通过后走线板接口P2到后走线板上,用于连接普通硬盘或光驱。

2 PCB布局

2.1 元器件封装选择

本设计中所有电子元器件都采用表贴元件,电阻、电容大部分采用0603的封装,并且大量使用电阻排。由于只在表面焊接,不需要钻孔,体积小、功耗小、节省了印制板空间,简化了整版的布局和走线。

2.2 PCB层数选择

本次设计选择制作8层的PCB板。CPCI板卡的总线标准连接器引脚间距为2.0 mm,焊盘孔径为0.6 mm,焊盘直径为1.1 mm,所以两焊盘之间走线空间仅为0.9 mm,线宽为6 mil,线间距6 mil的线单层只能走2根,而CPCI总线连接器单排有5个引脚,即必须走5根线,所以信号层不能少于3层。对于主控模块其主要供电为3.3 V和5 V两种。为了保证信号层和电源层的对称性,同时考虑到此板的复杂性和信号的完整性,将信号层设计为4层,地平面和电平面分别设计为2层。印制板最终的层分布设计依次为:顶层信号层、地层l、内信号层1、3.3 V电层、地层2、内信号层2、5 V电层、底层信号层。

2.3 PCB布线

在CPCI主控模块的设计和布线过程中,严格遵循PCI2.1规范和PICMG2.0R3.0规范,使用符合IEC-1076国际标准的高精度、屏蔽型、针孔式的CPCI连接器。主控模块上的5个CPCI连接器J1,J2,J3,J4,J5中,J1,J2连接器用来连接PCI总线信号,而J3,J4,J5连接器用来扩展系统板的IO信号。设计完成的主控模块可以驱动7个CPCI扩展插槽。

在进行CPCI主控模块PCB布局和布线设计时,其设计要点如下:

1)ETX模块的PCICLK到PCI2050BI主总线的时钟P_CLK信号传输线长度必须为8.7±0.1 inch;

2)为减小CPCI底板总线上时钟之间的偏移(skew),必须将PCI2050BI从总线的S_CLKOUT9信号必须反馈给从总线的S_CLK,PCI2050BI供给扩展槽的9根时钟线(9个S_CLKOUT)与S_CLK必须等长;

3)对PCI2050BI的每个电源引脚提供1个0.1μF的高速去耦电容,并且在布线时尽量靠近PCI2050BI的电源引脚;

4)在主控模块布线时,让PCI2050B尽量靠近Jl和J2连接器,使PCI总线信号到连接器距离尽量的短;

5)根据CPCI规范,PCI总线信号线的10 Ω终端匹配电阻应该设置在信号的连接器引脚的15.2 mm之内,这些总线信号包括AD0~AD31,C/BE0#~C/BE3#,PAR,FRAME#,IRDY#,TRDY#,STOP#,L0CK#,IDSEL,DEVSEL#,PERR#,SERR#和RST#;

6)网口信号和USB信号属于差分信号,在印制板上走线时要应用差分线,对于网口信号TX+和TX-,RX+和RX-要使用差分线对,对于USB信号USB+和USB-要使用差分线对;

7)IDE信号线要尽量等长,以保证传输质量;

8)PCI信号线都要进行阻抗控制,阻抗为65Ω±10%。

3 结束语

CPCI总线是高速同步共享总线,而ETX模块具有强大的性能、高可靠性、灵活的结构、优良的可扩展性以及尺寸小巧等特点,它为6U的基于CPCI总线的主控模块的快速自行研制提供了解决方案。通过深入分析CPCI总线特性,深刻理解高频数字电路设计方法,已成功研制出基于CPCI总线主控模块。经综合测试和实际应用验证表明,该模块已达到了系统要求的性能指标,系统工作稳定,各接口应用正常。

-

基于CPCI总线的CPCI6320视频播放板2023-12-11 627

-

基于CPCI总线CPU主控模块的设计与实现2023-10-18 605

-

厚物科技CPCI机箱CPCI控制器CPCI机架式测控平台HW-30143r2022-04-26 2234

-

基于CPCI总线的四通道总线通讯模块设计2021-06-22 1171

-

如何设计一款基于CPCI总线的通用FPGA信号处理板?2021-05-07 1764

-

探究CPCI总线的PMC载板设计2021-05-05 4770

-

求一款基于CPCI总线的智能A/D,D/A模块设计2021-04-20 1548

-

基于DSP的CPCI总线2018-06-21 1532

-

基于FPGA的CPCI总线多功能通信卡的设计2016-01-14 4606

-

LTC4240实现CPCI总线接口设计2011-09-09 1077

-

CPCI数据总线接口的设计与实现2011-07-17 15936

-

基于CPCI总线的多网口卡设计2010-09-10 2100

-

基于CPCI总线的智能A/D,D/A模块设计2009-11-27 1202

-

cpci总线请教2008-12-29 4720

全部0条评论

快来发表一下你的评论吧 !