川土微电子|隔离电源的辐射抑制设计参考(二)

EMC/EMI设计

描述

VCC 去耦电容

芯片内置的微型变压器的频率高达约 70MHz,短时间内如此大频率的切换,将引起较大的 dv/dt 及di/dt,将产生一定的电磁辐射。 微型变压器的原副边电流路径的环路面积影响着辐射干扰的强弱,电流环路越大,辐射越强。 PCB 布线时需要最大程度地缩小电流路径的环路面积。

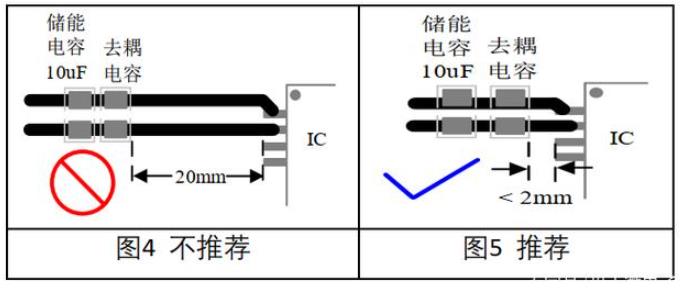

输入 VCC 及输出侧 VISO 的储能电容及耦合电容位置放尽可能摆放在靠近芯片的管脚位置, 以减少环路面积和 PCB 走线的寄生电感, 一般应控制在 2mm 以内。 储能电容 10μ F 应放在最外侧,去耦电容要放在靠近芯片的位置。 如下图 4 和图 5 所示。

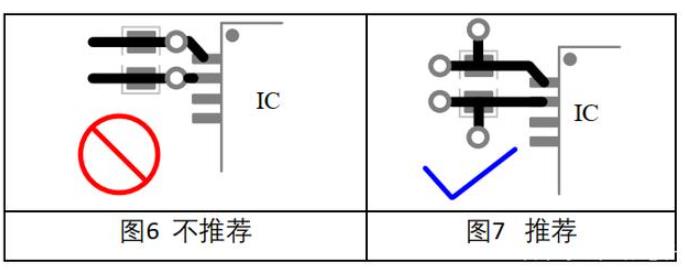

当需要在供电电源线和地线中放置过孔,过孔的摆放位置在电容相对于芯片管脚的外侧,而非放置在电容和芯片之间,以减少过孔寄生电感的影响,如下图 6 和图 7 所示。如果 PCB 空间允许应多放置几个过孔,这样过孔的寄生电感相当于并联,进一步减少过孔的寄生电感带来的影响。

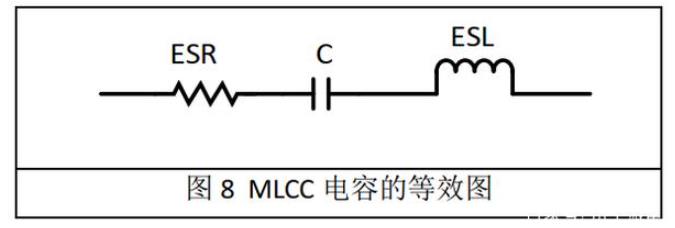

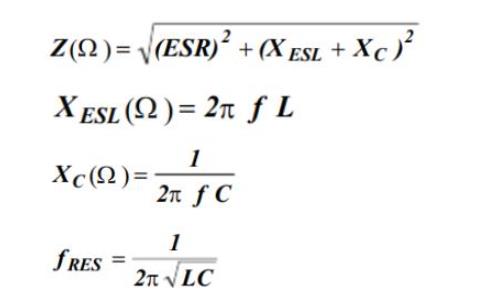

变压器的频率高达 70MHz,芯片在开关期间需要初次级供电端 VCC对 GNDA 以及 VISO 对 GNDB 需要放置容量约 10μ F 储能电容来提供开关期间的瞬间大电流。此外, 需要合适的去耦电容来滤除高频噪声。 去耦电容一般选用 MLCC 多层陶瓷电容,但陶瓷电容存在着寄生电感,频率越高,越不能忽略 ESL 的影响。 MLCC电容的等效图如下所示。

ESR: 电容器电介质或者电极损耗(高频)产生的寄生电阻;

ESL: 电容的分布电感以及 PCB 走线的寄生电感。

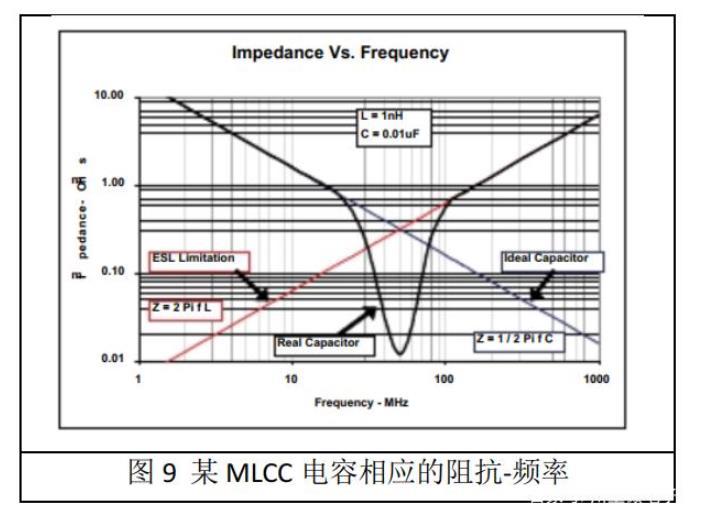

某 10nF/10V MLCC 电容相应的阻抗-频率如图 9 所示:

从上图可以看到,当频率较低时,电容的感抗远小于容抗,表现为容抗特性,且阻抗值较大;当超过自振频率时,电容的感抗大于容抗,表现为感抗特性,阻抗随着频率的增加而增加。因此,在选择器件时, 去耦电容的自振频率应在 70MHz 及多倍频附近。 也可以用几个不同容量的去耦电容,这样可以覆盖更宽的频率。

从上图可以看到,当频率较低时,电容的感抗远小于容抗,表现为容抗特性,且阻抗值较大;当超过自振频率时,电容的感抗大于容抗,表现为感抗特性,阻抗随着频率的增加而增加。因此,在选择器件时, 去耦电容的自振频率应在 70MHz 及多倍频附近。 也可以用几个不同容量的去耦电容,这样可以覆盖更宽的频率。

从上图可以看到,当频率较低时,电容的感抗远小于容抗,表现为容抗特性,且阻抗值较大;当超过自振频率时,电容的感抗大于容抗,表现为感抗特性,阻抗随着频率的增加而增加。因此,在选择器件时,去耦电容的自振频率应在70MHz及多倍频附近。也可以用几个不同容量的去耦电容,这样可以覆盖更宽的频率。

除了上述利用分立器件外,也可以通过PCB的VCC平面层与地层之间拼接电容,形成VCC去耦电容。PCB拼接电容的分布电感较小,高频特性优于分立器件,可以覆盖相对较宽的频率。PCB拼接电容于PCB板上的分立器件的电容共同起到去耦作用。例如PCB第一层GNDA和第二层VCC之间的厚度为0.2mm,VCC和GNDA的交叠面积为0.0021m2。

按照上述计算方式,得到拼接电容约为C=4.5*8.544*0.0021/0.0002pF,=403.7pF。

-

川土微电子推出CA-IS23101WH高精度隔离电流传感器2025-08-20 1186

-

川土微电子与国创中心达成战略合作2025-07-17 827

-

川土微电子股份有限公司创立大会顺利召开2025-06-26 1019

-

川土微电子发布CA-IS3212单通道隔离式栅极驱动器2025-01-10 1548

-

川土微电子推出CA-IS3211SCWG单通道隔离栅极驱动器2024-11-27 1958

-

川土微电子发布CA-IF1021Lx-Q1 LIN收发器2023-12-12 1993

-

川土微电子推出高性能1000M数字隔离器CA-IS303xT2023-10-27 2108

-

继比亚迪之后,吉利入股川土微电子2023-09-19 2032

-

川土微电子车规级CA-IS3221/3222隔离栅极驱动器面市2023-04-24 3869

-

川土微电子CA-IS3062W荣获2022中国IC设计成就奖之“年度最佳隔离器”2022-08-23 2217

-

川土微电子CA-IS1300用于电流检测的隔离运放新品上市2022-02-15 4306

-

川土微隔离电源的辐射抑制设计参考(一)2021-12-31 3847

-

国产首发:上海川土微电子数字接口电源数字隔离芯片模拟芯片领导者2021-11-08 1347

全部0条评论

快来发表一下你的评论吧 !