AD6659混合信号双通道中频接收机

电子常识

描述

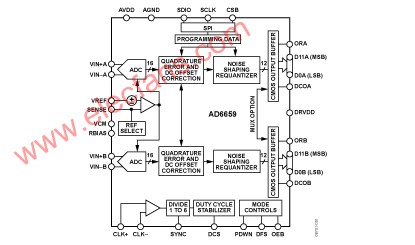

AD6659是一款混合信号双通道中频接收机,支持需要两条接收机信号路径的无线电拓扑结构,例如主信号/分集通道或直接变频。该通信系统处理器由两个高能性模数转换器(ADC)和噪声整形再量化器(NSR)数字模块组成。AD6659专为支持各种需要高动态范围性能和小尺寸的通信应用而设计。

高动态范围ADC内核采用多级、差分流水线架构,并集成了输出纠错逻辑。各ADC的差分流水线第一级采用宽带宽开关电容采样网络。集成基准电压源可简化设计。

各ADC输出从内部连接至NSR模块。集成NSR电路可以改善奈奎斯特区域内的小频段SNR使能NSR特性后,ADC输出经过处理,增强了AD6659在奈奎斯特带宽有限区域内的SNR性能,同时可以保持12位输出分辨率。NSR模块通过编程可提供采样时钟20%的带宽。例如,采样时钟速率为80 MSPS时,AD6659对9.7 MHz AIN下的16 MHz带宽最高可实现81.5 dBFS SNR。

禁用NSR模块后,ADC数据直接提供至输出,输出分辨率为12位。在此模式下,AD6659对整个奈奎斯特带宽最高可实现72 dBFS SNR。

经过数字处理,输出数据路由至两个支持1.8 V或3.3 V CMOS电平的12位输出端口。AD6659接收机可对宽频谱的中频频率进行数字化处理。每个接收机均设计成可同时接收主通道和分集通道。与传统模拟技术或集成度较低的数字方法相比,这种中频采样架构大大降低了器件成本和复杂性。

AD6659还可选用集成直流失调校正和正交误差校正(QEC)模块,用于校正两个通道之间的增益和相位失配。在直接变频接收机等复数信号处理应用中,此功能模块可发挥重要作用。

该ADC内置多种功能特性,可使器件的灵活性达到最佳、系统成本最低,例如可编程时钟与数据对准、生成可编程数字测试码等。可获得的数字测试码包括内置固定码和伪随机码,以及通过串行端口接口(SPI)输入的用户自定义测试码。

采用一个差分时钟输入来控制所有内部转换周期。可选的占空比稳定器(DCS)用来补偿较大的时钟占空比波动,同时保持出色的ADC总体性能。

数字输出数据格式为偏移二进制、格雷码或二进制补码。每个ADC通道均有一个数据输出时钟(DCO),用来确保接收逻辑具有正确的锁存时序。该器件支持1.8 V和3.3 V两种CMOS电平,输出数据可以在单条输出总线上多路复用。

AD6659采用64引脚LFCSP封装,符合RoHS标准,额定温度范围为−40°C至+85°C工业温度范围。

特性

- 每通道12位、80 MSPS输出数据速率

- 1.8 V 模拟电源供电(AVDD)

- 1.8 V 至3.3 V输出电源(DRVDD)

- 集成噪声整形再量化器(NSR)

- 集成正交纠错(QEC)

-

使能NSR时的性能

16 MHz频带内信噪比(SNR) = 81 dBFS,80 MSPS下最高30 MHz

-

禁用NSR后的性能

信噪比(SNR) = 72 dBFS,80 MSPS下最高70 MHz

无杂散动态范围(SFDR) = 90 dBc,80 MSPS下最高70 MHz输入 - 低功耗:每通道98 mW (80 MSPS)

- 差分输入、700 MHz带宽

- 片内基准电压源和采样保持电路

- 2 V峰峰值差分模拟输入

- 串行端口控制选项

应用

- 通信

- 分集无线电系统

-

多模式数字接收机

3G, W-CDMA, LTE, CDMA2000, TD-SCDMA, MC-GSM - I/Q 解调系统

- 智能天线系统

- 电池供电仪表

- 通用软件无线电

-

AD6650分集中频至基带GSM/EDGE窄带接收机技术手册2025-04-28 787

-

为什么接收机中频不能落入调谐范围内?2023-10-19 1214

-

CN0140 高性能、双通道IF采样接收机2021-06-06 1082

-

AN-1589:高性能双通道中频采样接收机2021-05-26 735

-

AD6659:双中频接收器过时数据表2021-05-25 669

-

AD6649: 中频分集接收机2021-03-21 918

-

AD6643: 双通道中频接收机2021-03-20 811

-

AD6643双通道中频接收机的性能及应用2019-06-20 3821

-

80MHz带宽双通道中频接收机2017-06-01 1673

-

analog AD6659 产品手册PDF下载2012-09-19 1154

-

双通道接收机的设计2011-12-14 601

-

高性能、双通道IF采样接收机2011-03-31 578

-

中频采样多模式数字接收机的设计与实现2009-08-28 967

-

双通道接收机校正系统的设计与实现2009-08-26 699

全部0条评论

快来发表一下你的评论吧 !