晶体管的3、2、1纳米制程中谁将胜出,有何发展趋势

今日头条

描述

来源:旺材芯片

随着5G、人工智能、元宇宙等新兴科技产业快速崛起,发展低功耗、小尺寸、异质整合及超高运算速度的芯片架构技术,已成为全球半导体制造业者最重要的产业趋势与决胜关键。而跨过5 纳米世代后,未来芯片制程又将迎来哪些白热化的竞争与发展趋势?

在芯片的先进制程竞赛上,自英特尔(INTEL)于2012 年在22 纳米芯片引入创新立体架构的「鳍式晶体管」(FinFET)之后,全球半导体业者都在此基础上进行研发。目前最先进的5 纳米制程,即是采用FinFET 架构来制作。该技术已由台积电(TSMC)拔得头筹,于2020 年成功投入量产。

然而,当未来制程要再微缩至 3 纳米时,FinFET却会产生电流控制漏电的物理极限问题。事实上,三星(Samsung )已于近期赶在台积电之前,发布了最新一代采用环绕式闸极场效晶体管(Gate-All-Around FET ;GAAFET )的全新架构3纳米制程。究竟在新一轮芯片制程的巅峰决战中,谁能最终胜出仍待观察。

由于GAAFET 的芯片架构相比于FinFET,能以更小的体积实现更好的功耗表现,实际可缩减45% 芯片面积、同时降低50% 的能耗。台积电欲持续以FinFET 与三星GAAFET 在3 纳米先进制程领域决战,2022 年绝对是决定胜负至为关键的一年。

而对于众所瞩目的下一代2 纳米制程,台积电也已公开表示亦将采用GAAFET 架构,并藉由导入低维度高电子迁移率材料以及特殊绝缘层材料等,来强化其在先进制程的竞争优势。GAAFET架构俨然已成为下一世代延续莫尔定律(Moore‘s Law )发展的最佳选项。

01、浅谈鳍式芯片架构原理与发展

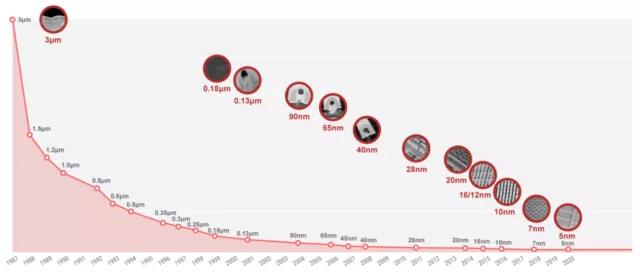

随着摩尔定律(Moore’s Law)的发展,从微米(μm)技术节点演进至现今的5 纳米技术节点(图一),以及预计将于2022 年量产的3 纳米技术节点[1],技术节点的数值越小,晶体管密度越高。

过去在平面晶体管(Planar FET)技术发展中,有两项重要的技术突破:一是90 纳米技术节点开始量产的应变硅(strained Si),可提升硅通道的迁移率,增加电流;二是高介电常数/金属闸极(high-k/metal gate),介电层的k 值越大,氧化层电容(Cox)越大,晶体管电流就越大,且可在相同的等效氧化层厚度(equivalent oxide thickness, EOT)下,以较大的物理厚度来降低漏电流。

▲图一、台积电的制程技术节点[1]。

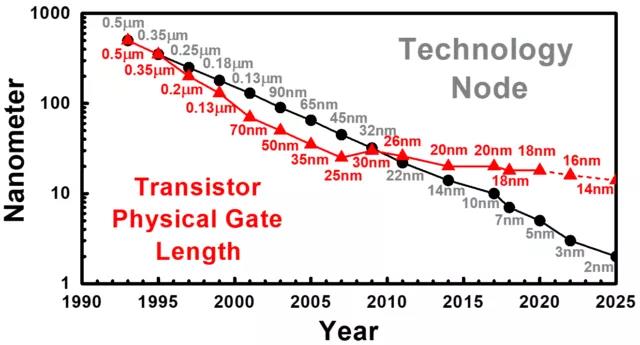

随着传统的半导体尺寸微缩,晶体管的闸极长度(gate length)也逐渐减小。实际上,闸极长度和技术节点的数值是不相等的,且在22纳米技术节点以后,闸极长度会大于技术节点的数值(图二)。随着晶体管的尺寸越来越小,传统的微缩方式逐渐接近其物理极限,单纯依循摩尔定律的尺寸微缩,已无法提供如预期般效能的成长。自22 纳米技术节点(Intel)及16 纳米技术节点(台积电)开始,由胡正明院士团队提出的鳍式晶体管(FinFET)开始被业界所采用,三维晶体管也成为现今先进半导体的主流结构。

▲ 图二、约略估计晶体管技术节点(Technology Node )与闸极长度(Gate Length )。图片来源:台大电子工程学研究所刘致为教授研究团队

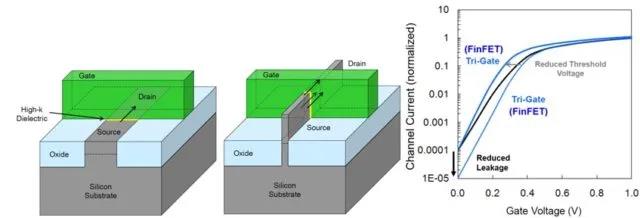

晶体管由传统的平面式(图三a)走向三维的立体结构(图三b),因为三面的闸极结构(Tri-Gate)与鱼鳍十分相似,所以称为鳍式晶体管。鳍式晶体管具有比平面晶体管更大的等效宽度(effective width),可提高元件之电流密度,且其三维之结构可增加通道控制能力,抑制短通道效应(short channel effect)。

三维的鳍式晶体管结构可降低次临界摆幅(subthreshold swing, SS)与工作电压,减少晶体管损耗功率(图三c)。鳍式晶体管已从16 纳米、10 纳米、7 纳米、5 纳米、3 纳米共发展了五代技术节点,为目前的主流元件结构。

▲ 图三、(a)平面晶体管示意图(b)鳍式晶体管示意图(c)电流–电压关系图。[2]

02、鳍式3 纳米台积电今年量产未来将采用闸极环绕式架构

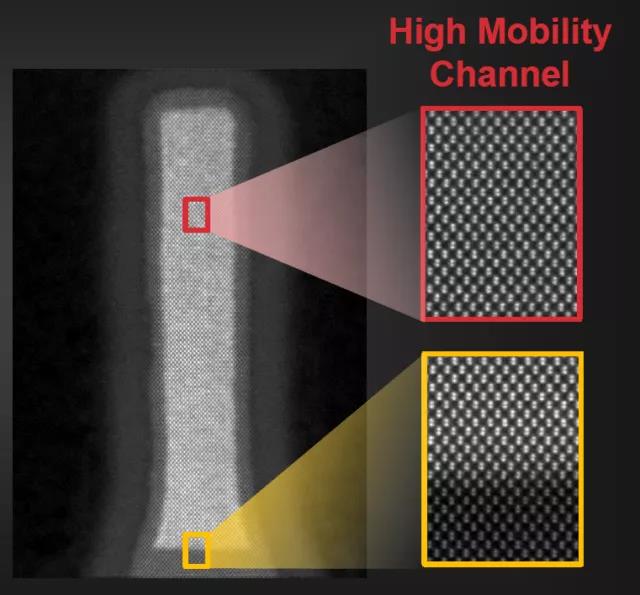

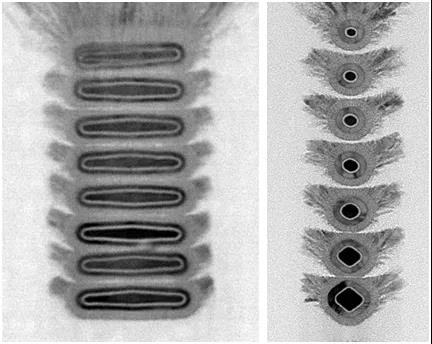

台积电于2019 年国际电子元件会议(International Electron Devices Meeting, IEDM)宣布于5 纳米技术节点量产拥有高迁移率通道(high mobility channel)之鳍式晶体管[3]。使用高迁移率通道,犹如驾驶跑车,速度更快,使晶体管的效能更佳。图四[4] 为台积电于2021 年国际固态电路研讨会(International Solid-State Circuits Conference, ISSCC)中所展示的高迁移率通道鳍式晶体管,由图中可看出高迁移率通道与底部的硅材料具有明显的对比,且皆有清楚的哑铃状结构(dumbbell)。

台积电预计于2022 下半年开始量产3 纳米技术节点的全世代制程晶体管,与5 纳米技术节点相比,3 纳米技术节点的逻辑密度将增加约70%,在相同功耗下速度提升10-15%,或者在相同速度下功耗降低25-30% [1]。

▲ 图四、台积电 5 纳米技术节点的高迁移率通道鳍式晶体管 [4] 。© IEEE

为了进一步增加通道的控制能力与维持短通道效应的抑制,必须改变晶体管之架构。三星、台积电、Intel 已宣布在3纳米技术节点(Samsung )和2纳米技术节点(TSMC 、Intel 20A )将采用闸极环绕式(Gate-All-Around, GAA )的纳米片(nanosheet )结构。

03、闸极环绕式晶体管架构原理

闸极环绕式晶体管具有比鳍式晶体管更好的闸极控制能力,在先进技术节点将取代鳍式晶体管结构,晶体管密度也将持续提升。使用GAA 晶体管结构,犹如使用强力水龙头,滴水不漏,使晶体管有效降低漏电流,更加节能省电。

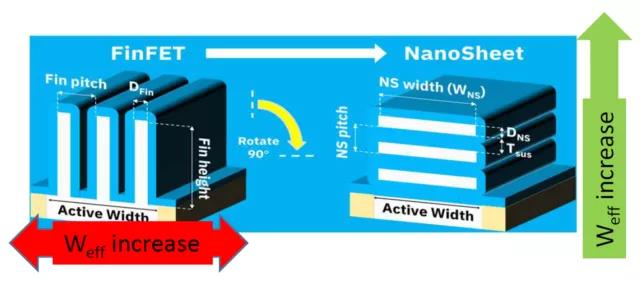

为了增加晶体管的驱动电流,采用通道堆叠(channel stacking)的方法,在垂直方向增加通道数目,犹如建构双层高架桥,在相同占地面积下,可负载更多车流量,使晶体管拥有更高电流并增加晶体管密度,有效提升元件效能。图五[5] 为垂直堆叠纳米片(stacked nanosheets)的结构,可视作将FinFET 旋转90 度并进行垂直堆叠,形成四面环绕式的闸极结构。

有别于FinFET 的通道宽度(D Fin)是由微影制程(Lithography)所限制,stacked nanosheets 的通道厚度(D NS)可藉由磊晶(epitaxy)来决定,因此可精准控制厚度。除此之外,stacked nanosheets 可往垂直方向增加通道层数,在相同的占地面积(footprint)下具有更大的等效宽度(effective width, W eff),提供更大的电流以提升晶体管效能。

磊晶(epitaxy)技术除了可精准决定stacked nanosheets 的通道厚度外,也可以控制通道与通道之间的距离(suspension thickness, T sus),不会像FinFET 增加占地面积,且可以透过降低T sus的方式来减少元件的寄生电容(parasitic capacitance)。

▲ 图五、鳍式晶体管(FinFET)与垂直堆叠纳米片(Stacked nanosheets)之比较 [5] 。© IEEE

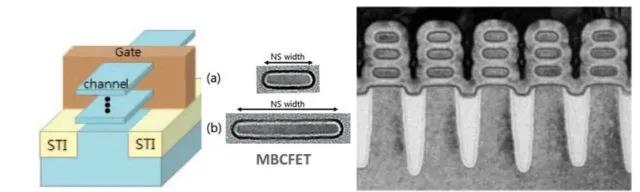

三星率先在2018 IEDM国际会议上宣布以Multi-Bridge-Channel FET (MBCFET )之GAA 晶体管作为3纳米技术节点之晶体管结构(图六 a,b )[6] ,其中提到MBCFET采用90%的FinFET制程,与现今业界之FinFET制程具有良好的相容性。

MBCFET 顾名思义,结构与多层桥梁相似,实际上和前述的stacked nanosheets 是相同的结构。与FinFET 相比,MBCFET 具有更好的闸极控制,在相同的面积下,也有更大的等效宽度以提供更大的驱动电流,并可依照不同的应用来调整通道宽度,提高电路设计之弹性。

另一方面,IBM 的2 纳米技术节点提出三层垂直堆叠的stacked nanosheets (图六c)[5],其通道宽度为40 纳米、通道高度为5 纳米、闸极长度为12 纳米,并采用底部介电层绝缘(bottom dielectric isolation, BDI),能有效减少漏电流,降低芯片功耗。与7 纳米制程技术相比,预计提升45% 的性能或降低75% 的耗能[7]。

▲ 图六、(a, b)三星3纳米技术节点之MBCFET [6] © IEEE (c)IBM 2纳米技术节点之三层垂直堆叠通道晶体管[5] 。© IEEE

04、高层数通道堆叠的GAA 晶体管将成未来主流结构

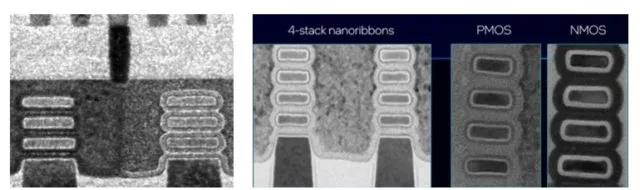

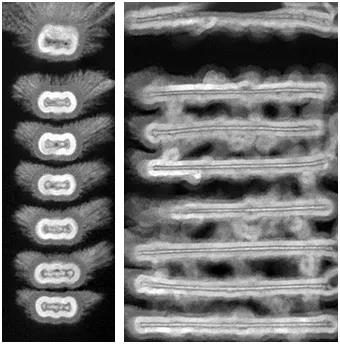

台积电在2021 ISSCC 国际会议上展示三层垂直堆叠的stacked nanosheets 作为2 纳米技术节点之晶体管结构(图七a),可提供更佳的性能及更低的次临界摆幅[4]。Intel 则宣布2024 年将以RibbonFET(垂直堆叠四层的nanoribbons,也与stacked nanosheets 结构相似)作为20A 技术节点之结构(图七b)[8],并将于2025 年以优化的RibbonFET 作为18A 技术节点之结构。

由业界趋势可见,高层数通道堆叠的GAA晶体管为未来晶体管之主流结构。在2020 年超大型积体电路技术研讨会(Symposium on VLSI Technology, VLSI)中,法国半导体研究机构CEA-Leti 发表了七层的Si GAA nanosheets 晶体管(图八)[9]。

▲ 图七、(a)台积电2纳米技术节点之三层垂直堆叠通道晶体管 [4] © IEEE(b)Intel 20A技术节点之四层垂直堆叠通道晶体管(RibbonFET )[8] 。

▲图八、法国半导体研究机构 CEA-Leti发表之七层垂直堆叠硅通道晶体管[9] 。© IEEE

05、由硅到锗硅等晶体管通道材料发展

目前已发表的GAA晶体管,通道材料大部分以硅(Si )为主,为了增加电路的运作速度,必须提升晶体管的驱动电流(垂直堆叠通道电流的总和),除了往垂直方向增加通道数目外,采用高载子迁移率(mobility )的材料作为晶体管通道可进一步提高晶体管的驱动电流,例如锗(Ge )、锗硅(GeSi )、锗锡(GeSn )等新四族材料,具有优于硅的电子及电洞迁移率,并且与现今业界的硅半导体制程技术有良好的相容性。

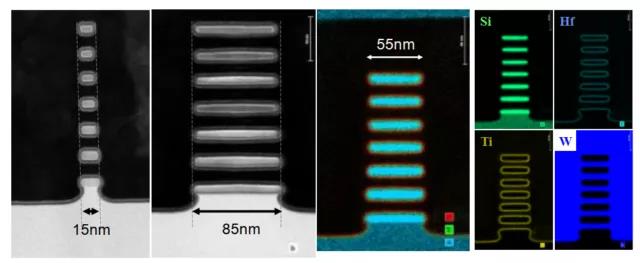

台大电子工程学研究所刘致为教授研究团队,于2021 VLSI国际会议上发表了八层锗硅N型GAA晶体管(8 stacked Ge 0.75 Si 0.25 nanosheets )(图九左)[10],拥有极高的通道均匀性。为进一步提高元件的驱动电流,将锗硅通道的锗浓度提升至95%,以提高通道之电子迁移率,并成功展示了世界首颗高效能七层锗硅N 型GAA 晶体管(7 stacked Ge 0.95 Si 0.05 nanowires)(图九右)[10],此研究成果也获国际顶尖期刊Nature Electronics 报导于Research Highlight [11]。

由此可见,高层数堆叠之高迁移率通道GAA 晶体管为未来半导体技术节点的一大趋势。其中磊晶(epitaxy )与蚀刻(etching )为高层数堆叠通道GAA晶体管最重要的两大制程技术,藉由两者的互相优化才能成功制备高效能晶体管。目前台大是业界以外,唯一能研发多层堆叠通道GAA晶体管的大学,也成为学界与业界接轨的重要桥梁。

▲图九、本研究团队发表之(左)八层 GeSi nanosheets [10](右)七层 GeSi nanowires [10] 。© IEEE

P 型晶体管方面,因为压缩应变的锗锡(GeSn)材料拥有比纯锗和硅更高的电洞迁移率,可增加元件之驱动电流,成为通道材料的潜力之一。然而因锗锡材料之能隙较小,元件具有较大之截止状态漏电流(I OFF)以及较小之开关电流比(I ON /I OFF),将造成元件功率耗损过大。此问题可藉由降低通道厚度来改善,随着通道厚度变薄,受量子局限效应(quantum confinement effect)影响使I ON /I OFF随之上升,因闸极控制能力增强使次临界摆幅(SS)下降。

然而当通道厚度小于5nm 时因表面粗糙散射(surface roughness scattering)的影响,导致载子迁移率降低,故需搭配高堆叠、高载子迁移率之锗锡通道,维持元件之驱动电流。因此研究团队在2021 IEDM 国际会议上发表七层与八层堆叠锗锡极薄通道P 型晶体管(7 stacked and 8 stacked Ge 0.9 Sn 0.1 ultrathin bodies)(图十) [12],以锗锡材料作为高迁移率通道(high mobility channel),优化磊晶(epitaxy)与高蚀刻选择比等向性干蚀刻(highly selective isotropic dry etching, HiSIDE)制程,制备出厚度为3 纳米之极薄通道,有效降低元件之漏电流,且I ON /I OFF为锗/锗锡三维晶体管之世界纪录,此篇论文也获得2021 IEDM 最佳学生论文奖(Best Student Paper Award)。

▲图十、本研究团队发表之(左)七层与(右)八层锗锡极薄通道[12] 。© IEEE

06、台积电、三星及英特尔下一步决战GAAFET

综上所述,高层数(highly stacked )、高迁移率(high mobility ),以及极薄通道(ultrathin bodies )之GAA晶体管将能使半导体芯片效能更高、更省电,进而使先进半导体科技不断进步,为人类带来更好的生活。

接下来,先进制程架构将从FinFET 转进GAAFET,台积电、三星及英特尔在未来5 纳米以下的GAAFET 技术发展上势必也将展开一场白热化的竞赛。然而,值得注意的是,欲在未来半导体霸权时代取得技术领先地位,除了晶圆制造技术上须掌握优势外,系统封装整合技术也是半导体产业重要的发展方向。

而在GAAFET 世代之后,是否会有更为创新、可延续莫尔定律发展的新型晶体管结构出现?就让我们拭目以待。

审核编辑:符乾江

-

电子行业人士带你入行之纳米制程小白篇2016-06-29 0

-

最精尖的晶体管制程从14nm缩减到了1nm2016-10-08 0

-

【AD新闻】英特尔解读全球晶体管密度最高的制程工艺2017-09-22 0

-

集成电路的发展趋势与设计挑战2018-05-11 0

-

晶体管的发展历程概述2019-07-23 0

-

芯片里面100多亿晶体管是如何实现的2020-07-07 0

-

尔必达40纳米制程正式对战美光2010-01-08 648

-

IBM展示领先芯片技术,3D晶体管碳纳米管来袭2013-02-20 7997

-

张忠谋:3纳米制程两年内研发成功,2纳米制程将于2025面世2018-06-15 4875

-

中芯国际的14纳米制程将于2019年量产 未来首个14纳米制程客户将来自手机芯片产业2019-01-29 7601

-

7纳米制程竞争激烈 台积电3月领先量产2019-02-14 2236

-

纳米制程是什么?2019-10-14 15274

-

M2芯片采用了增强的第二代5纳米制程技术2022-06-07 3385

-

台积电领跑半导体市场:2纳米制程领先行业,3纳米产能飙升2024-02-21 792

全部0条评论

快来发表一下你的评论吧 !