薄膜MLCC的技术报告

薄膜MLCC的技术报告

制造/封装

描述

本文讨论了传统MLCC技术的最新技术,并将该技术与潜在的MLCC薄膜制造技术进行了比较,讨论了MLCC制造、相关限制、潜在制造技术和设计理念方面的薄膜技术的实用性。同时还考虑了电子行业的总体趋势的影响、MLCC形状因子的预期演变以及薄膜技术作为一种潜在可行的未来MLCC制造方法的一般器件要求。

由于传统MLCC工艺的基本限制,结合薄层薄粒钛酸钡铁电介质,MLCC技术可能会开始滞后于“MLCC曲线”,薄膜技术长期以来一直被认为是MLCC的下一个技术,然而,薄膜技术在制造高层计数器件方面有基本的局限性。此外,薄膜高K介质与厚薄膜基高K介质相同的K还原相同,因此,需要考虑新的电容器结构来最大化最大的体积电容的VE,使高VE能够实现,而不受多层薄膜工艺的相关成本和限制。这些结构很可能包括浸渍一个复杂的多孔结构。此外,很可能会使用混合浸渍和阳极化过程来实现。

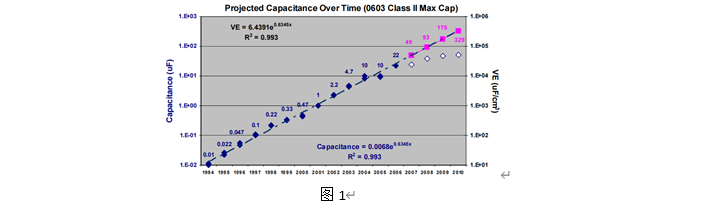

图1显示了自ca以来0603MLCC的电容和VE的增加,这种增加很好地符合一个关系,表明对于0603外壳尺寸,最大可用电容和VE随着时间的推移以超过摩尔定律的速度增加,大约每13到14个月增加一倍(摩尔定律为大约18个月)。为了实现这一令人印象深刻的速度,MLCC的所有设计参数都随着时间的推移而变化。

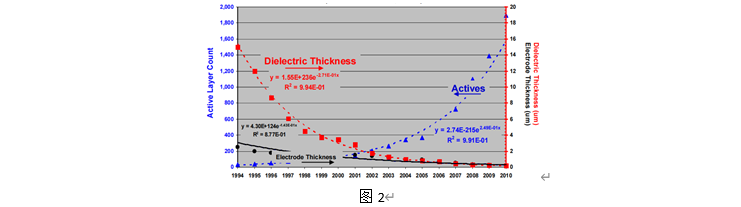

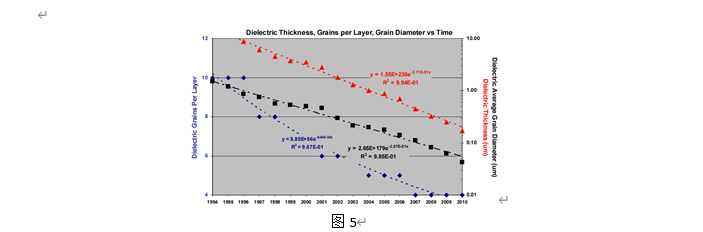

图2表明,对MLCC VE和电容增加速率的最大贡献是减少介电厚度和增加有效计数的组合,随着介电介质厚度在~0.8µm以下明显下降,这一趋势是否会继续下去还值得怀疑,造成这种怀疑的普遍原因是,所使用的介电介质需要在每个介电层的厚度上有几个晶粒,以便使这些基于batio3的2类介质适当可靠,虽然每层晶粒数量也随着时间的推移而减少,但除非引入介电材料的突破技术,每层介电晶粒数量可能不会低于~4。考虑到这一点,预计的介电晶粒尺寸将需要显著减少,以实现如图5所示的预计的介电厚度目标。

此外,这些计算和预测是通过假设K没有,也不会随着时间(或介电厚度)发生明显的变化而进行的,可以开发替代材料,如弛豫介质,尽管它们通常含铅,并且大多数主要的MLCC制造商由于各种法律和环境监管原因而避免。从以上讨论可以明显看出,传统的MLCC材料和制造技术将很难跟上“MLCC曲线”的步伐。介电厚度小于0.2µm的MLCC,结合1800多个活性层,产率高,可靠性好,成本有竞争力,采用传统材料和MLCC制造技术制造,难以理解,如果传统的MLCC材料和制造技术开始滞后于“MLCC曲线”,那么颠覆性技术的机会就会出现,多层薄膜技术长期以来一直被认为是MLCC的下一个技术,取代传统的MLCC技术来制造高VE,然而,这种预期还有待实现,薄膜工艺对多层结构有相关的基本限制。因此,有必要开发一种与传统方法一样利用可移动衬底的制造工艺。

-

TDK适用于谐振电路的MLCC电容器解决方案2025-09-05 58728

-

Molex薄膜电池的技术原理是什么?-赫联电子2025-07-15 1120

-

AMEYA360:汽车市场高端MLCC需求旺盛#MLCCjf_81091981 2023-04-12

-

片式元件新宠——超微型超高精度微波MLCC2012-11-08 2820

-

MLCC外选2012-12-29 2457

-

手机对MLCC市场需求2013-01-07 3879

-

MLCC种类及结构2013-01-23 7437

-

消费电子市场需求旺盛 MLCC前景看好2014-07-14 3167

-

MLCC2016-03-11 3464

-

电容界的龙争虎斗:钽电容 VS MLCC2016-08-19 11565

-

薄膜无源器件在射频微波电路中的应用2019-07-10 2036

-

薄膜电容的内部构造2020-07-01 4216

-

如何选择合适的MLCC?有哪些要求?2021-04-21 2854

-

MLCC行业:下游需求趋势长期向好,高端产品国产替代空间广阔2023-03-30 2040

-

有关于MLCC(多层陶瓷电容)替代Film Cap (薄膜电容)的那些事2023-12-04 4388

全部0条评论

快来发表一下你的评论吧 !