PCIE一致性测试过程的详细介绍

电子说

描述

作者:一博科技高速先生自媒体成员 黄刚

PCIE信号的一致性测试从来都是业界的一个重点和难点,本期借着一个电脑主板的debug案例,高速先生向大家介绍下PCIE一致性测试的过程!

相信不少酷爱PCB设计(吃ji游戏)的粉丝们都知道一部好的电脑的重要性,再说得细一点,就是主板和显卡的重要性。近段时间国内某家主板的自研客户听说了我们有PCIE的测试夹具和高端的示波器后,就联系上了高速先生,希望我们帮他们定位一下他们的问题!

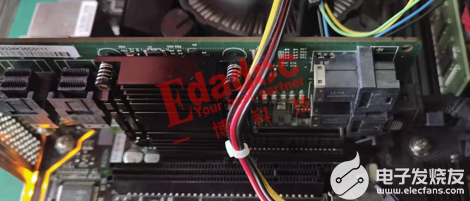

上面说过了,客户是一家自研电脑主板的客户,本次的问题是他们自己研发的主板在测试外面专用的显卡时,发现PCIE信号在运行到3.0(8Gbps)的时候就不太稳定,经常会出现降到2.0(5Gbps)的情况,主板和专用显卡的连接就像下面这样。

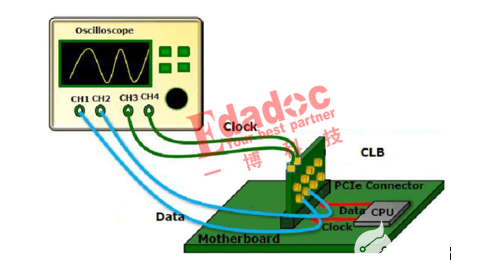

由于线卡是专用的显卡,我们高速先生主要还是怀疑是客户自研的主板这边的问题,于是我们就需要对主板进行测试,要进行什么测试呢?最好的测试当然是PCIE信号的一致性的测试,它通过PCIE标准的CLB(Compliance Load Board)来替代显卡,从而对主板进行测试,其中主板的TX信号可以通过CLB连接到示波器来进行眼图的测试,验证下眼图的质量。

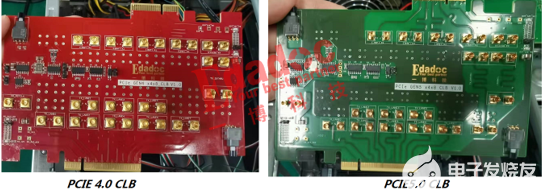

在选用哪一款CLB的时候,高速先生一度陷入了选择困难,因为高速先生实验室里拥有从3.0到5.0的CLB夹具,为了更好的表征出主板的性能,我们最终选择了最高配置的5.0的CLB夹具。

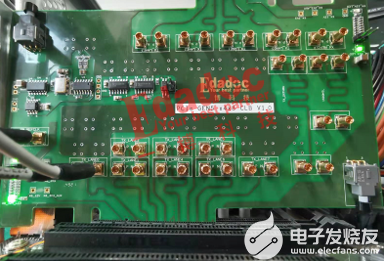

然后我们就使用5.0的CLB夹具插到主板的PCIE插槽里面进行测试,然后把PCIE的REF时钟和其中一个通道的PCIE信号通过高速线缆连接到示波器去测试,搭建的场景如下所示:

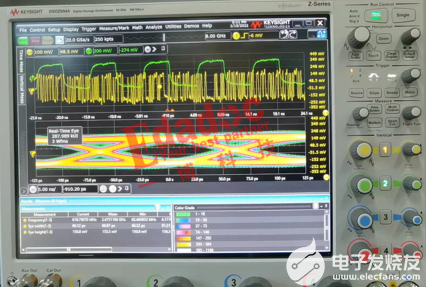

一开始我们先看看在主板发送芯片没有加重均衡的情况下,到底眼图的质量是怎么样的?通过我们示波器的眼图显示,在PCIE3.0(8Gbps)下眼图质量比较差,如下所示:

也这印证了客户的功能测试,在3.0速率下不稳定,会降到2.0的结果,同时也说明了客户自研的主板的确设计上还是有待改进。

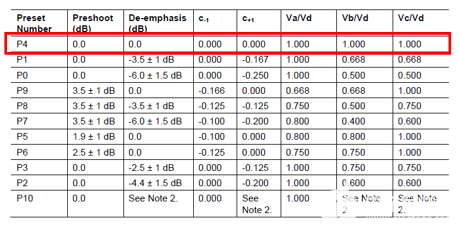

大家是不是以为这样就完了?当然不是,根据PCIE3.0的协议,规定了芯片需要具备多达10种加重均衡的参数可以去调节和切换,如下所示,其实上面我们测试的是芯片没有加重均衡情况下的眼图结果,也就是P4这一阶的芯片参数。

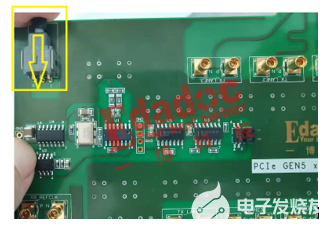

一款合格的CLB夹具是可以控制主板的芯片来调节不同的输出参数的,具体的调节方法也非常的简单,只需要轻轻的按一下CLB夹具上的这个按钮!

我们都遍历了一下不同芯片输出的均衡参数,由于篇幅关系,这个就不一一列出每种参数的眼图结果,我们直接给出最好的一种参数下的眼图结果,也就是在P7下,我们的眼图能够重新变好,达到150多mV的眼高!

后面我们让客户自己去按照P7的均衡参数去配置它的主板芯片,客户就惊喜的发现他们主板接上专用的显卡后能稳定运行在PCIE3.0的速率了,本文也顺利收尾了!

审核编辑:符乾江

-

jf_02380735

2024-07-18

0 回复 举报1、文章里的CLB板子,不是PCI-SIG官方的板子,这个是否有问题?2、要测试主板TX眼图,除了插入CLB板子,最关键的是怎么让芯片进入polling.compliance模式,让芯片的TX发出CTS测试pattern;3、CLB上的按钮按一下能切换芯片TX EQ参数的原因是按下之后CLB的会发一个100MHz的时钟脉冲给RX,用一个信号发生器的输出接到芯片RX也能实现同样的效果。 收起回复

jf_02380735

2024-07-18

0 回复 举报1、文章里的CLB板子,不是PCI-SIG官方的板子,这个是否有问题?2、要测试主板TX眼图,除了插入CLB板子,最关键的是怎么让芯片进入polling.compliance模式,让芯片的TX发出CTS测试pattern;3、CLB上的按钮按一下能切换芯片TX EQ参数的原因是按下之后CLB的会发一个100MHz的时钟脉冲给RX,用一个信号发生器的输出接到芯片RX也能实现同样的效果。 收起回复

-

LIN一致性测试规范2.12024-08-15 932

-

QSFP一致性测试的专业测试设备2024-03-14 1667

-

深入理解数据备份的关键原则:应用一致性与崩溃一致性的区别2024-03-11 2331

-

DDR一致性测试的操作步骤2024-02-01 4431

-

MIPI一致性测试2019-09-26 3667

-

LTE基站一致性测试的类别2019-06-06 2006

-

CAN一致性测试—容错性测试2018-11-22 3741

-

EMI一致性测试调试方法2017-09-12 1069

-

一致性测试2017-07-14 3594

-

TD-LTE终端一致性测试标准化技术规范2013-01-09 5495

-

RFID协议一致性测试系统设计(二)2012-03-28 2078

-

DMR空中接口协议一致性测试技术2011-12-22 1424

-

TTCN在TD-SCDMA终端RRM一致性测试系统中的应用2010-09-15 1669

-

PCIe 2.0/PCIe 3.0验证、调试和一致性测试解决2010-06-29 1272

全部0条评论

快来发表一下你的评论吧 !