AXI4-FULL总线多通道数据传输,合并生成一组数据的讨论

电子说

1.4w人已加入

描述

1、对于AXI4-FULL总线时,握手信号共有5路,包括写地址,写数据,写应答,读地址,读数据。

2、当主机burst写时,每发起一次猝发交易,需要有一笔应答对应。

3、当主机进行读数据时,接受数据即可。

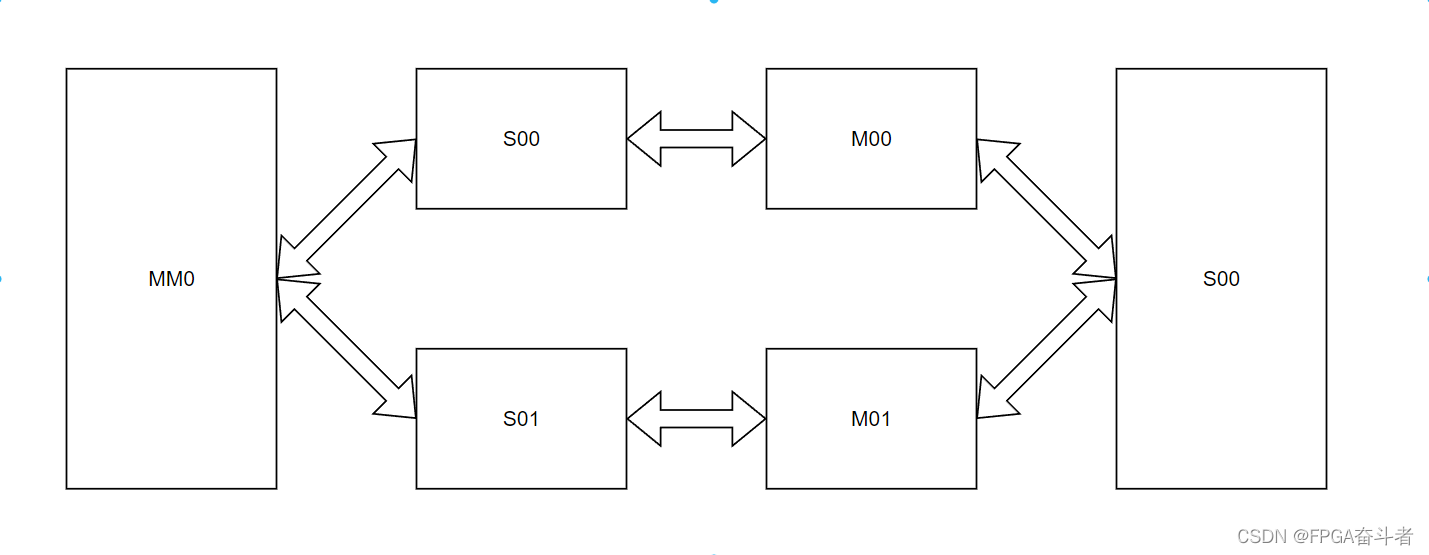

4、具体如图所示

5、共5路信号,每路信号都包括握手信号,ready和valid,当ready和valid都有效时,此时数据才有效,且信号不存在相互等待关系,以免发生死锁现象。

6、包括aw,w,b,ar,r,每路信号都应用FIFO做缓存,使数据对齐。

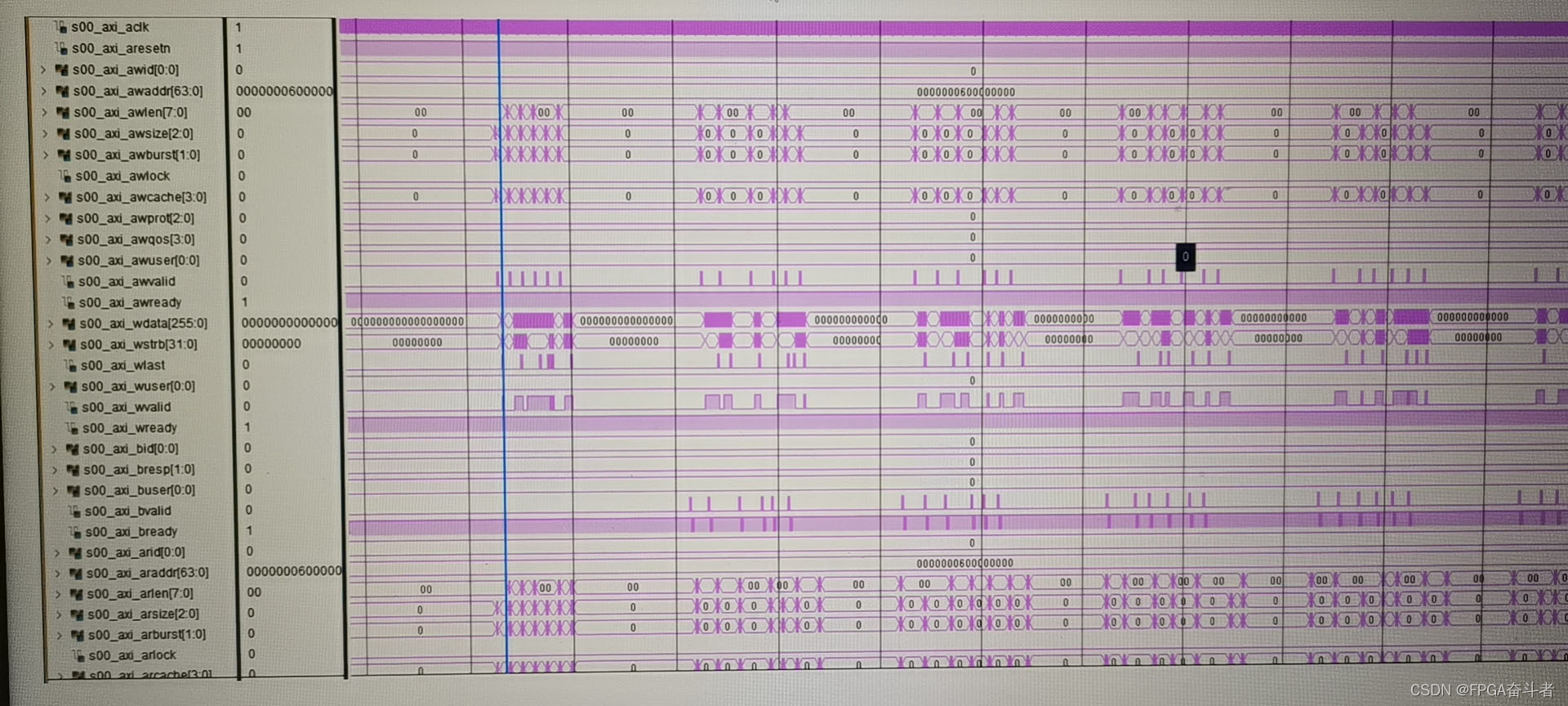

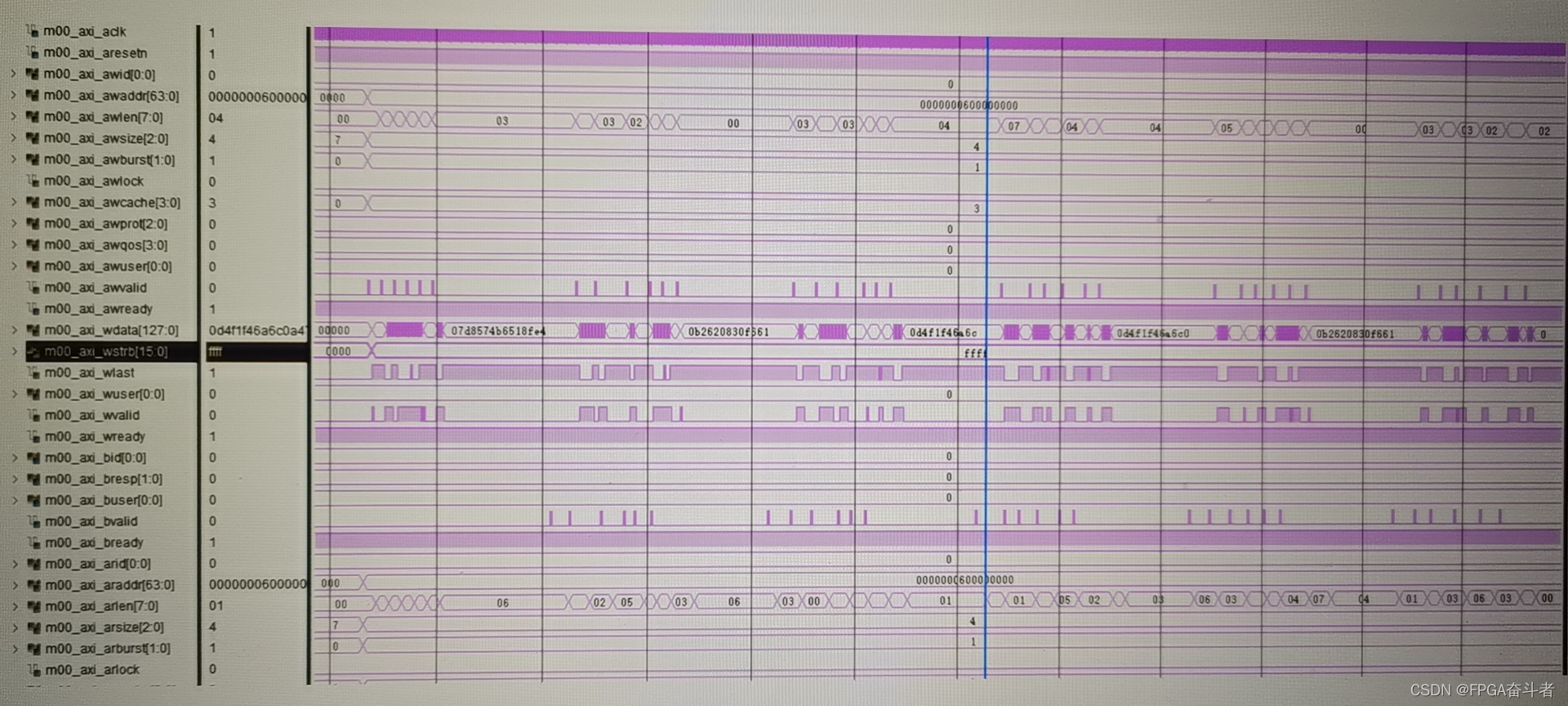

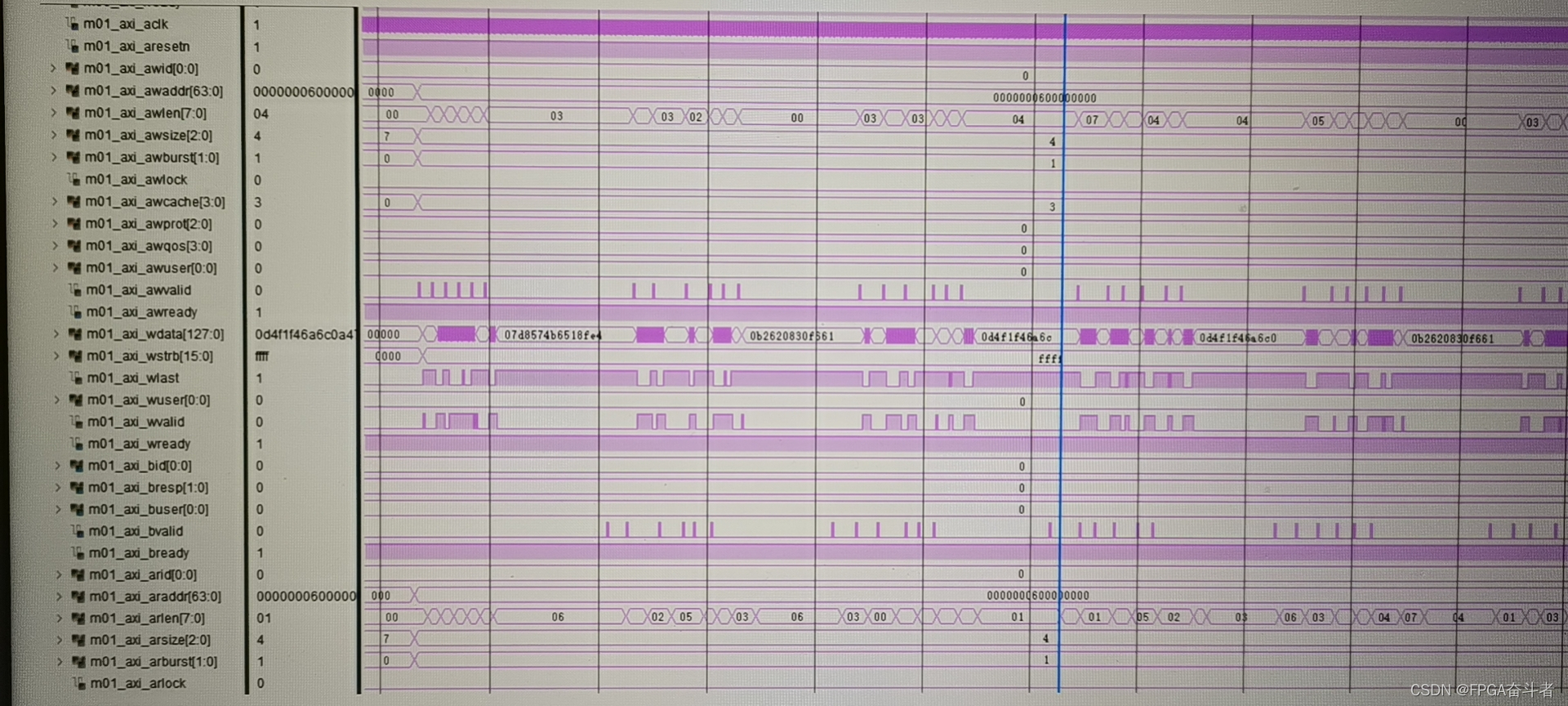

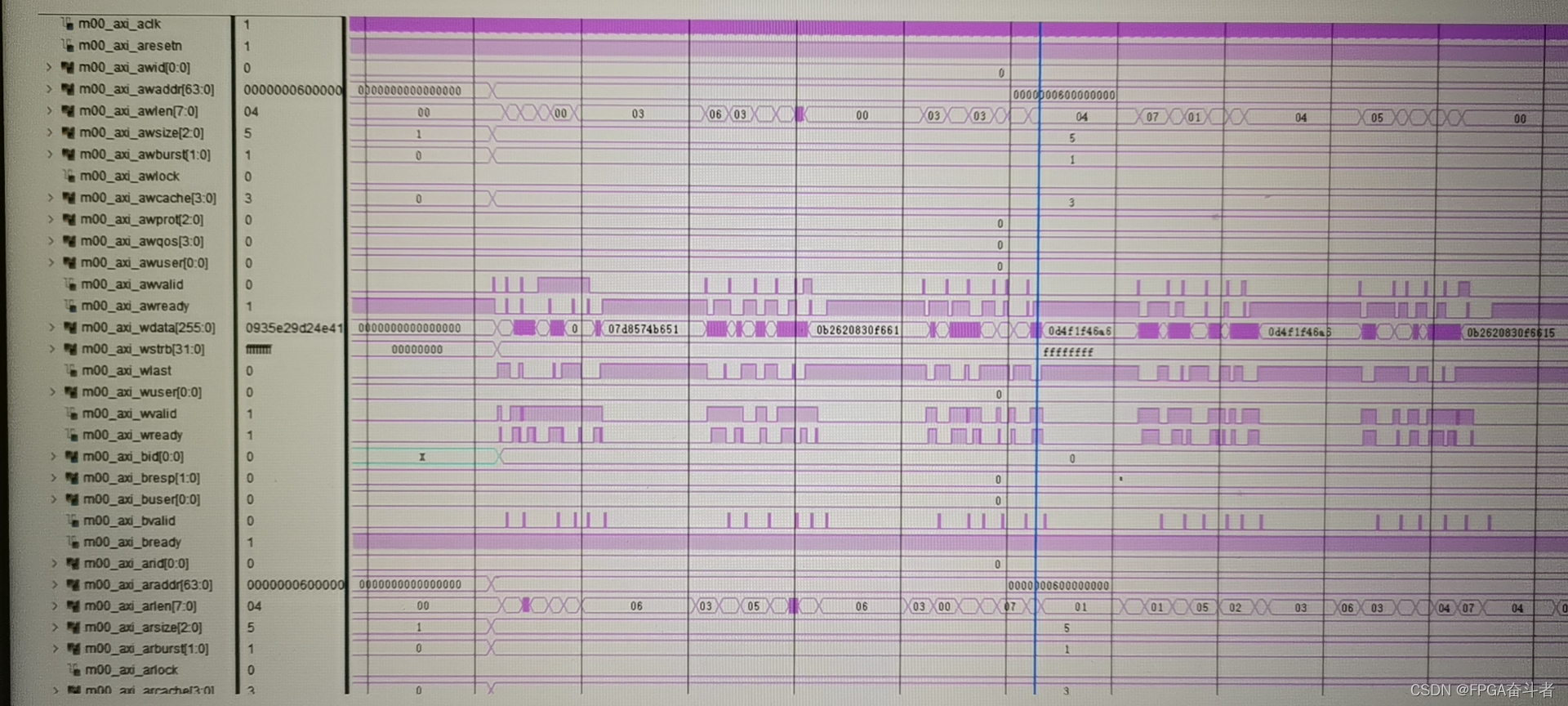

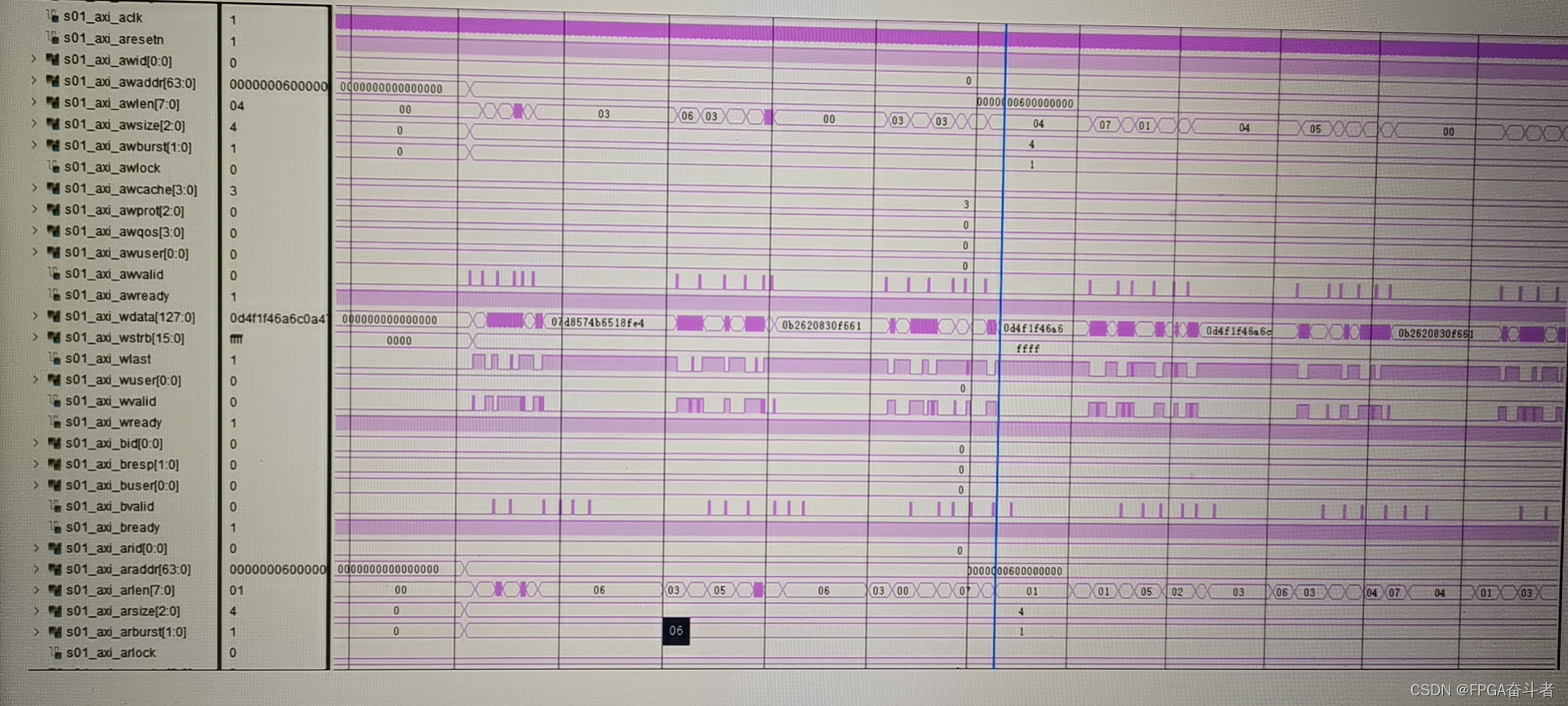

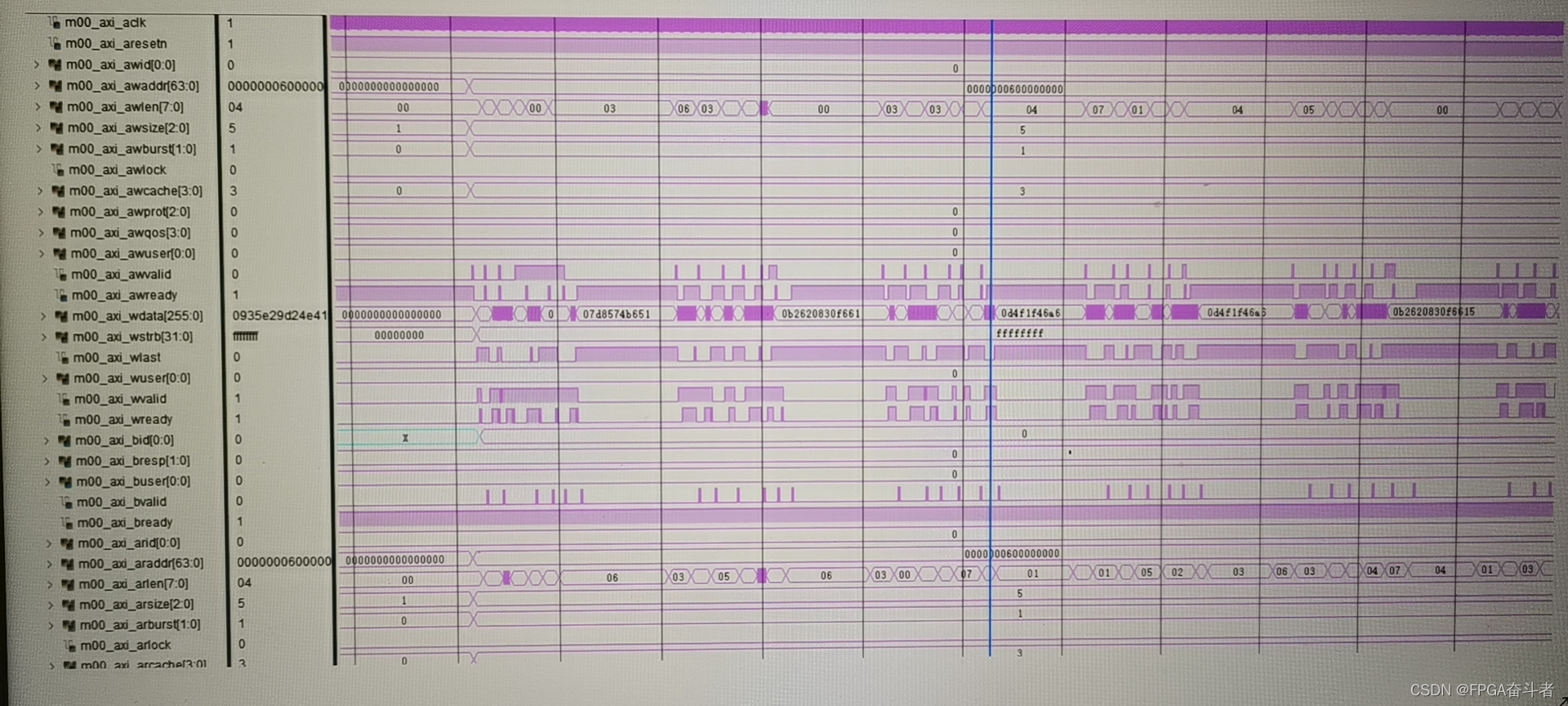

7、代码仿真如下

(1)

(2)

(3)

(4)

(5)

(6)

8、对其中的一组数据加延时,同样也可以使数据对齐,容忍度为FIFO的大小。

审核编辑:符乾江

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

多通道数据传输终端 LoRa/LTE双模通信终端稳控自动化 2025-10-24

-

NVMe IP之AXI4总线分析2025-06-02 6198

-

PCIe数据传输协议详解2024-11-26 6614

-

AXI传输数据的过程2023-10-31 2359

-

DMA进行数据传输和CPU进行数据传输的疑问2023-05-25 1245

-

浅析AXI DMA收发数据传输过程2022-10-11 3354

-

AXI-stream数据传输过程2021-01-08 2911

-

光纤通道应用的高数据传输接口设计问题怎么解决?2019-08-22 2240

-

玩转Zynq连载3——AXI总线协议介绍12019-05-06 2792

-

zynq的PS如何向一个基于AXI4-FULL协议的自定义IP批量传输数据?2017-02-22 9946

-

数据传输速率是什么意思2010-03-18 5296

-

基于SPI总线的无线数据传输系统设计2010-03-13 4234

-

PCI总线高速数据传输系统设计2009-09-21 972

全部0条评论

快来发表一下你的评论吧 !