FPGA虚拟时钟的使用方法

电子说

描述

在我之前写的FPGA时序约束教程中,有一篇中讲到了虚拟时钟:

FPGA时序约束理论篇之时钟周期约束

但文中对虚拟时钟的应用介绍的还不够详细,因此这里我们再对虚拟时钟做一个更加细致的介绍。

首先,虚拟时钟用于什么地方?

虚拟时钟通常用于设定输入和输出的延时,即set_input_delay和set_output_delay。可能有同学忘记这两个约束的用法了,这里我们再展示一下:

set_input_delay 0.5 -clock clkA [get_ports A] set_output_delay 1 -clock clkB [get_ports B]

其中clkA和clkB就是我们使用create_clock创建的主时钟或者虚拟时钟。

主时钟在创建的时候需要指定时钟输入端口,虚拟时钟不需要指定端口,所以称之为虚拟时钟。那什么场景下要用到虚拟时钟呢?

1. 外部IO的参考时钟并不是设计中的时钟

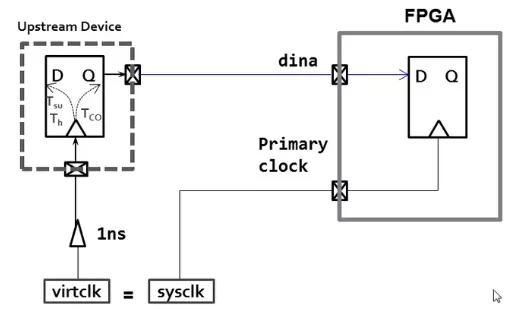

下图中,外部IO的参考时钟比设计中主时钟的路径上多了一个BUFFER,因此我们需要使用虚拟时钟来进行约束。

create_clock -name sysclk -period 10 [get_ports clkin] create_clock -name virtclk -period 10 set_clock_latency -source 1 [get_clock virtclk] set_input_delay -clock virtclk -max 4 [get_ports dina] set_input_delay -clock virtclk -min 2 [get_ports dina]

2. FPGA I/O路径参考时钟来源于内部衍生时钟,但与主时钟的频率关系并不是整数倍

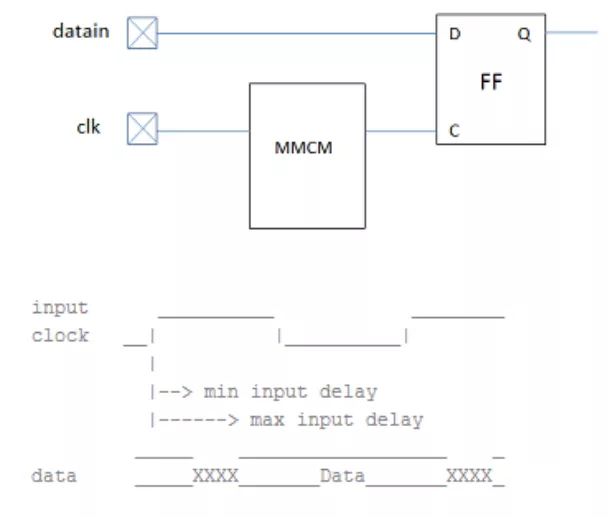

如果I/O路径参考时钟源于内部的衍生时钟,那set_input_delay和set_output_delay约束中-clock参数后的时钟不能是衍生时钟,比如下图的例子中,输入10MHz时钟经过了MMCM后去采输入的数据。

a) 如果MMCM没有负的相移而且输出的频率也是10MHz,那么直接使用主时钟来约束input delay。

create_clock -period 100.000 -name clk [get_ports clk] set_input_delay -clock clk -max 2.000 [get_ports datain] set_input_delay -clock clk -min 1.000 [get_ports datain]

b) 如果MMCM输出频率是60MHz,那么这个衍生时钟跟主时钟并不是整数倍关系,这时就需要用到虚拟时钟了

create_clock -period 100.000 -name clk [get_ports clk] create_clock -name clk_port_vclk -period 16.67 set_input_delay -clock clk_port_vclk -max 2 [get_ports datain] set_input_delay -clock clk_port_vclk -min 1 [get_ports datain]

3. 在不修改时钟特性的情况下针对I/O指定不同的jitter和latency

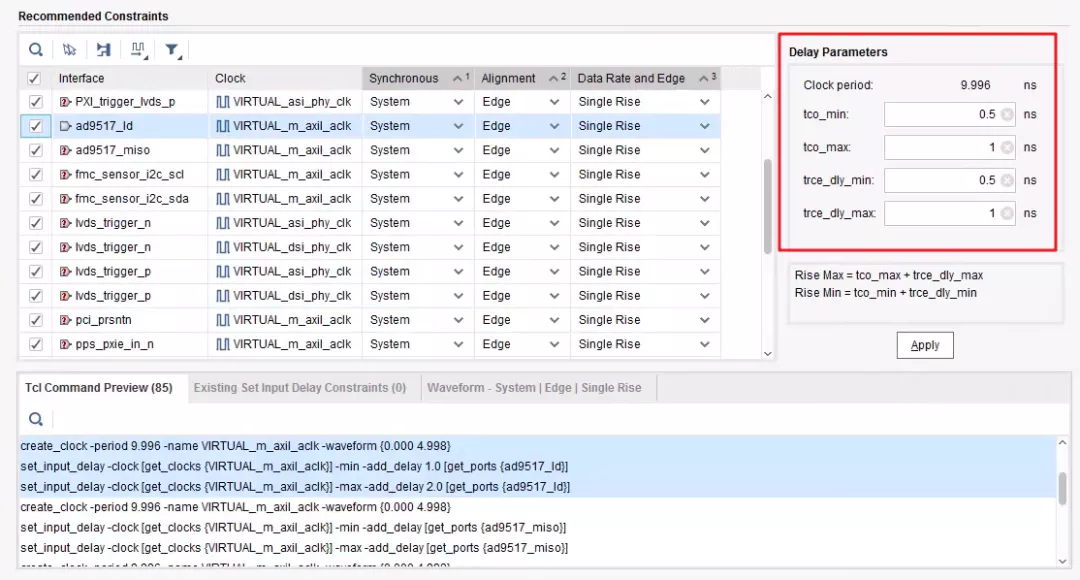

在设置完成后,可以看到Tcl Command Preview中提示的约束指令。

审核编辑:汤梓红

-

示波器使用方法2021-12-15 2294

-

DS1302时钟芯片使用方法2022-01-17 1311

-

Xilinx FPGA全局时钟资源的使用方法2010-11-03 1017

-

FPGA全局时钟和第二全局时钟资源的使用方法2017-02-11 5519

-

FPGA界最常用也最实用的3种跨时钟域处理的方法2017-11-15 14844

-

虚拟主机用途_虚拟主机使用方法步骤_虚拟主机如何绑定域名2018-01-19 2734

-

虚拟现实头盔如何_虚拟现实头盔的使用方法2020-05-27 4548

-

揭秘FPGA跨时钟域处理的三大方法2022-12-05 2684

-

示波器的使用方法(三):示波器的使用方法详解2020-12-24 4673

-

在FPGA中配置PLL的步骤及使用方法2021-05-28 1341

-

简述FPGA时钟约束时钟余量超差解决方法2021-10-11 4543

-

FPGA设计中动态时钟的使用方法2023-07-12 1999

-

XR虚拟拍摄中摄像机的使用方法2023-07-24 2262

-

Xilinx FPGA芯片内部时钟和复位信号使用方法2023-10-27 3805

-

FPGA如何消除时钟抖动2024-08-19 4206

全部0条评论

快来发表一下你的评论吧 !