Xilinx FPGA平台DDR3设计保姆式教程(一)

电子说

描述

一、DDR3简介

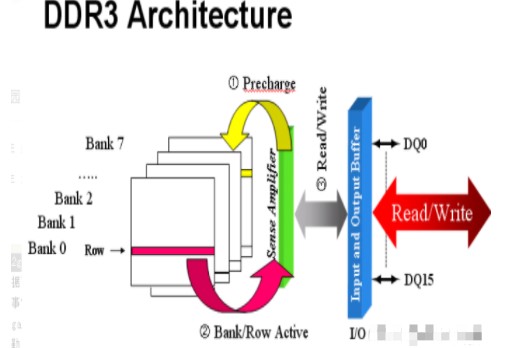

DDR3全称double-data-rate 3 synchronous dynamic RAM,即第三代双倍速率同步动态随机存储器。所谓同步,是指DDR3数据的读取写入是按时钟同步的;所谓动态,是指DDR3中的数据掉电无法保存,且需要周期性的刷新,才能保持数据;所谓随机存取,即可以随机操作任一地址的数据;所谓double-data-rate,即时钟的上升沿和下降沿都发生数据传输。

图1. DDR3结构

二、地址的概念及容量计算

2.1地址的概念

DDR3的内部是一个存储阵列,将数据“填”进去,你可以它想象成一张表格。和表格的检索原理一样,先指定一个行(Row),再指定一个列(Column),我们就可以准确地找到所需要的单元格,这就是内存芯片寻址的基本原理。对于内存,这个单元格可称为存储单元,那么这个表格(存储阵列)就是逻辑 Bank(Logical Bank,下面简称Bank)。

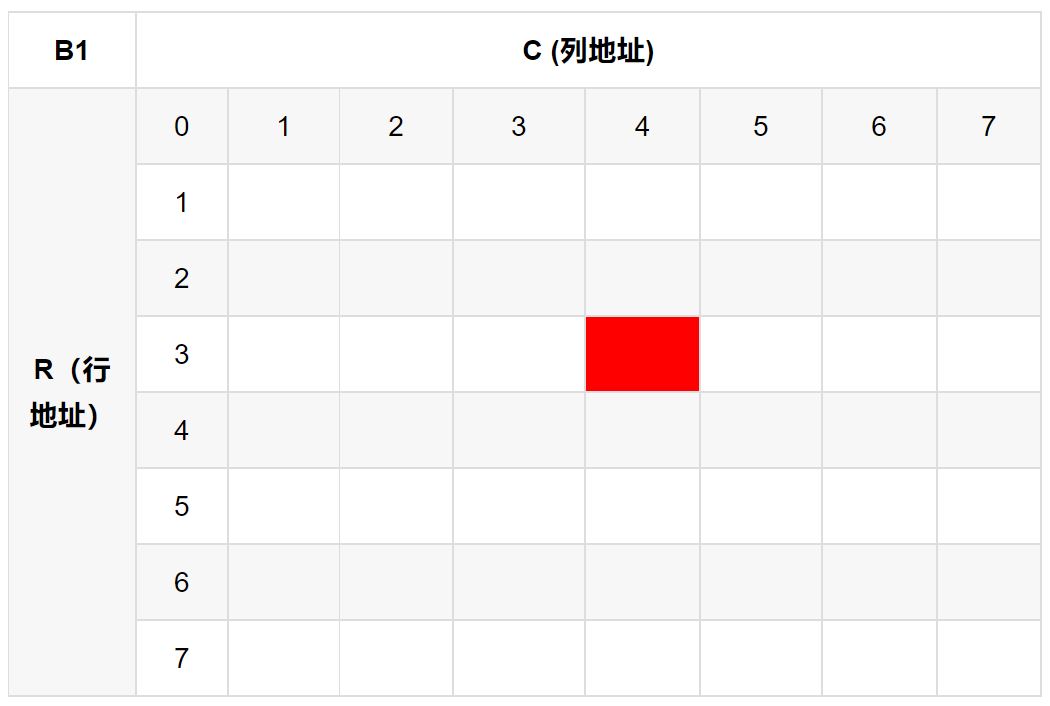

DDR3内部Bank示意图,这是一个MXN的阵列,B代表Bank地址编号,C代表列地址编号,R代表行地址编号。如果寻址命令是B1、R3、C4,就能确定地址是图中红格的位置目前DDR3内存芯片基本上都是8个Bank设计,也就是说一共有8个这样的“表格”。寻址的流程也就是先指定Bank地址,再指定行地址,然后指列地址最终的确寻址单元。

图2. DDR3地址

目前DDR3系统而言,还存在物理Bank的概念,这是对内存子系统的一个相关术语,并不针对内存芯片。内存为了保证CPU正常工作,必须一次传输完CPU 在一个传输周期内所需要的数据。而CPU在一个传输周期能接受的数据容量就是CPU数据总线的位宽,单位是bit(位)。控制内存与CPU之间数据交换的北桥芯片也因此将内存总线的数据位宽等同于CPU数据总线的位宽,这个位宽就称为物理Bank(Physical Bank,有的资料称之为Rank)的位宽。目前这个位宽基本为64bit。

2.2 DDR3容量计算

上一节我们已经说过bank、row、column的概念,容量就要据此来计算:

假设:

bank地址线位宽为3,及bank数目为 2^3=8;

行地址线位宽位13,及A0…A12;

列地址线位宽为10,及A0…A9;

有 2^3 * 2^13 * 2^10 = 2^26 =67108864b= 64Mb

再加上数据线,则容量为 64Mb x 16 = 128M Byte = =1G bit

三、重要给概念理解

3.1 行选通周期

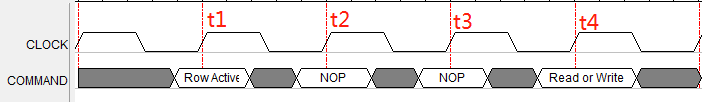

在实际工作中,Bank地址与相应的行地址是同时发出的,此时这个命令称之为“行激活”(Row Active)。在此之后,将发送列地址寻址命令与具体的操作命令(是读还是写),这两个命令也是同时发出的,所以一般都会以“读/写命令”来表示列寻址。根据相关的标准,从行有效到读/写命令发出之间的间隔被定义为tRCD,即RAS to CAS Delay(RAS至CAS延迟,RAS就是行地址选通脉冲,CAS就是列地址选通脉冲),我们可以理解为行选通周期。tRCD是DDR的一个重要时序参数,广义的tRCD以时钟周期(tCK,Clock Time)数为单位,比如tRCD=3,就代表延迟周期为两个时钟周期,具体到确切的时间,则要根据时钟频率而定,时钟频率100M,tRCD=3,代表30ns的延迟。

图3. 行选通周期tRCD

3.2 列地址脉冲选通潜伏期

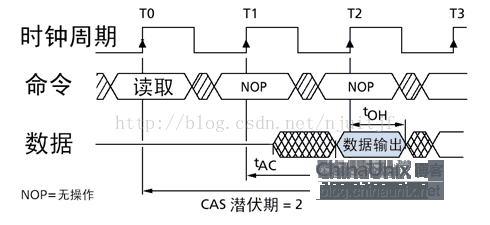

相关的列地址被选中之后,将会触发数据传输,但从存储单元中输出到真正出现在内存芯片的 I/O 接口之间还需要一定的时间(数据触发本身就有延迟,而且还需要进行信号放大),这段时间就是非常著名的 CL(CAS Latency,列地址脉冲选通潜伏期)。CL 的数值与 tRCD 一样,以时钟周期数表示。如 DDR3-800,时钟频率为 100MHz,时钟周期为 10ns,如果 CL=2 就意味着 20ns 的潜伏期。

注:CL只是针对读取操作。

图4. CL的概念(CL=2,tAC=1)

注意:delay与Latency虽然都有“延迟”的意思,但本质上是不同的

Delay :事情要在这个时间之后开始

Latency:事情已经发生,但是还不够稳定需要一个稳定时间

3.3 突发传输的概念

目前内存的读写基本都是连续的,因为与CPU交换的数据量以一个Cache Line(即CPU内Cache的存储单位)的容量为准,一般为64字节。而现有的Rank位宽为8字节(64bit),那么就要一次连续传输8次,这就涉及到我们也经常能遇到的突发传输的概念。突发(Burst)是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输的周期数就是突发长度(Burst Lengths,简称BL)。

在进行突发传输时,只要指定起始列地址与突发长度,内存就会依次地自动对后面相应数量的存储单元进行读/写操作而不再需要控制器连续地提供列地址。这样,除了第一笔数据的传输需要若干个周期(主要是之前的延迟,一般的是tRCD+CL)外,其后每个数据只需一个周期的即可获得。

连续读取模式:只要指定起始列地址与突发长度,后续的寻址与数据的读取自动进行,而只要控制好两段突发读取命令的间隔周期(与BL相同)即可做到连续的突发传输。

在 DDR SDRAM 中,突发长度只有 2、4、8 三种选择,没有了随机存取的操作(突发长度为 1)和全页式突发。这是为什么呢?因为 L-Bank一次就存取两倍于芯片 位宽的数据,所以芯片至少也要进行两次传输才可以,否则内部多出来的数据怎么处理?但是,突发长度的定义也与 SDRAM 的不一样了,它不再指所连续寻址的存储单元数量,而是指连续的传输周期数,每次是一个芯片位宽的数据。

上面是别人的解释,笔者结合自己的理解和代码实现中再解释一下:

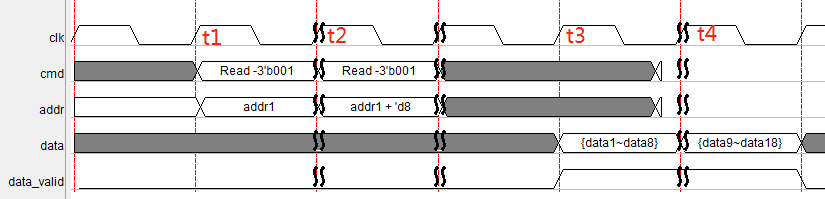

突发传输是为了提高传输效率,这涉及到预取的概念;DDR3突发长度BL=8,在t1时刻我们发起读命令,给出地址addr1,那么因为是突发传输,所以实际我们将读出addr1以及它之后地址,总共8个地址,也就读出了8个数据;那么t2时刻,我们继续读数,给出的地址addr=addr1+8;结合下图更容易理解:

图5. 突发传输

注:

t1 ,t2 / t3,t4时刻不一定连续;要看ddr是否准备好,具体到代码就是app_rdy 并不是一直为高;

3.4 掩码

掩码简单解释下,就是屏蔽掉我们传输不需要的数据;掩码每一位bit对应ddr数据的1个字节;当掩码为0,数据有效;当掩码为1,数据屏蔽;

一般不使用,传输数据全部有效,掩码直接置0:(掩码位宽根据数据位宽而定)

assign app_wdf_mask = 64'b0;

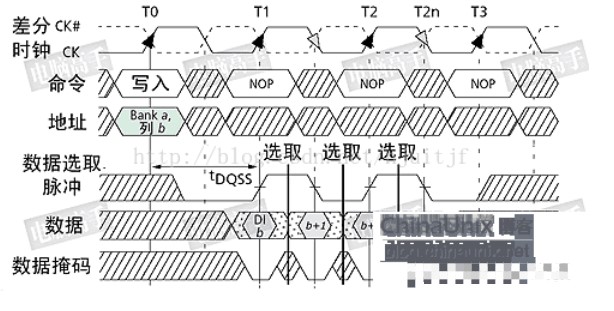

3.5 数据选取脉冲(DQS)

DQS 是DDR中的重要功能,它的功能主要用来在一个时钟周期内准确的区分出每个传输周期,并便于接收方准确接收数据。每一颗芯片都有一个DQS信号线,它是双向的,在写入时它用来传送由北桥发来的DQS信号,读取时,则由芯片生成DQS向北桥发送。完全可以说,它就是数据的同步信号。

在读取时,DQS与数据信号同时生成(也是在CK与CK#的交叉点)。而DDR内存中的CL也就是从CAS发出到DQS生成的间隔,DQS生成时,芯片内部的预取已经完毕了,由于预取的原因,实际的数据传出可能会提前于DQS发生(数据提前于DQS传出)。由于是并行传输,DDR内存对tAC也有一定的要求,对于DDR266,tAC的允许范围是±0.75ns,对于DDR333,则是±0.7ns,有关它们的时序图示见前文,其中CL里包含了一段DQS 的导入期。

DQS 在读取时与数据同步传输,那么接收时也是以DQS的上下沿为准吗?不,如果以DQS的上下沿区分数据周期的危险很大。由于芯片有预取的操作,所以输出时的同步很难控制,只能限制在一定的时间范围内,数据在各I/O端口的出现时间可能有快有慢,会与DQS有一定的间隔,这也就是为什么要有一个tAC规定的原因。而在接收方,一切必须保证同步接收,不能有tAC之类的偏差。这样在写入时,芯片不再自己生成DQS,而以发送方传来的DQS为基准,并相应延后一定的时间,在DQS的中部为数据周期的选取分割点(在读取时分割点就是上下沿),从这里分隔开两个传输周期。这样做的好处是,由于各数据信号都会有一个逻辑电平保持周期,即使发送时不同步,在DQS上下沿时都处于保持周期中,此时数据接收触发的准确性无疑是最高的。

在写入时,以DQS的高/低电平期中部为数据周期分割点,而不是上/下沿,但数据的接收触发仍为DQS的上/下沿。

四、参考资料

如果我们只是拿来用ddr搬砖,那么它就简单,知道IP怎么使用就好,但是要想知其所以然,理论知识是必备的,这也是我们初学者所欠缺的东西,慢慢修炼吧!

参考资料①,里面所有信号都有解释,感兴趣的和想提升的可以仔细研究:

DDR基础详解

参考资料②,超详细DDR3底层原理介绍,大佬首选

深入浅出DDR系列(一)--DDR原理篇

审核编辑:汤梓红

-

基于FPGA的DDR3读写测试2023-09-01 3749

-

xilinx平台DDR3设计教程之设计篇_中文版教程32023-08-05 7452

-

FPGA学习-DDR32022-12-21 5642

-

Xilinx FPGA平台DDR3设计保姆式教程(六)2022-02-26 2776

-

Xilinx FPGA平台DDR3设计保姆式教程(二)2022-02-21 5038

-

基于Arty Artix-35T FPGA开发板的DDR3和mig介绍2021-01-01 5582

-

xilinx平台DDR3设计教程之仿真篇2020-03-12 2415

-

基于FPGA的DDR3 SDRAM控制器用户接口设计2017-11-17 4159

-

Xilinx DDR3最新VHDL代码(通过调试)2016-06-07 1483

-

Xilinx DDR3 资料2016-05-27 3824

-

FPGA外接DDR3,带宽怎么计算?2016-02-17 14766

-

xilinx平台DDR3设计教程2015-09-18 15489

-

基于FPGA的DDR3多端口读写存储管理系统设计2015-04-07 14154

全部0条评论

快来发表一下你的评论吧 !