进入IP Core的时钟,都不需要再手动添加约束吗

电子说

1.4w人已加入

描述

在FPGA的时序约束中,主时钟约束是第一步就要做的,主时钟通常有两种情形:一种是时钟由外部时钟源提供,通过时钟引脚进入FPGA,该时钟引脚绑定的时钟为主时钟:另一种是高速收发器(GT)的时钟RXOUTCLK或TXOUTCLK。对于7系列FPGA,需要对GT的这两个时钟手工约束:对于UltraScale FPGA,只需对GT的输入时钟约束即可,Vivado会自动对这两个时钟约束。

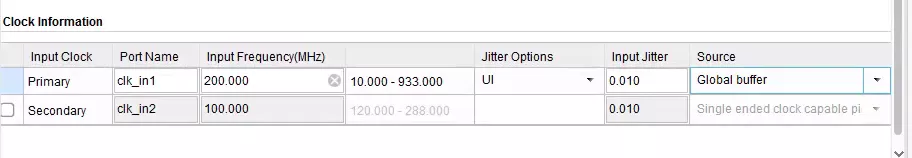

对于进入到IP Core(比如MMCM)的主时钟,只有我们在IP Core中指定了时钟频率,那么Vivado会自动产生一个约束文件来约束该输入的主时钟。

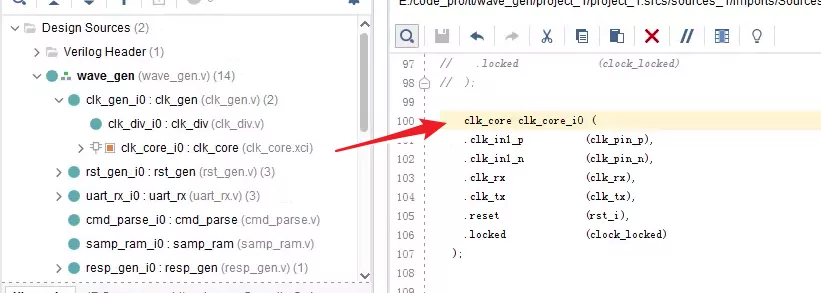

我们以Vivado自带的wave_gen工程为例,该工程中输入一对差分的时钟信号,进入到MMCM中,我们无需再对这个主时钟添加约束。

可以看到,综合后这个时钟已经被约束了:

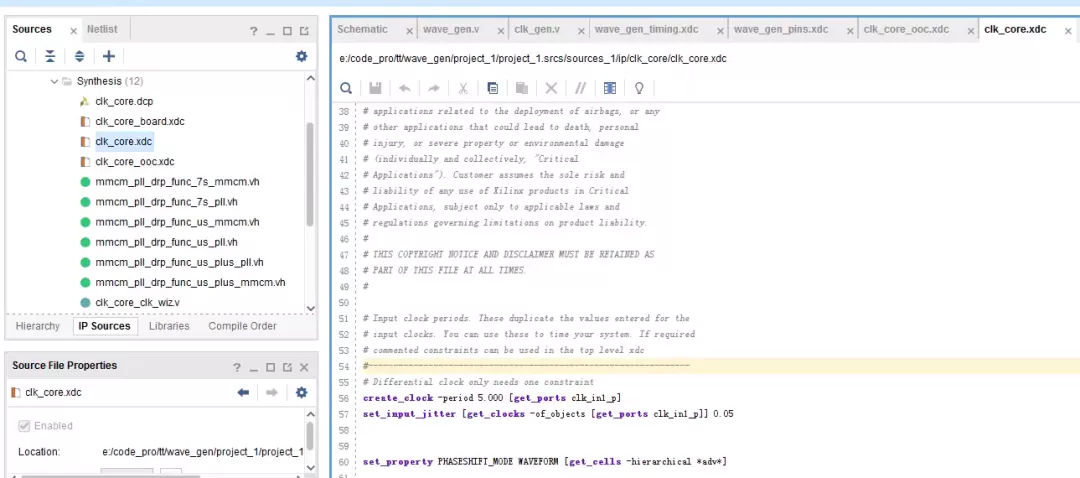

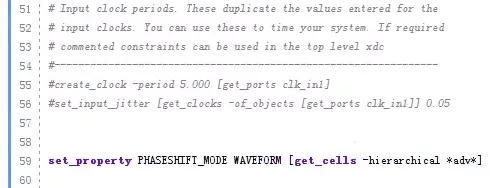

这是因为该ip生成的xdc文件中,已经包含了对这个主时钟的约束,如下图:

所以很多同学可能误以为只要是进了IP Core的主时钟,都不需要再手动添加约束了。

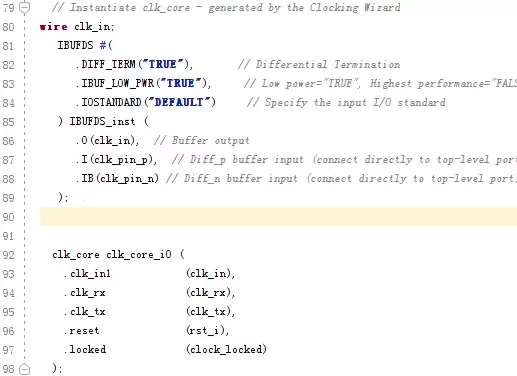

但如果收入的差分时钟先经过了IBUFDS,然后再以单独的形式进入了MMCM:

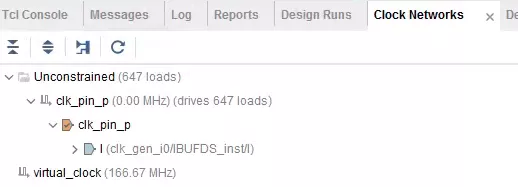

综合后,可以看到该时钟是没有被约束的:

此时由于输入时钟并非来自管脚,所以Source选择为Global Buffer

再看刚刚的clk_core.xdc文件,已经没有产生主时钟的约束了:

为什么会没有这个约束了呢?因为输入的时钟并非来自管脚,IP Core并不知道从哪个pin输入的,所以就无法添加主时钟的约束,此时就需要我们再手动添加约束。

审核编辑:符乾江

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

请问WIFI模块都不需要用心跳包吗?2019-04-03 3537

-

为什么放置cutout再覆铜怎么也不能切除不需要的铜?2019-06-06 2203

-

STM32外设为什么不需要开启复用时钟(AFIO时钟)呢2021-11-24 2415

-

IP CORE 之 FIFO 设计- ISE 操作工具2023-04-11 940

-

不需要场效应管的多路传输开关2009-04-13 1103

-

添加时序约束的技巧分析2017-11-25 3232

-

HTC Vive和Vive Pro两款高级虚拟现实(VR)体验不需要再受到电线的约束2018-08-24 3631

-

未来全固态电池,真得不需要冷却吗?2019-03-07 6977

-

FPGA案例之衍生时钟约束2020-11-17 3455

-

不需要电感器2021-04-29 878

-

对讲机到底需不需要中继台?2023-03-15 4694

-

如何用手动方式添加诊断帧2023-09-13 3162

-

六类屏蔽网线和六类非屏蔽网线都不需要接地吗2024-03-08 6900

-

时序约束一主时钟与生成时钟2024-11-29 2829

-

系统c盘满了怎么清理不需要文件2025-11-22 1205

全部0条评论

快来发表一下你的评论吧 !