Xilinx System Generator for DSP纪事—RTL设计的生成

电子说

描述

注:本文转自赛灵思中文社区论坛,源文链接在此。本文原作者为XILINX工程师。

以下为个人译文,仅供参考,如有疏漏之处,还请不吝赐教。

本篇博文是面向希望学习 Xilinx System Generator for DSP 入门知识的新手的系列博文第一讲。

其中提供了有关执行下列操作的分步操作方法指南:

- 使用 Xilinx System Generator 块集合对用户算法进行建模

- 对设计进行仿真并以可视化方式直观展示输入/输出以验证设计

- 为设计生成测试激励文件、测试矢量和 RTL (VHDL/Verilog) 代码

Xilinx System Generator for DSP 可为基于模型的设计与系统集成平台提供模块框图环境,以支持将 DSP 系统的 RTL、Simulink®、MATLAB® 和 C/C++ 组件整合到面向赛灵思 FPGA 器件的单一仿真和实现环境中。

它包含一个已预定义并预优化的开箱即用的块集合,可用于对算法进行建模、仿真和分析,并生成测试激励文件、测试矢量以及 HDL 代码,从而加速 FPGA 开发。

System Generator 支持针对以下编译目标生成自动代码 (Automatic Code):

- HDL 网表

- IP 目录

- 已综合的检查点

- 硬件协同仿真

配置 MATLAB

首先,我们需要安装 MATLAB 并对 MATLAB 进行相应配置,确保它可配合 Vivado Design Suite 一起使用。

具体操作如下:

在 Windows 上:

以管理员身份打开“开始 >(所有)程序 > Xilinx Design Tools > Vivado 2019.x > System Generator > System Generator 2019.x MATLAB Configurator”。

出现 MATLAB 配置窗口后,勾选相应版本的 MATLAB 对应的复选框。

单击“Apply”,然后单击“OK”。

在 Linux 上:

请确保可在 Linux 系统的 $PATH 环境变量中找到 MATLAB 可执行文件。

Linux 下的 System Generator 是使用名为“sysgen”的 shell 脚本处理的,此脚本位于 /bin 目录中。

本实践教程操作步骤如下:

本篇博文是面向希望学习 Xilinx System Generator for DSP 入门知识的新手的系列博文第一讲。

其中提供了有关执行下列操作的分步操作方法指南:

1. 使用 Xilinx System Generator 块集合对用户算法进行建模

2. 对设计进行仿真并以可视化方式直观展示输入/输出以验证设计

3. 为设计生成测试激励文件、测试矢量和 RTL (VHDL/Verilog) 代码

实践教程将按以上指定的编译目标顺序予以展示。

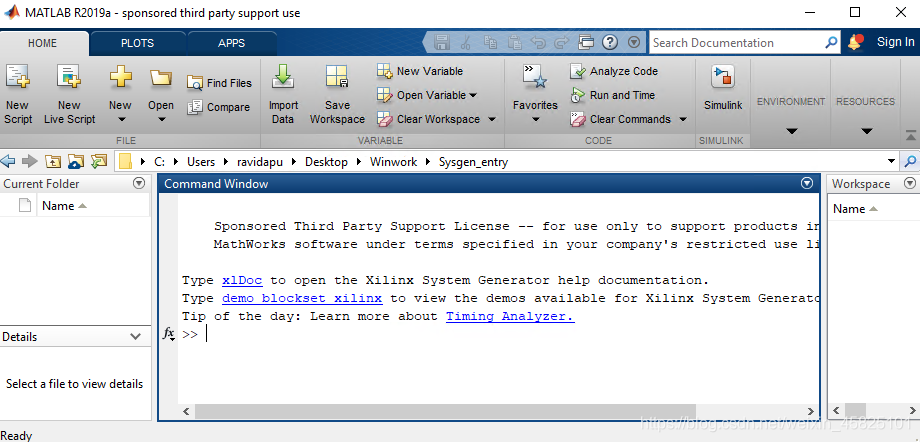

步骤 1:遵循以下对应于您的操作系统的步骤调用 System Generator:

- 在 Windows 系统上,选择“开始 >(所有)程序 > Xilinx Design Tools > Vivado 2019.x >System Generator > System Generator 2019.x”

- 在 Linux 系统上的命令提示符处输入 sysgen

此步骤将打开包含 System Generator 块集合的 MATLAB 会话。

如以下截屏所示:

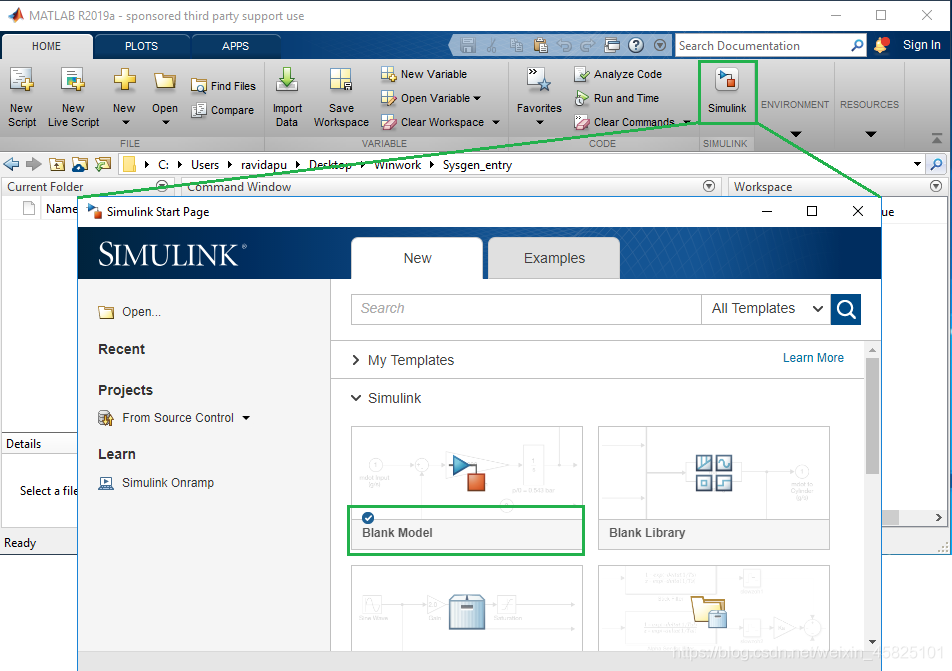

步骤 2:将工作目录更改为包含创建的 Sysgen 模型的任意本地目录。

单击位于 MATLAB 窗口右上角的 Simulink 图标。

这样将打开 Simulink Start Page:

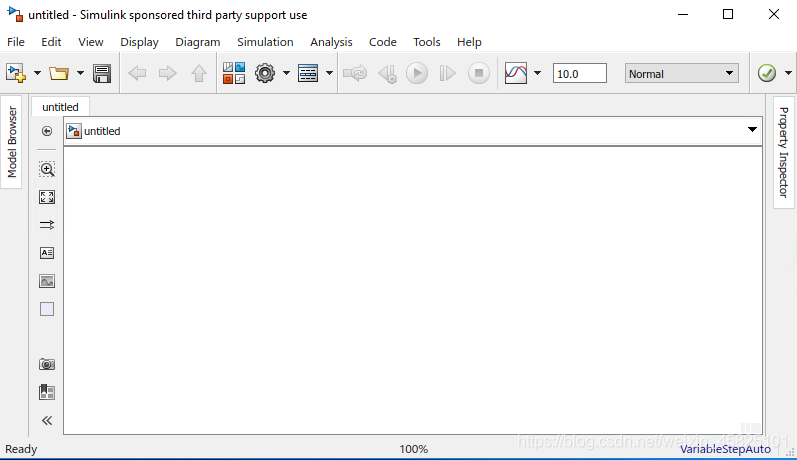

步骤 3:单击 Simulink 下拉选项的“Blank model”图标。

这样将打开空白或“Untitled”模型,其中包含空白的模型画布。

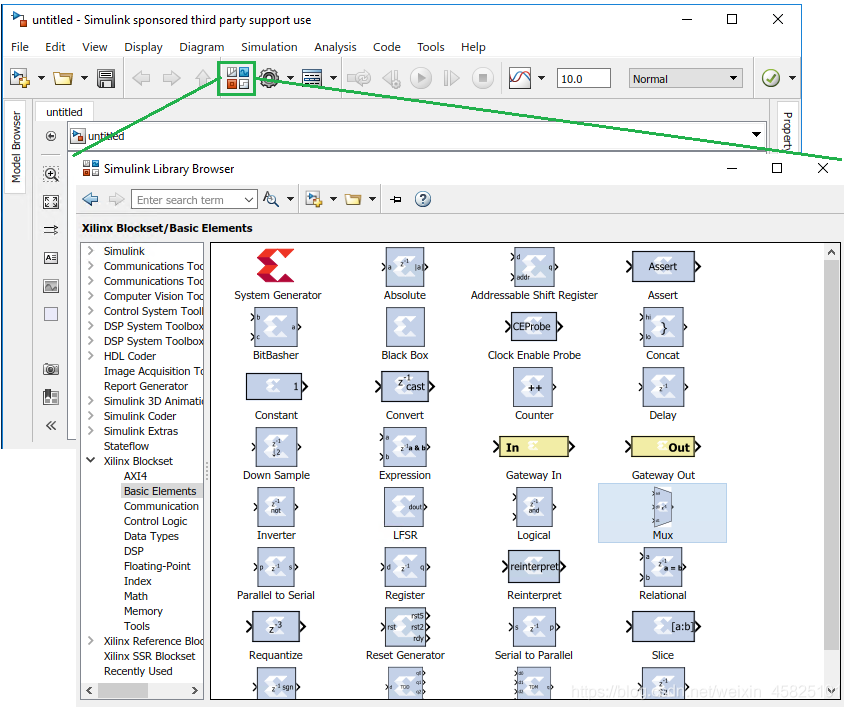

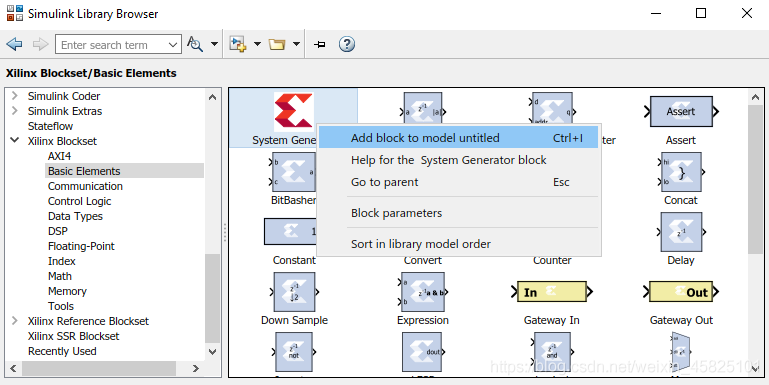

步骤 4:单击“Untitled”模型窗口中的“Library browser”图标以便在“Simulink Library Browser”窗口中查看赛灵思块集合。

单击并展开“Xilinx Blockset”菜单,以查看不同类别的块。单击“Basic elements”类别,以查看基本 sysgen 块,如下所示:

步骤 5:右键单击并选择“Add block to model”(Ctrl+I) 选项将 System Generator 标识块添加到模型中以定义 FPGA 技术。

以同样方式添加“Gateway In”和“Gateway Out”块,以定义设计的 System Generator 部分与 Simulink 部分之间的界限。

注:任何模型都必须包含这些必需的块。每个模型都必须至少包含 1 个 System Generator 块,可包含多个“Gateway In”和“Gateway Out”块,具体取决于设计的输入和输出。

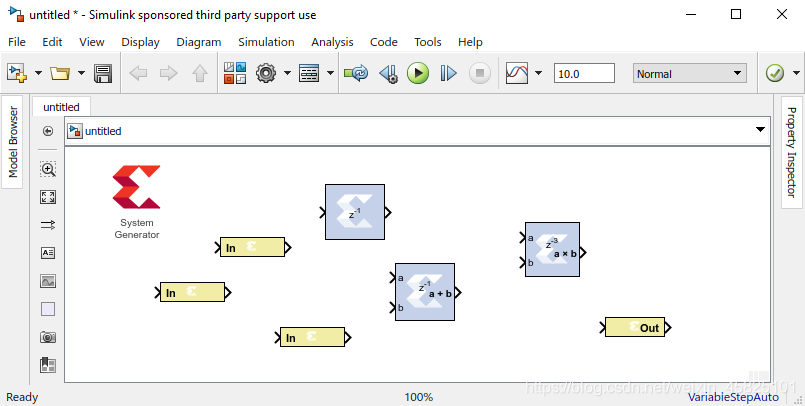

此处演示的是添加乘累加 (Mult-add) 运算的建模过程,因此我们需要将“Mult”、“AddSub”和“Delay”块添加到模型中。

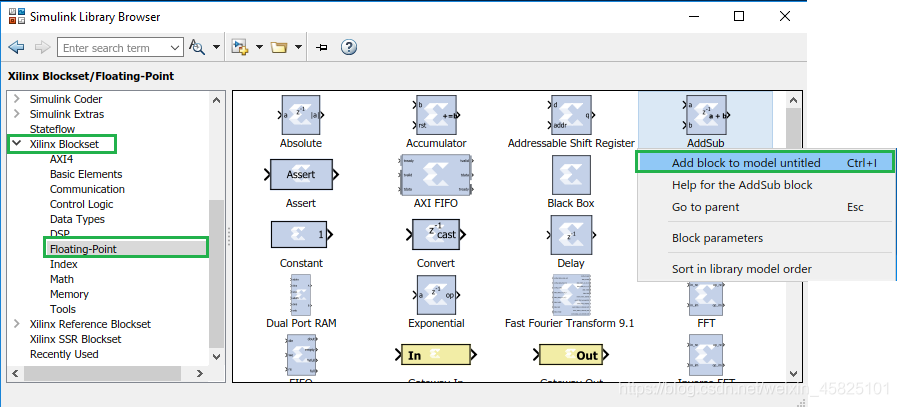

步骤 6:选中“Xilinx Blockset”下的“Floating-Point”类别中的“AddSub”块,右键单击,然后单击“Add block to model”选项。

步骤 7:以同样方式选中“Xilinx Blockset”下的“Floating-Point”类别中的“Mult”块和“Basic Elements”类别下的“Delay”块,并将这两个块添加到模型中。

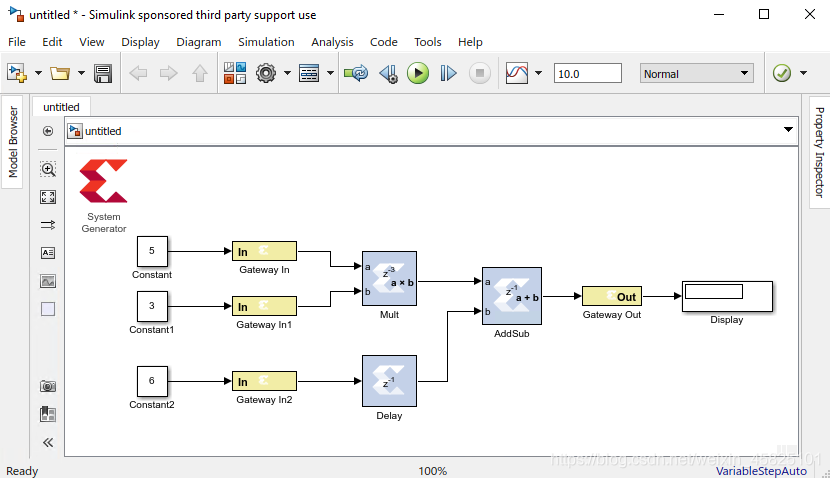

这样模型将如下图所示:

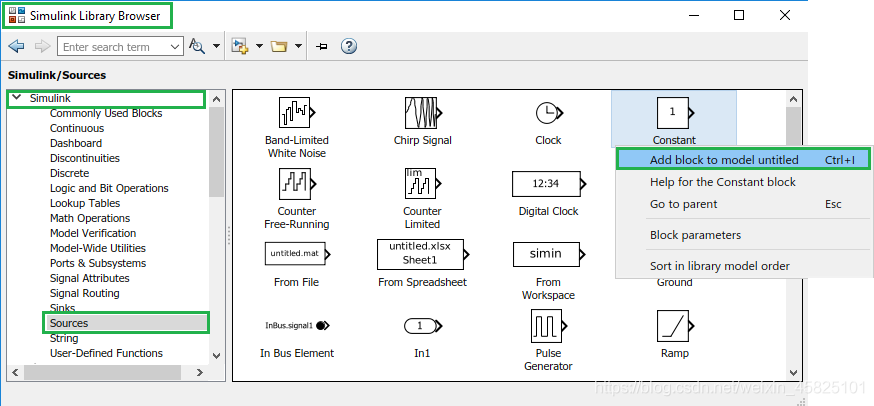

步骤 8:现在,添加 3 个“Constant”块实例,此“Constant”块可在“Simulink Library Browser”的“Simulink”块集合下的“Sources”类别中找到:

以同样方式添加来自“Simulink”块集合下的“Sinks”类别的“Display”块。

这些块用作为 System Generator 设计的激励块。

步骤 9:按住鼠标左键并绘制一条从源端口到目标端口的线,以将块连接在一起。

完整的模型将如下所示:

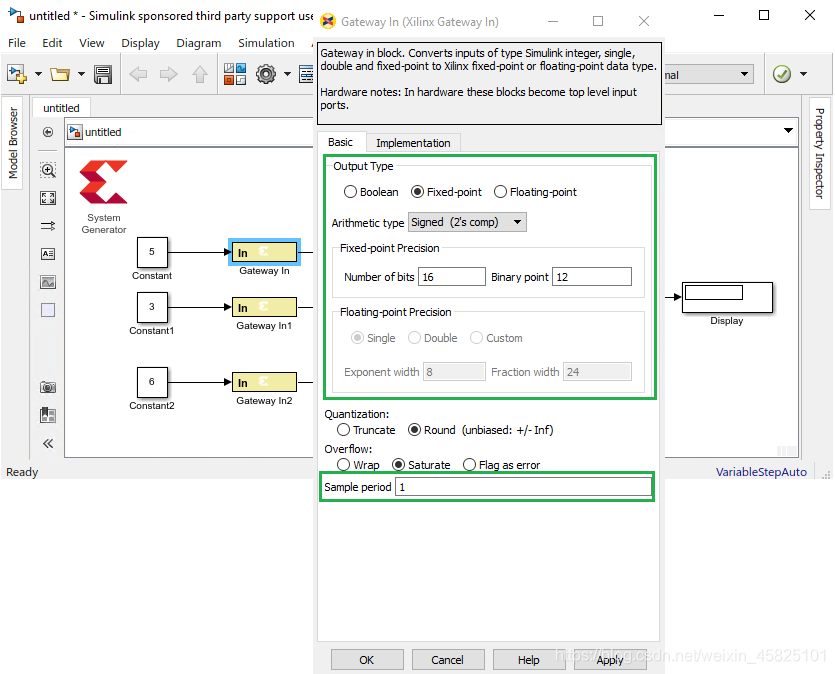

步骤 10:双击“Gateway In”块以打开“Properties Editor”,根据块 GUI 中的“Output type”和“Sample period”下的输入值来设置输入数据类型,然后单击“OK”。

针对其他输入重复该过程:

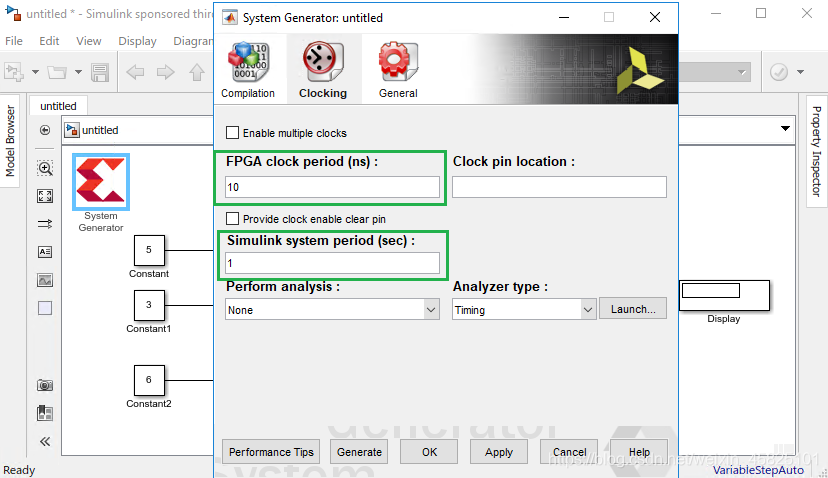

步骤 11:双击 System Generator 标识以更改系统和仿真参数。

确保“clocking”选项卡下的“Simulink system period”与“Gateway In”块的样本周期相同。

“FPGA clock period”应为“Simulink system period”的整数倍。

单击“OK”。

步骤 12:单击模型工具栏上的保存按钮、为其提供有效的名称,然后单击“Save”以保存设计(在步骤 3-9 间可随时执行此步骤)。

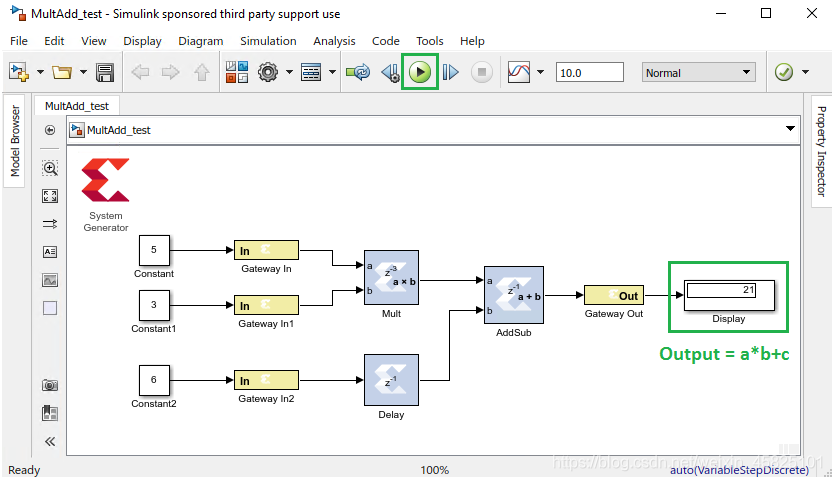

步骤 13:单击“Run”按钮以对模型进行仿真并验证输出:

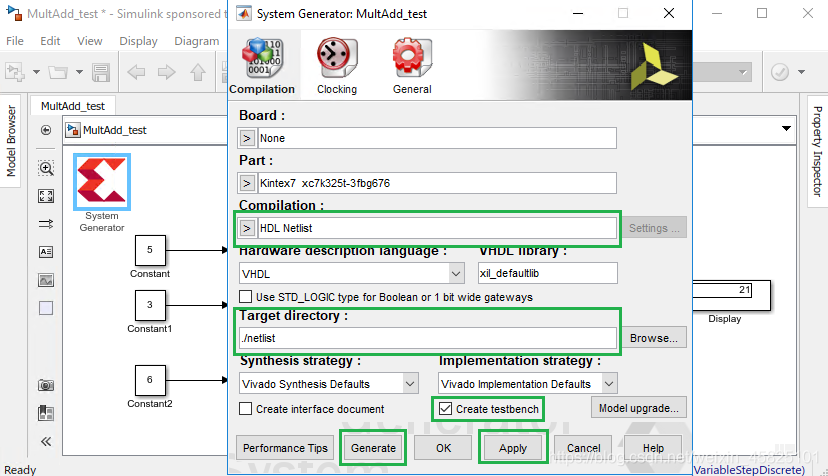

步骤 14:双击 System Generator 标识,确保:

- “Compilation”已设置为“HDL Netlist”

- “Target directory”选项设置为包含所生成 RTL 代码的任意有效目录(在此示例中目录为 netlist)

- 已选中“Compilation”选项卡上的“Create testbench”选项

对于其他选项,保留默认设置。

现在,单击“Apply”,然后单击“Generate”按钮。

注:System Generator 标识充当用于控制系统和仿真参数的控制面板,并且还可用于调用代码生成器。

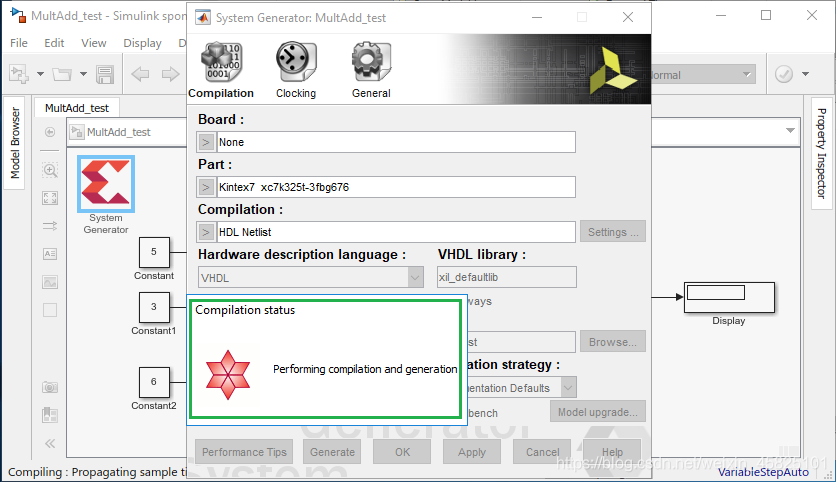

步骤 15:代码生成过程开始后,就会弹出状态窗口,如下所示:

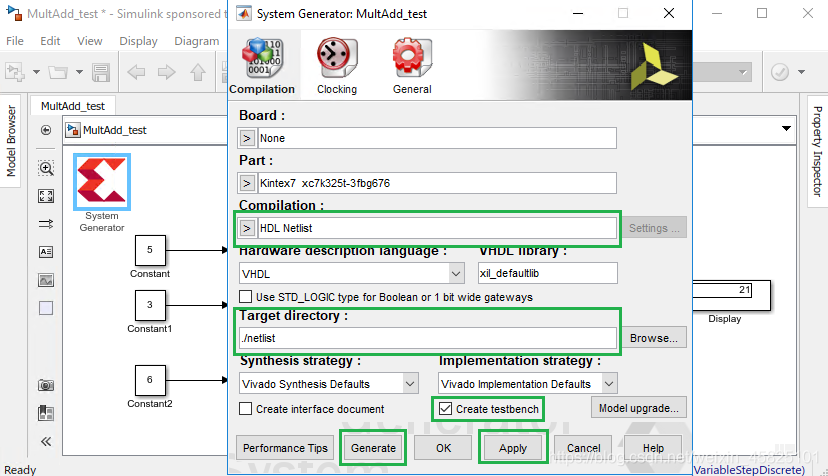

步骤 16:代码生成完成后,状态窗口将通知您代码生成过程已完成。

在此处截屏中所示的示例中,System Generator 已成功生成 Kintex-7 xc7k325t-3fbg676 器件的 VHDL RTL 设计,包括测试矢量和测试激励文件。

现在,请启动 Vivado,打开“netlist/hdl_netlist/Multadd_test.xpr”文件,然后按下文中详述的步骤运行 Vivado 流程:

Vivado 设计输入纪事 - RTL 设计输入

审核编辑:符乾江

-

谁有xilinx公司的网络教程“利用 System Generator 进行 D...2013-03-14 2064

-

ISE 与matlab连接 问题 system generator for DSP simulink2013-10-05 13468

-

可以使用基于Vivado的System Generator来开发ISE系统吗?2018-12-27 4330

-

System Generator for DSP(SysGen)的许可证签出失败2018-12-29 2962

-

安装SDx 2017.2时无法安装System Generator2019-01-07 3839

-

System Generator for DSP的许可证失败2019-01-28 3325

-

System Generator是MatLab到RTL的转换吗2019-04-25 2156

-

安装System Generator时System Generator for DSP这个选项没有出现怎么办?2023-09-26 924

-

基于System Generator的数字下变频设计2013-01-10 1439

-

System Generator的设计实例2016-06-07 1020

-

Xilinx System Generator大幅简化无线系统设计2017-02-09 517

-

System generator如何与MATLAB进行匹配?2017-02-11 7993

-

FPGA开发之算法开发System Generator2017-11-17 9173

-

利用 ISE 和 System Generator for DSP 10.1 提高 DSP 设计生产率2018-06-06 4129

-

如何将IP模块整合到System Generator for DSP中2018-11-20 3972

全部0条评论

快来发表一下你的评论吧 !