使用Jtag Master来调试FPGA程序

电子说

描述

对FPGA进行上板调试时,使用最多的是SignalTap,但SignalTap主要用来抓取信号时序,当需要发送信号到FPGA时,Jtag Master可以发挥很好的作用,可以通过Jtag Master对FPGA进行读写测试,使用tcl脚本控制Jtag Master可以完成复杂的测试功能。使用jtag master进行调试时分为如下步骤:

- 将JTAG to Avalon Master Bridge Intel FPGA IP加入代码

- 根据Avalon-MM总线时序编写测试代码

- 编写tcl脚本

- 在System Console上运行tcl脚本进行调试

Jtag Master

在逻辑代码中加入JTAG to Avalon Master Bridge Intel FPGA IP ,IP路径如下。

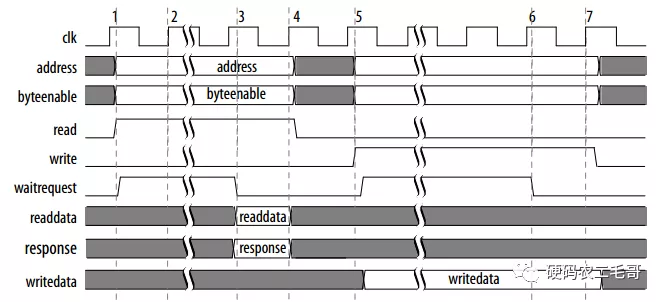

Avalon-MM总线时序

jtag_master模块例化到fpga代码中,使用Verilog根据Avalon-MM时序图编写读写代码。master_read有效时将数据发送到master_readdata。master_write有效时,将master_writedata数据写入FPGA。

jtag_master u0 (

.clk_clk (_connected_to_clk_clk_),

.clk_reset_reset (_connected_to_clk_reset_reset_),

.master_reset_reset (_connected_to_master_reset_reset_),

.master_address (_connected_to_master_address_),

.master_readdata (_connected_to_master_readdata_),

.master_read (_connected_to_master_read_),

.master_write (_connected_to_master_write_),

.master_writedata (_connected_to_master_writedata_),

.master_waitrequest (_connected_to_master_waitrequest_),

.master_readdatavalid (_connected_to_master_readdatavalid_),

.master_byteenable (_connected_to_master_byteenable_)

);

编写TCL脚本

global claimed_path_jtag

#启动jtag master服务

proc start_jtag {} {

set service_type "master"

set jtag_path [lindex [get_service_paths $service_type] 0]

puts $jtag_path

set ::claimed_path_jtag [claim_service $service_type $jtag_path mylib]

}

# 下载函数

proc config {sof_file} {

set device_index 0

set device [lindex [get_service_paths device] $device_index]

puts "download..."

device_download_sof $device $sof_file

}

#关闭jtag master服务

proc end_jtag {} {

close_service master $::claimed_path_jtag

}

#写函数

proc jtag_write {addr data} {

master_write_32 $::claimed_path_jtag $addr $data

}

#读函数

proc jtag_read {addr} {

set result [master_read_32 $::claimed_path_jtag $addr 1]

return $result

}

#测试读写

proc test { } {

#地址0中写入1

jtag_write 0x0 0x1

#读取地址0

jtag_read 0x0

}

上电测试

打开System Console

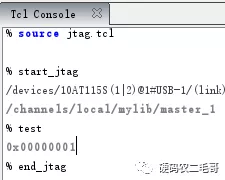

运行如下指令

source jtag.tcl //tcl 脚本

config output_files/test.sof //下载文件

start_jtag //打开jatg master服务

test //测试读写函数

end_jtag //关闭jatg master服务

审核编辑:符乾江

-

FPGA调试中常用的TCL语法简介2022-02-19 3915

-

蜂鸟FPGA开发板和JTAG调试器介绍2021-03-23 1784

-

FPGA中如何通过JTAG固化程序?2021-03-05 6922

-

FPGA——API函数实现JTAG to AXI Master的读写操作2020-09-27 4056

-

JTAG链路同时调试FPGA和HPS电路设计2020-08-08 2371

-

如何编程master fpga的IO引脚来配置目标cpld?2020-03-24 1793

-

Artix7板子中调试FPGA不能启动的问题2020-03-15 4167

-

可以使用ULIK2作为JTAG调试器来调试代码吗?2019-04-26 1343

-

JTAG 链调试程序工具的作用及应用2018-06-20 5047

-

《ARM JTAG 调试原理》下载2011-11-15 968

-

ARM JTAG 调试原理2009-07-14 745

-

JTAG调试原理(推荐)2009-05-27 653

全部0条评论

快来发表一下你的评论吧 !