XILINX偶然加载不成功的问题原因及解决方法

电子说

描述

XILINX偶然加载不成功的问题原因及解决方法

一、项目背景

明德扬(MDY)在2021年承担了多个基于XILINX芯片的研发项目,包括VPX网络透明传输项目(芯片为XC7K325T-2FBG900)、某高端测试仪项目(芯片为XCKU060-FFVA1156)、某网闸设备项目(芯片为XC7Z030-FBG676)等,另外,明德扬自研了基于XC7K325T-2FBG900和基于XC7K410T-2FBG900芯片的核心板,在XILINX研发领域拥有丰富的经验。即使拥有丰富经验和积累,每个新项目我们均要投入相当大的精力去研发。例如本文章分享的案例,在一个研发设备的压力测试中,每隔3分钟对设备进行断电复位重启,部分设备会出现低于1%概率的FPGA加载不成功,重启300多次,会存丰1~3次的加载失败。

为定位此问题,花费了一个多月,先后投入多位专家,最终确定问题的根源是“上电的时序问题”,特为此给大家分享。

二、XILINX的上电启动流程

FPGA上电启动包含三大流程,分别是Setup,Bitstream Loading和Startup Sequence。本次故障的现象是FLASH有概率无法加载,因此定位出现问题的流程是Setup。

在第一阶段的流程中,FPGA首先要上电,其中VCCINT、VCCBRAM、VCCAUX、VCCIO要以由低到高的顺序依次上电。当芯片上电后,电压达到VCCO后在10~50ms内,init_b会拉高,初始化完成,FPGA开始加载配置工作。

但是FPGA上电第一次加载时,与PROGRAM_B信号没有关系,只需要达到init_b的延迟时间,当init_b拉高,FPGA就会加载配置。

三、问题原因:

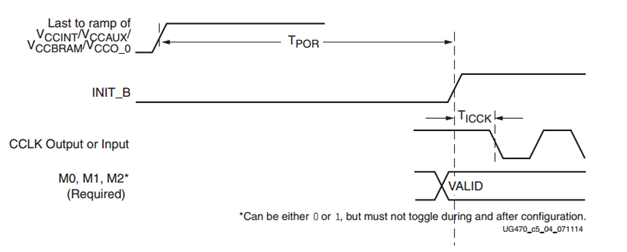

FPGA上电时序图如图1所示,时序要求如表1所示。上电后init_b会延迟10~50ms后拉高,然后CCLK开始输出,加载外部FLASH。通过示波器实测Tpor大约是20ms左右。而且经过反复测量发现,Tpor的延时是相对于VCCINT电压启动后的。

图1:FPGA上电启动时序

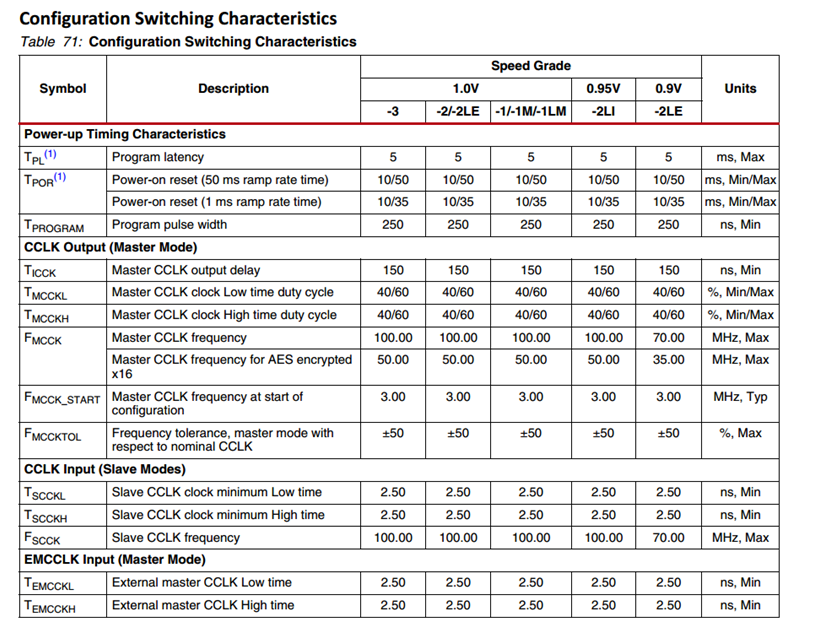

表1:FPGA上电时序要求

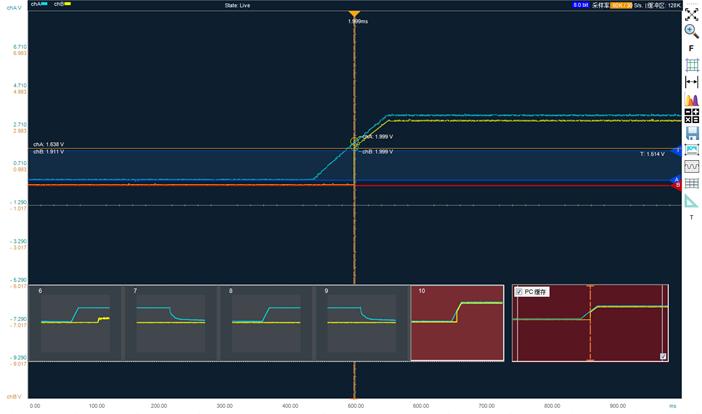

因此,如果FPGA的链路启动时间过长,整个链路启动时间超过50ms的时候,init_b信号的上升沿就会正好卡在3.3V电压启动的过程中,如图2所示。此时FPGA认为已经可以进行加载流程,因此发送CCLK给外部FLASH。但是当前3.3V电压仅爬升到1.9V,还不足以启动FLASH芯片,因此FLASH芯片不会响应,FPGA在得不到FLASH回应后,init_b信号再次拉低,表示FLASH加载过程出现异常。导致连上仿真器发现FLASH没有加载成功。

图2:故障情况下的上电时序(黄线:3.3V 蓝线:init_b)

四、解决方案

1、 减少电源链路启动的时间,将时间控制在50ms以内,同时寻找导通时间更短的MOS管,让3.3V电压爬升的时间缩短至1ms左右。

2、 由于故障的根本原因在于FPGA开始加载FLASH时,3.3V点没有达到FLASH的工作电压,因此可以尝试更换一片宽压FLASH芯片,看看问题能否解决。

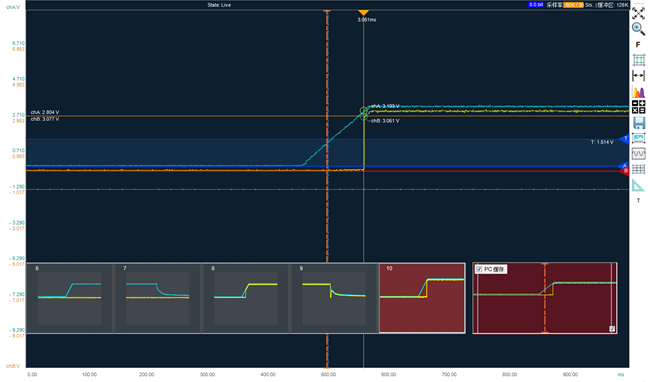

3、 前面两种方案是基于不改版的情况下。如果后期可以改版,还是建议使用PCIE上来的12V电源,来提供整板的供电。所有电压都通过电源芯片进行转换。然后将3.3V电源芯片的PGOOD引脚连接至init_b上。这种方式是人为延迟了init_b跳变的时间,也就是说可以确保3.3V电压稳定之后,再去加载FLASH,这样就可以确保不会出现该故障。而且即使3.3V爬升速率很满,也可以在3.3V电源达到足够大的值之后再加载FLASH。图3就是在类似的板子上做了这样的试验,即使3.3V的上升时间达到了20ms,在init_b跳变的时刻,3.3V电源也已经达到了3.0V的输出,完全可以保证FLASH芯片正常工作。

图3:故障修复后的上电时序(黄线:3.3V 蓝线:init_b)

!!!本问题出现在XC7Z030-FBG676芯片,理论上大部分的XILINX型号均会存在此问题,出现此现象时可以参考。

明德扬(MDY)除了承接项目外,还可为客户提供FPGA芯片、电源芯片、AD芯片等元器件,可找我们了解。

审核编辑:汤梓红

-

PADS9.3不成功原因2011-07-07 5723

-

proteus仿真成功实物不成功具体有什么原因??2011-12-29 5036

-

为什么cpld下载程序不成功2013-07-19 7053

-

cc2640 广播关闭不成功,什么原因?2016-03-29 3165

-

如何去解决STM32 USB转串口驱动安装不成功的问题2021-08-23 1821

-

Imx6Q7cvT08AD的SD卡加载不成功怎么解决2022-01-11 1305

-

XILINX偶然加载不成功的问题原因及解决方法2022-02-24 10664

-

android自动对时不成功的原因有哪几点2022-03-10 2925

-

颠覆格局 盘点12种不成功的智能硬件2015-03-23 1248

-

stm32下载程序解决4线sw下载不成功keil问题2018-10-09 1755

-

PHP教程之PHPstudy安装不成功的解决方案资料说明2019-03-05 1133

-

STC ISP单片机烧录软件下载程序不成功应该如何解决详细方法说明2019-08-09 2430

-

pcb导入不成功?原理图如何进行ID号的复位2020-09-30 6785

-

stm32程序下载不成功2021-11-17 851

-

navicat导入SQL文件不成功2023-11-21 9980

全部0条评论

快来发表一下你的评论吧 !