利用电阻触摸屏和CPLD来实现多点触摸系统的替代

MEMS/传感技术

描述

触摸屏技术概述

触摸屏是成熟的技术,最基本、也是最常用的是4/5线电阻触摸屏。很多标准屏支持多种尺寸,可以选择多种解码模拟解决方案。电阻触摸屏支持多种输入方法,比如手指、触摸笔、手套和指甲等等。电容触摸屏是一种新的解决方案,也有4/5线选择,标准屏比较少,复杂的模拟解码器解决方案也比较少。电容触摸屏比较适合手指的输入,不太适合指甲、触摸笔和手套的输入。电容屏幕最主要的优势是表面耐用性,成熟的电阻和电容触摸屏限于单点触摸。iTouch等产品则采用了多点触摸技术,多点触摸增加了人机接口,并增加了两路以上的同时输入或者触摸点。静态输入触摸的例子有键盘或者游戏手柄上的Shift键和Control、Alt、Delete功能键等,它们都有多路独立的控制;动态输入的例子有手势、命令、旋转动作或者收缩、扩大等等。使用过多点触摸技术以后,传统的触摸技术就显得太简单了。

目前,可以使用到多点触摸技术的应用包括医疗影像(超声、X射线和MRI在进行图像处理时需要用到)、信息查询终端 (相片打印、零售信息查询终端、地图/导航等)、音乐/视频播放器(iTouch)、家电等。本文将介绍一个使用数字电阻触摸屏和MAX II CPLD来实现多点触摸系统的简单数字低成本替代方案。

多点触摸解码

任何多点触摸解决方案都从触摸屏开始。文中的例子使用NKKSwitch的数字SmartTouch,型号为FTAS225-5.7A-N。还有别的供应商提供的尺寸不同的其他数字电阻屏。处理接口是I2C,但也可以使用其他接口。

FTAS225-5.7A-N采用了5.7”叠层屏幕,15行×15列,触点分辨率为5mm×7mm。屏幕叠层实际上是15×15的开关矩阵。数字电阻屏叠层使用水平和垂直的铱锡氧化物(ITO)走线。走线之间是分开的,触摸时会使两层短路。

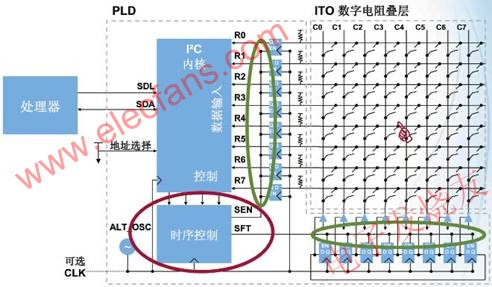

在此次演示中,设计简化为8×8数字电阻触摸屏。本例子使用了处理器I2C接口,但是也可以为任何处理器提供任意串行或者并行接口。该设计只需要MAX II将数字电阻触摸屏与处理器连接起来,利用MAX II内部上拉电阻和内部振荡器减少外部元件。

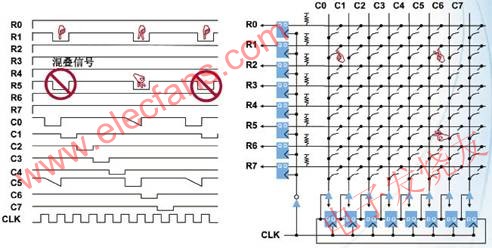

在图1中,垂直寄存器在每一列为每一行进行采样,水平寄存器组成了移位寄存器,阵列每次都被驱动为低电平。图中波形显示了没有触摸时屏幕是怎样解码的。当屏幕上没有点被触摸时,行探测信号保持高电平。当屏幕上第2行第2列被触摸时,导致第二行在C2采样期间被拉低。每次扫描显示屏时,I2C模块向处理器发送8字节数据。

表1 触摸屏的优缺点

图1 单点触摸解码的工作模式

多点触摸解码是怎样工作的呢?图2中的波形显示了三个触点。图中的手指符号表示每一个触点是怎样映射到行列采样信号的。三个触点导致扫描期间出现3个低电平脉冲。在某些3手指触摸条件下,简单解码器会错误地报告出现混叠信号,而后者是不正确的触点解码。3个触点必须呈三角形,其中两个点共享一行,两个点共享一列。图中的红圈画线显示了混叠信号解码脉冲。

图2 多点触摸解码的工作模式

改进后的解码器电路可以减小甚至消除混叠信号。首先,我们要做的是时钟速率提高,通常将时钟速率提高10-100倍。在图3中,I2C时钟从100kHz提高到4MHz。增加了同步移位和采样使能信号(绿色)。 SFT是移位使能信号,SEN是采样时能信号。加入了时序控制模块,支持SFT至SEN延时调整(红色),支持移位使能信号对使能延时调整进行采样。时序控制模块能够减小移位使能采样,使能延时可以增大移位使能。采样使能延时独立地控制每一列、每一行延时。

图3 改进后的电路减小了混叠信号(1)

电路是怎样去掉混叠信号的呢?在实际系统中并没有调整时序,时钟更快一些。RA到RE详细显示了产生混叠信号的触摸屏通路,包括ITO走线阻抗、I到RE。I到RE详细阐述了产生混叠信号的触摸屏通路。由于采用了电阻,从手指触点1到混叠信号脉冲的延时比较大,因此,控制采样使能时序会忽略它。如左下部的箭头所示,通过改进采样使能信号,可以消除混叠信号。图5详细显示了延时和时序变化。时钟频率还是比实际例子慢,以方便理解该图。第0列和第5列的采样时序不同,以消除混叠信号。虽然C5 SEN信号比C0 SEN信号滞后,但还是比最初设计短得多。设计人员的目标是根据触摸屏和PCB特性,使每一列和每一行的采样时序足够长,能够正确采样真正的触摸;同时采样时序还要足够短,从而可以忽略混叠信号。利用MAX II器件的可编程能力,使用JTAG可以迅速重新配置设计或者动态进行控制,很容易对电路进行调整。

图4 改进后的电路减小了混叠信号(2)

图5 改进后的电路减小了混叠信号(3)

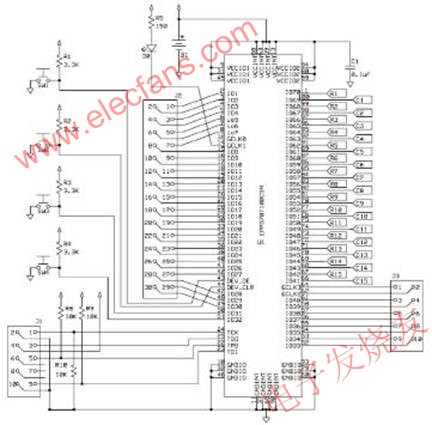

参考设计电路板非常简单(图6)。只需将MAX II器件直接连接至触摸屏的30个引脚,以及15×15 LED阵列。还有下载连接线J1,以及SPI或者I2C连接用的扩展插头J3。相对于I2C接口,LED阵列更容易进行交互式演示。

图6 演示电路板原理图

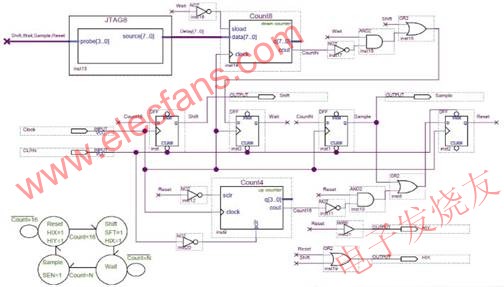

图7是MAX II电路结构图。它包括移位寄存器,含有来自时序控制模块的移位控制信号。时序控制模块还控制采样寄存器。为能够有效地演示时序变化的影响,将使用JTAG源探测特性Mega向导以及Quartus II和MAX II系列支持的源探测编辑器。

图7 MAX II电路结构图

如图8所示,时序控制模块有4个状态,显示在左下角。“复位”驱动所有引脚为高电平,建立时间为16个时钟周期。“移位”将列扫描移到左侧。“等待”是从移位到采样的可编程延时。JTAG8模块控制延时,是从JTAG电缆下载的8位数值,控制来自Quartus源探测编辑器窗口。它还对内部节点进行采样,以便在Quartus中实时读取。“等待”周期后,采样状态采集列数据。

图8 时序控制模块

MAX II是可编程逻辑器件,很容易采用免费的Quartus II设计工具对其进行定制,满足使用者的应用需求。同时,MAX II CPLD具有以下特性,非常适合数字电阻触摸屏解码:大量的I/O引脚,其中超低功耗MAX IIZ系列含有160个I/O,MAX II系列含有272个I/O,很少有处理器提供足够的I/O来解码数字电阻触摸屏;所有MAX II器件都有内部振荡器和可编程内部I/O上拉电阻;MAX II器件支持在系统可编程,这样可以先设计印刷电路板,然后再调整时序;MAX II的功耗非常低,MAX IIZ适用于很多电池供电的便携式应用;最后,可编程MAX II能够灵活的支持需要标准或者专用接口的处理器。

欢迎转载,本文来自电子发烧友网(http://www.elecfans.com/)

-

电阻式触摸屏是利用什么进行控制和工作的2024-01-23 3637

-

电容触摸屏原理 电容触摸屏和电阻触摸屏有什么区别2024-01-22 8578

-

STM32 SPI驱动触摸屏(XPT2046)(上)2023-07-22 7392

-

电阻触摸屏的检修方法2020-06-26 6362

-

电阻式触摸屏多点触摸技术的原理分析2020-01-23 4940

-

多点触摸屏是什么意思_多点触摸屏原理2019-10-01 17974

-

电阻触摸屏和电容触摸屏哪个更具有优势2019-07-08 16371

-

电阻式触摸屏校准算法的优化_电阻式触摸屏工作原理2018-01-21 11741

-

触摸屏与多点触控技术2012-07-26 2578

-

基于MMSE的触摸屏应用多点校准算法2011-11-28 765

-

详解多点电容触摸屏的设计挑战2011-11-17 2610

-

四线电阻触摸屏,四线电阻触摸屏原理和特点有哪些?2010-03-24 1743

全部0条评论

快来发表一下你的评论吧 !