CY8C20xx6A设计的1.8V CapSense触摸技术

嵌入式设计应用

132人已加入

描述

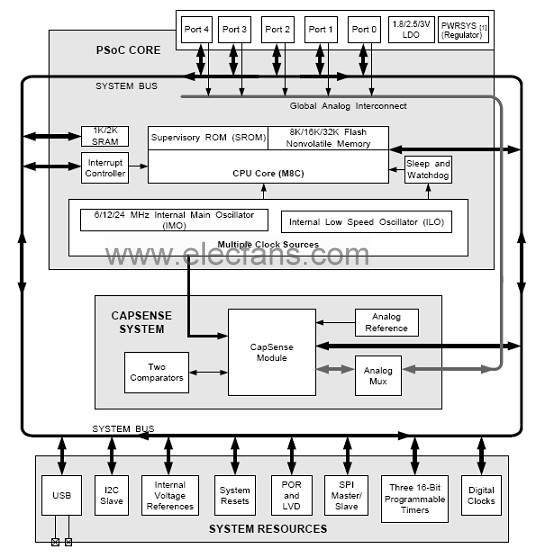

本文介绍了CY8C20xx6A主要特性,逻辑方框图,CapSense系统方框图以及通用CapSense控制套件电路图。

Cypress公司的CY8C20xx6A 是最新和最低功耗的1.8V CapSense解决方案,工作电压1.71V 到 5.5V,采用低功耗 CapSense® 模块,可配置的电容式感测元件和支持组合使用 CapSense 按钮、滑条、触摸板、触摸屏和接近传感器,M8C 处理器的速度最高可达 24 MHz,主要用于以电池为能源的手持设备,移动设备,蓝牙手持设备以及打印机,LCD TV和监视器等。

■ 1.71V 到 5.5V 工作电压

■ 低功耗 CapSense® 模块

❐ 可配置的电容式感测元件

❐ 支持组合使用 CapSense 按钮、滑条、触摸板、触摸屏和接近传感器

■ 强大的 Harvard 架构处理器

❐ M8C 处理器的速度最高可达 24 MHz

❐ 速度高、功耗低

❐ 中断控制器

❐ 温度范围:-40℃ 至 +85℃

■ 灵活的片上存储器

❐ 3 个程序/数据存储器容量选项:

・ CY8C20x36A:8K 闪存/1K SRAM

・ CY8C20x46A、CY8C20x96A:16K 闪存/2K SRAM

・ CY8C20x66A:32K 闪存/2K SRAM

❐ 50,000 次闪存擦/写循环

❐ 局部闪存更新

❐ 灵活的保护模式

❐ 系统内串行编程 (ISSP)

■ 全速 USB

❐ 仅在 CY8C20646A、CY8C20666A 和 CY8C20x96A 上提供

❐ 符合 12 Mbps USB 2.0 标准

❐ 8 个单向端点

❐ 1 个双向控制端点

❐ 专用的 512 字节缓冲区

❐ 在 3.3V 时采用内部稳压调节

■ 高精度、可编程时钟

❐ 内部主振荡器:6/12/24 MHz ± 5%

❐ 供看门狗和睡眠定时器使用的 32 kHz 内部低速振荡器

❐ 供可选外部晶振使用的高精度 32 kHz 振荡器

❐ 不带外部组件时,USB 振荡器的精度为 0.25%

(仅限 CY8C20646A、CY8C20666A 和 CY8C20x96A)

■ 可编程引脚配置

❐ 多达 36 个 GPIO(具体取决于封装)

❐ 双模式 GPIO:所有 GPIO 都支持数字输入/输出和模拟输入

❐ 所有 GPIO 均具有 25 mA 的灌电流能力

❐ 所有 GPIO 均可选择上拉驱动、High Z 驱动、开漏驱动模式

❐ 端口 0 和 1 采用 CMOS 驱动模式(5 mA 源电流):

・端口 0 的源电流总和为 20 mA(在 3.0V 时)

・端口 1 的源电流总和为 20 mA(在 3.0V 时)

❐ 端口 1 上具有可选的稳压数字 I/O

❐ 端口 1 的输入阈值可配置

❐ 所有端口 1 GPIO 上都具有热插拔能力

■ 通用模拟复用器

❐ 通用内部模拟总线

❐ I/O 的同步连接

❐ 高 PSRR 电压比较器

❐ 用于所有模拟资源的低压差电压调节器

■ 额外的系统资源

❐ I2C 从器件:

・有 50 kHz、100 kHz 或 400 kHz 可供选择

・无需时钟伸展(在大多数情况下)

・在睡眠模式期间实现,电流不超过 100 µA

・硬件地址验证

❐ SPI™ 主控和从器件:可在 46.9 kHz 到 12 MHz 的范围内进行配置

❐ 3 个 16 位定时器

❐ 看门狗和睡眠定时器

❐ 内部电压参考

❐ 集成监控电路

❐ 8 到 10 位增量型模数转换器

❐ 2 个通用高速低功耗模拟电压比较器

■ 完善的开发工具

❐ 免费的开发工具 (PSoC Designer™)

❐ 功能齐全的在线仿真器和编程器

❐ 全速仿真

❐ 灵活实用的断点结构

❐ 128K 的跟踪存储器

■ 封装选择

❐ CY8C20x36A:

・ 16 引脚 3 x 3 x 0.6 mm QFN

・ 24 引脚 4 x 4 x 0.6 mm QFN

・ 32 引脚 5 x 5 x 0.6 mm QFN

・ 48 引脚 SSOP

・ 48 引脚 7 x 7 x 1.0 mm QFN

❐ CY8C20x46A:

・ 16 引脚 3 x 3 x 0.6 mm QFN

・ 24 引脚 4 x 4 x 0.6 mm QFN

・ 30 脚 WLCSP

・ 32 引脚 5 x 5 x 0.6 mm QFN

・ 48 引脚 SSOP

・ 48 引脚 7 x 7 x 1.0 mm QFN(带 USB)

❐ CY8C20x96A:

・ 24 引脚 4 x 4 x 0.6 mm QFN(带 USB)

・ 32 引脚 5 x 5 x 0.6 mm QFN(带 USB)

❐ CY8C20x66A:

・ 32 引脚 5 x 5 x 0.6 mm QFN

・ 48 引脚 7 x 7 x 1.0 mm QFN(带 USB)

・ 48 引脚 SSOP

・ 30 脚 WLCSP

图1。CY8C20xx6A逻辑方框图

图2。CY8C20xx6A CapSense系统方框图

CY3280-20x66通用CapSense控制套件

CY3280-20x66 Universal CapSense Controller Kit

The CY3280-20X66 CapSense Controller Kit is designed for easy prototyping and debug of 20xx6A CapSense Family designs with pre-defined control circuitry and plug-in hardware. Programming hardware is included as well as an I2C-to-USB bridge for tuning and data acquisition. This module connects to any CY3280 Universal CapSense Module Board.

CY3280-20x66 Kit Content:

CY3280-20x66 CapSense Controller Board

CY3240-I2USB Bridge

CY3210 MiniProg1 Programmer

USB 2.0 Retractable Cable

CY3280-20x66 Kit CD

图3。CY3280-20x66通用CapSense控制套件外形图

图4。通用CapSense控制套件电路图

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- CY8C20xx6A

-

如何在芯片CY8C20xx6A上制作PS2键盘CapSense?2019-03-15 0

-

如何测量降低的CY8C20XX7能耗2019-07-29 0

-

CY3280CapSense控制器套件专为简化20xx6A CapSense系列的原型设计和调试而设计2020-06-18 0

-

12V to 1.5V 10A and 1.8V 10A c2008-10-22 1005

-

PSoC 1 可编程片上系统CY8C21123_CY8C21223_CY8C21323_001-63473_0A_V_ZH2017-10-10 821

-

CapSense 可编程片上系统CY8C20234_001-63505_ZH2017-10-10 795

-

CY8CMBR2044 CapSenSe Express2017-10-10 660

-

CapSense CY8C20xx6A 的主机源串行编程-AN593892017-10-10 616

-

3.3V和3V降压到1.8V的芯片和LDO方案说明2020-11-30 2766

-

LTC3887 Demo Circuit - High Efficiency Dual 500kHz 3.3V/1.8V Step-Down Converter (6-24V to 3.3V & 1.8V @ 15A)2021-02-04 667

-

LTM4637 Project - 20A Step-Down μModule Regulator (4.5-20V to 1.8V @ 20A)2021-02-22 544

-

LTM4639 Project - Low Vin, 20A Step-Down μModule Regulator (2.4-7V to 1.8V @ 20A)2021-02-22 537

-

LTC3883演示电路-带电感DCR电流感应的高效425 kHz 1.8V降压转换器(6-24V至1.8V@20A)2021-06-05 534

-

LTM8028演示电路-低输出噪声、1.8V、5A降压稳压器(6-36V至1.8V@5A)2021-06-10 741

全部0条评论

快来发表一下你的评论吧 !