基于Type-C的USB4及DP 2.1等新技术的测试

描述

自从USB-IF协会于2014年发布新一代接口Type-C,其优异的性能,极简连接以及可扩展和多功能立刻受到整个业内消费者的瞩目,近几年Type-C技术更是凭借以上的诸多优点,在消费类电子行业得到蓬勃发展,其特点总结如下:

•极简连接:相比之前A/B口可以实现约8.3mm x 2.5mm小尺寸、扁平轻薄、支持正反连接;

•可扩展性:可用于不同终端设备诸如电脑,手机,显示器,U盘,扩展坞等等;

•多功能性:支持USB 2.0、USB 3.2、USB4、DP 1.4a、DP 2.0/2.1、PCIe和PD功能;

•生态多样:包括芯片和终端产品,比如台式机及笔记本、手机、扩展坞、U盘、显示器、嵌入式板卡、无源线缆、有源线缆等。

从2014年8月USB-IF协会初次发布USB Type-C技术规范支持USB2.0、3.1和PD 2.0,历经多年迭代更新,Type-C目前已经可以支持USB4、DP 2.1等新技术,其研发及测试的复杂度也随之大幅提高,下面的篇幅,我们就和大家分别介绍基于Type-C的USB4及DP 2.1等新技术的测试概览。

USB4技术

谈到Type-C,先谈谈USB4技术。USB-IF协会在2019年3月宣布开发新技术,同年9月发布USB4规范,时间如此之短,得益于借鉴了Intel贡献的TBT3技术(是德科技多年前已发布TBT测试相关的软硬件方案)。

USB4是面向互连的技术,相比USB 3.2技术更加复杂,其一,可利用现有USB Type-C线缆,但需注意线缆不同带来的损耗差异,若要支持2通道bonding/40Gbps,则需使用经过USB4认证的线缆,其二,借助隧道技术承载多协议,支持时间同步、带宽动态分配等机制,其三,可以兼容USB 3.2、USB 2.0等,其四,更高速率使得收发架构更复杂,体现在电气子层复杂的发送加重和接收均衡机制,逻辑子层使用precoder和fec技术,降低DFE可能引起的突发连续错误,提高鲁棒性。

再介绍USB Type-C连接器和线缆,它承载USB4数据,是设计、测试的重要部分。2014年8月USB-IF协会初次发布USB Type-C技术规范,支持USB 2.0、USB 3.1和PD2.0,历经多年迭代更新,2019年8月发布v2.0版本新增支持USB4,2021年5月发布v2.1版本新增支持USB PD 3.1扩展功率能力。

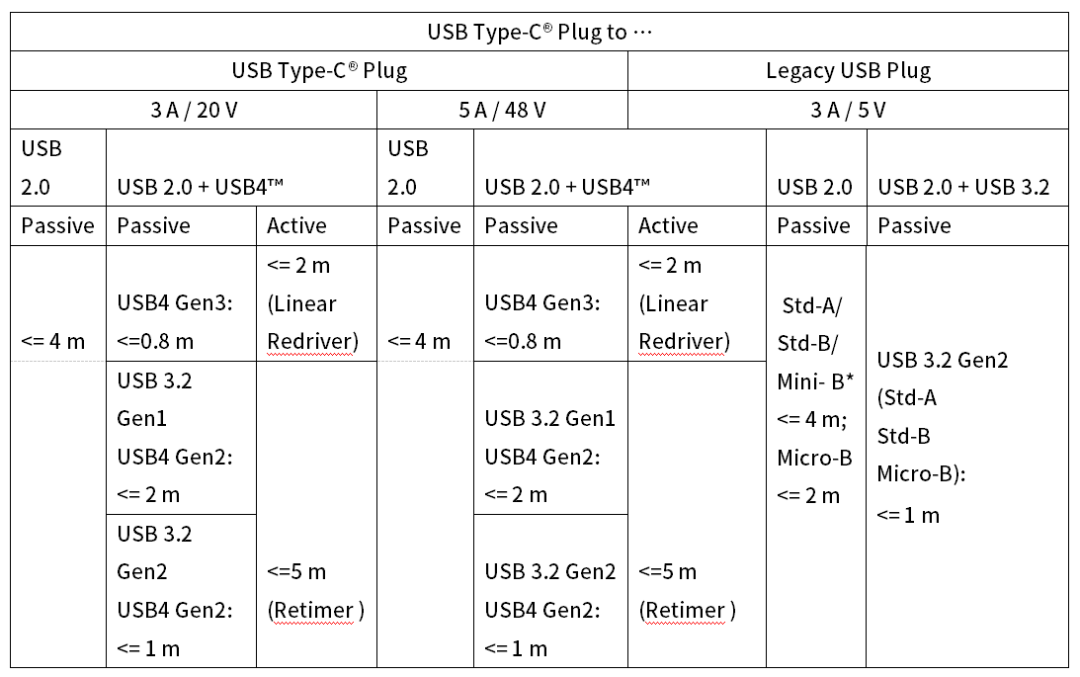

Type-C连接器和线缆在高速收发互连中起到非常重要的作用,如下展示了USB Type-C线缆和传统USB线缆在电源、信号速率、线缆长度方面的特点,电源方面USB Type-C连接器电流可到5A,Type-C线缆若支持USB PD标准功率范围那么可达3A/60W,若支持扩展功率范围(必须具备电子标签)那么可达5A/240W;线缆类型方面为方便USB4终端产品扩展支持显示等应用通过使用redriver或retimer实现有源线缆,延长传输距离,提高用户体验;信号速率方面速率更高相对损耗更大同样材质线缆传输距离变短,USB 2.0 Type-C线缆支持480Mbps,可实现至多4m传输距离,USB4 速率提升至单lane 20Gbps,使用无源线缆传输距离仅0.8m,另外相同传输速率USB 3.2 Gen2 10Gbps和USB4 Gen2 10Gbps,由于遵循标准的系统链路损耗budget不同,传输距离也有所差异。

*Mini B:500mA

图:USB Type-C与传统USB线缆差异对比

最后谈谈规范与测试。USB4规范为芯片和产品设计提供了重要参考,为保证良好品质,提高稳定性,保证兼容,并支持新功能等要进行认证,认证需要进行多种一致性测试(参考“USB4 认证测试”),USB4物理层电气一致性测试是其中重要一环。该一致性测试规范CTS历经0.96、1.0、1.01不同版本,目前最新的是2021年7月发布的1.02版本,更新了Clock Switch测试项。

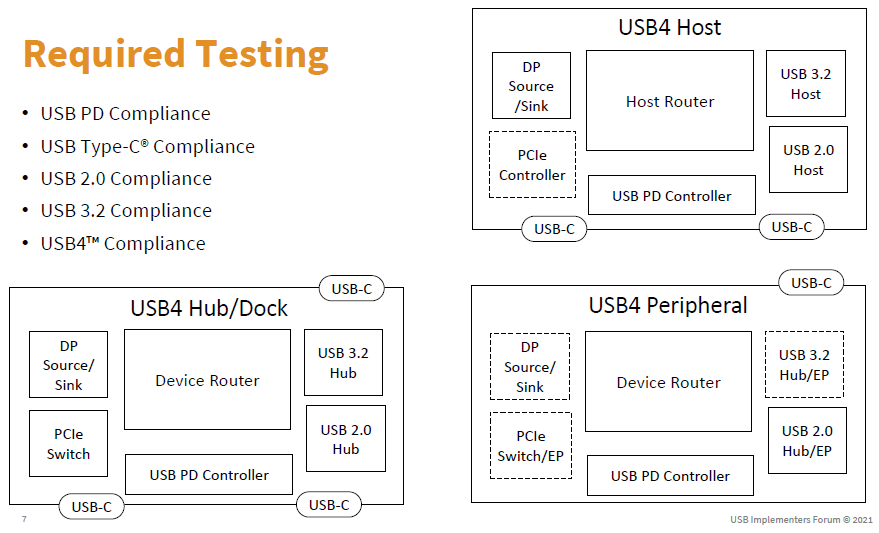

图:USB4 认证测试(摘自www.usb-if.org)

USB4工作原理与测试难点

USB4是通过USB Type-C实现互连的技术,在树型拓扑结构中支持多达6个Routers,通过隧道技术实现USB3、PCIE、DP多种协议传输,同时兼容TBT3技术的产品,因此USB4技术复杂。

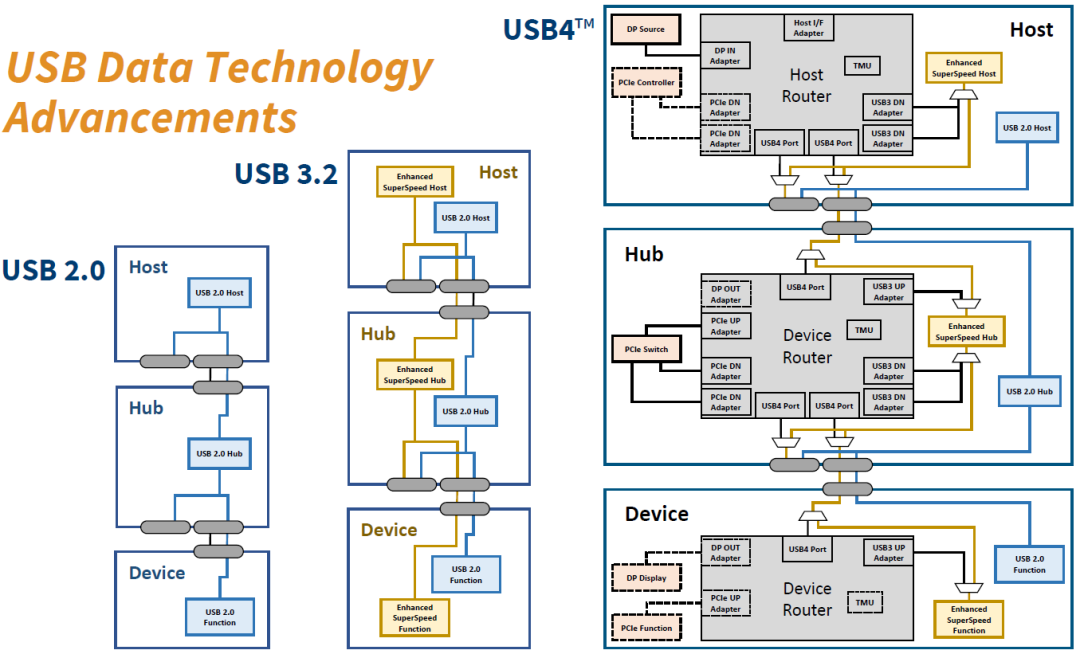

USB4相比USB 3.2,相同点是两者都支持主机和各种外设进行数据交换,不同点是USB4允许主机建立外设之间的数据交换,USB4面向连接、实现隧道架构,通过协议适配器将USB3、DP、PCIE等数据包放入隧道中,各协议可以独立工作(经传输层和物理层),也可通过CM(Connection Manager)实现带宽管理,通过TMU实现时间同步。Router是USB4的核心,有Host router和Device router两种类型,包括一个支持点到点、可配置开关,可在双方适配器之间建立单向逻辑连接。

以典型USB4 Host为例,内部组成包括1个Host Router、1个USB 2.0 Host、1个USB 3.2 Host、1个DisplayPort Source,可选支持PCIE controller,接口速率方面必须支持20G Gen2 x2,可选支持40G Gen3x2,对外物理接口典型支持2个Port,至少一个必须支持DFP,功能上支持Tunnel技术承载来自于DP source、PCIe Controller、SuperSpeed Host的DP、PCIe、USB3.0数据包,支持USB2.0 Host功能,可选兼容TBT3产品和USB Type-C Alternate Mode产品(参考“USB 2.0/USB 3.2/USB4数据技术对比”),USB4功能复杂。

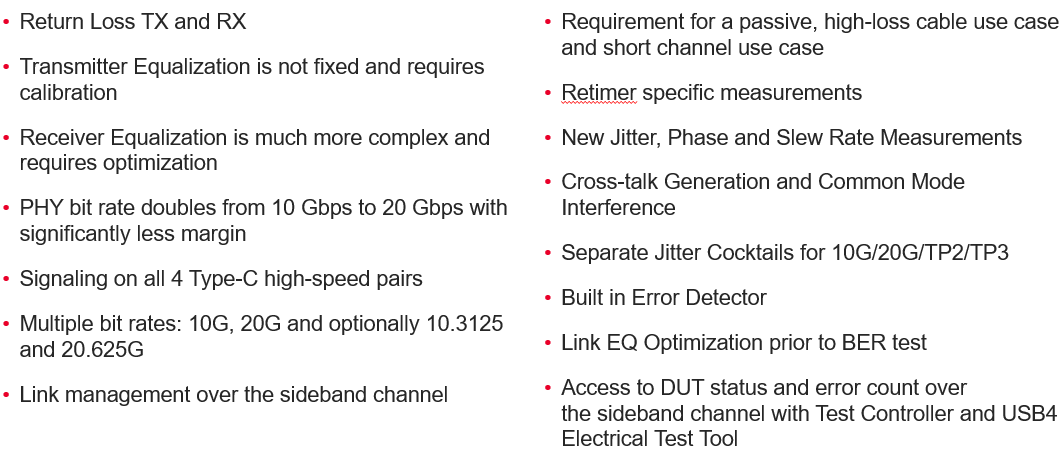

使用复杂技术的产品进行物理层电气一致性测试难点多,参考“USB4技术变化”,涉及测试点、收发架构、测试模式、测试码型、测试参数,另外还有线缆/连接器等变化带来的测试挑战。

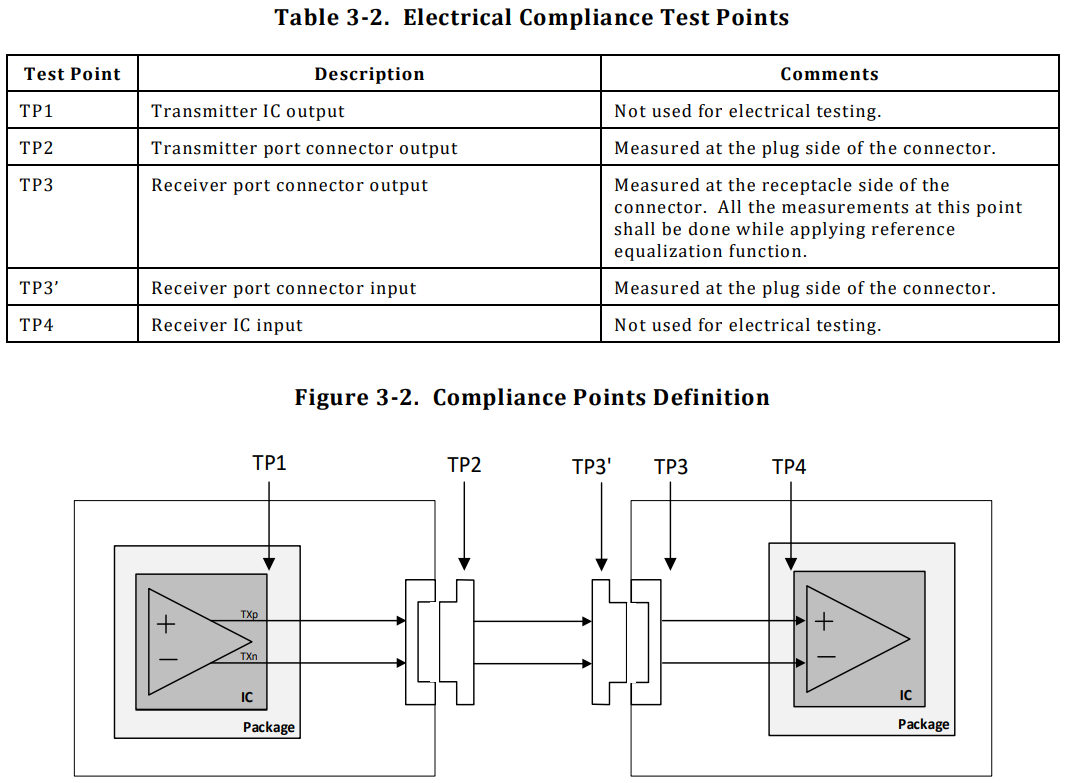

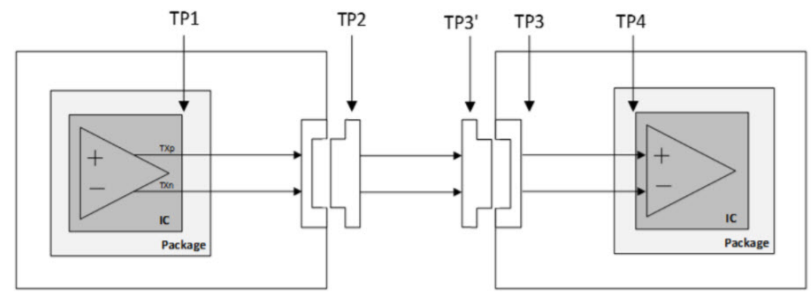

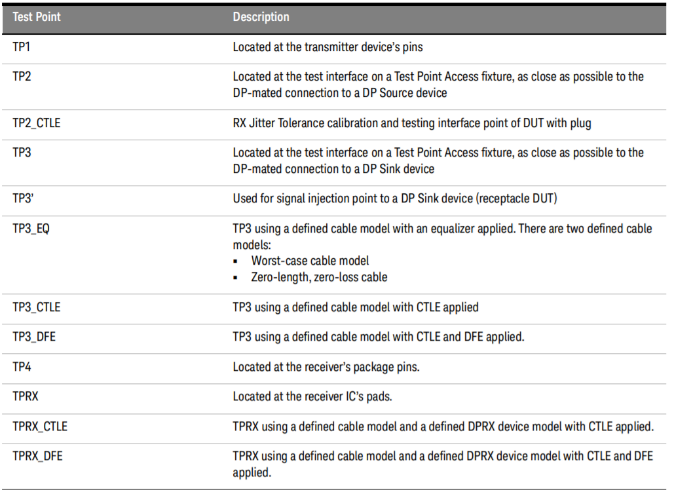

其一,要明确电气一致性测试点,TP1是IC芯片引脚,这个位置通常无法直接探测,对于发送一致性测试,测试组网环境仅一种,选择TP2(以终端PC为例,用插头夹具测量)和TP3(示波器中嵌入S参数文件,支持2m和0.8m两种cable的S参数),对于接收一致性测试来需要选择TP3’和TP3,不正确选择测试点会影响测试结果,如下是USB4规范提及的测试点说明:

图:USB4物理层电气一致性测试点

其二,物理电气子层发送加重和接收均衡更复杂。发送支持16种不同presets,通过3个系数的FIR滤波器实现,接收支持CTLE和DFE,参考CTLE支持10种模板,可“补偿”高频损耗,参考DFE是1个抽头的滤波器,可修正码间干扰影响,该抽头调整系数限制调整电压幅度在50mV以内。

其三,测试模式不同,相比USB 3.2,USB4产品都需要硬件控制器借助USB ETT软件工具配置DUT产生测试码型和实现误码率测试。

其四,测试码型复杂,相比USB 3.2,USB4产品要支持并能产生SQ128、PRBS15、PRBS31、SQ2、SQ4、Electrical Idle mode等测试码型。

其五,测试参数复杂,相比USB 3.2,USB4产品测试要进行时域、频域和BER多方面测试。从时域角度看,支持10Gbps、20Gbps,可选10.3125bps、20.625Gbps;取消LFPS码型测试,需要去嵌夹具到示波器那段射频线缆;由于收发架构复杂,Tx一致性测试需要验证16种presets的Pre-shoot/de-emphasis,P15还需要验证Swing,增加UI、SSC Phase Deviation(Phase jitter)、Tx Freq Variation Training(仅在包含retimer时需要、考察本地时钟和恢复时钟切换),TJ(要外推到1E-13)、UJ、UDJ、LF-UDJ、DDJ、DCD Jitter(EOJ)、Eye mask(其中Gen3 TP3眼张开度在98mV/27ps对仪器底噪和抖动要求较高)、增加AC Common mode。

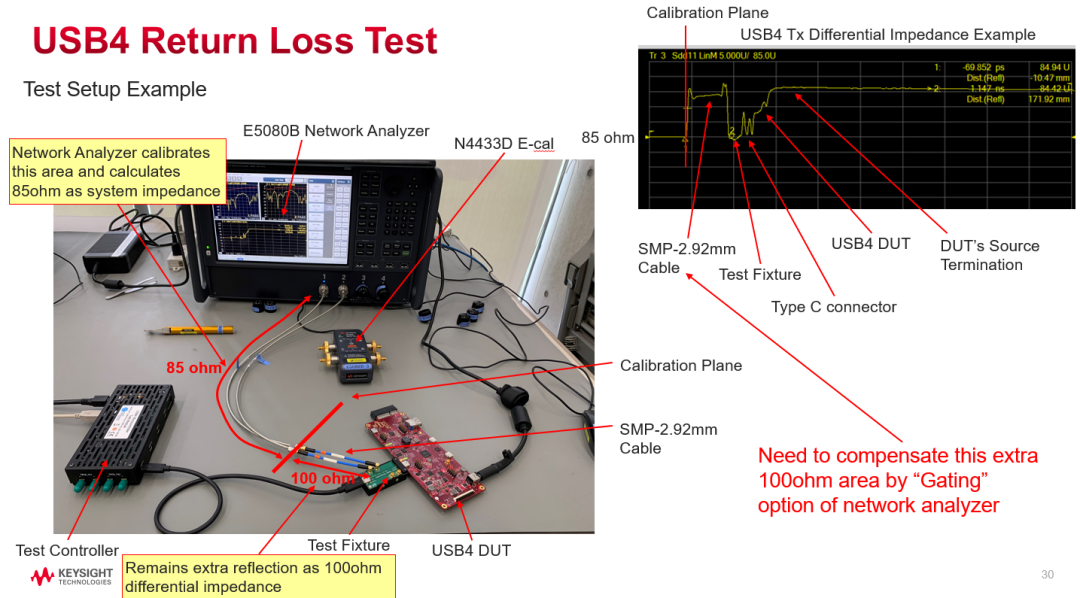

从频域角度看,增加SDD11和SCC11,SDD11表示差分回波损耗,要通过板级设计约束Tx和Rx差分阻抗,消费类电子产品除交流耦合电容、对地放电电阻外,还会增加防护器件,这对该项测试提出了挑战,SCC11表示共模回波损耗,要约束并考虑单端阻抗。

从BER测试看,Rx一致性测试时需要通过SBTRX信号配置被测件进入测试模式并使能内置error counter计数器,测试需要构建case1和case2不同损耗场景,这个损耗需要通过20GHz频率范围的矢量网络仪器E5080B进行标定,实时示波器校准case1和case2不同场景下的压力参数,case1场景下找到DDJ最小的Preset并以此校准AC CMSI、RJ、PJ并验证TJ(可调整RJ或PJ)最终找到符合标准的最小眼张开度的参数(可调整幅度),case2场景类似,在case1和case2场景下连接到DUT进行未编码的误码率测试,这里通过读取DUT内部error counter计算误码率是否符合10-12要求。

其六,同一个物理端口支持不同标准、不同线损,挑战很大。谈到损耗,对比USB 3.2和USB4损耗(参考“USB 3.2与USB4损耗分配对比”),以Type-C到Type-C互连为例,USB 3.2 10G要求目标总损耗是23 dB,Host/Cable/Device分配是8.5、6、8.5,USB4 10G目标总损耗相同,Host/Cable/Device分配不同(5.5、12、5.5),USB4 20G目标损耗是22.5,Host/Cable/Device分配是7.5、7.5、7.5,更高速率要克服“长链路”影响,链路包含DIE的负载、封装、过孔、走线、连接器、线缆等,会引入阻抗匹配、码间干扰、串扰等影响,芯片、板卡等设计挑战大。

图:USB 2.0/USB 3.2/USB4数据技术对比(摘自www.usb-if.org)

| TypeIL(Type-C) | Host* | Cable | Device* | Total |

| USB 3.2 Gen2 (10 Gbps) | 8.5 dB | 6 dB | 8.5 dB | 23 dB |

| USB4 Gen2 (10 Gbps) | 5.5 dB | 12 dB | 5.5 dB | 23 dB |

| USB4 Gen3 (20 Gbps) | 7.5 dB | 7.5 dB | 7.5 dB | 22.5 dB |

*Host/Device损耗涉及从Die到连接器中间所有的东西

图:USB 3.2与UBS4目标损耗对比

图:USB4技术变化

USB4物理层测试方案

谈到USB4物理层电气一致性测试,发送、接收、互连通道都需要关注。

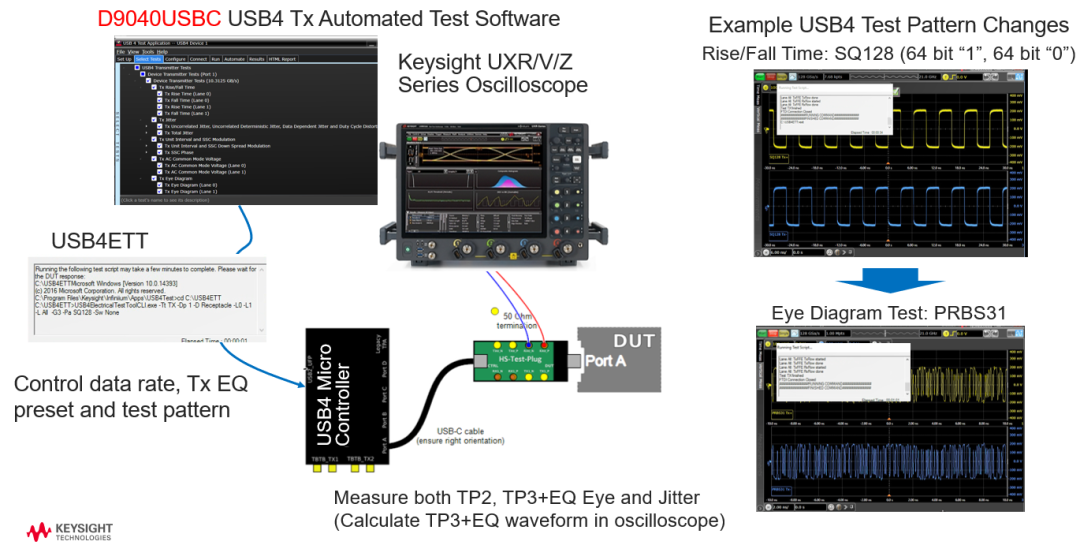

USB4发送端一致性测试,要在TP2和TP3进行测量和计算。相比USB 3.2除眼图、SSC、TJ、RJ、DJ外,值得注意USB4规范采用了不同的抖动分解方法:TJ分解为UJ(计算/TJ-DDJ)和DDJ(测量),UJ分解为RJ(测量)和UDJ(计算/UJ-RJ),另外还有DCD jitter(EOJ)、LF-UDJ、Phase Jitter、Tx Freq Variation、Sdd11/Scc11等相关的测试项目,如下图是发送端的测试组网图:

图:USB4发送端电气一致性测试组网

图:USB4端口回波损耗测试组网

是德科技研发的D9040USBC软件支持Host、Device等不同类型DUT,支持1端口或2端口,每端口可支持1个lane或2个lane,支持10Gb/s、20Gb/s和TBT3的10.3125Gb/s、20.625Gb/s.不仅支持调试,而且可以搭配USB4控制器和USB ETT工具软件进行自动化测试,极大提高效率,可以输出包含测试裕量、测试门限和参考测试源的报告。

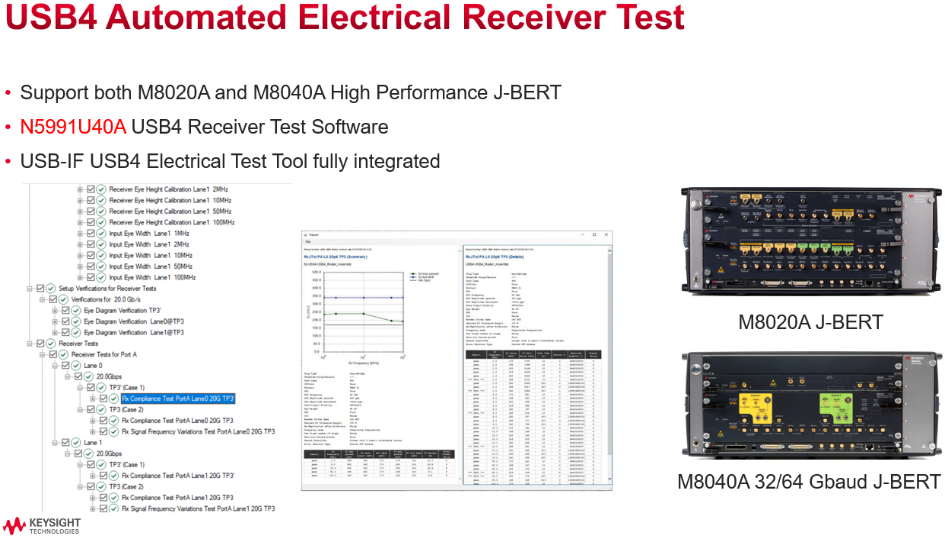

对USB4接收端一致性测试而言,基于M8020A/M8040A误码仪和N5991U40A软件的自动校准、测试的平台,支持USB4 Router、TBT3 Host、TBT3 Device不同类型的DUT,支持10Gb/s、20Gb/s、10.3125Gb/s、20.625Gb/s 4种速率,支持case1、case2场景,支持BER测试、Multi Error-Busrt测试、Signal Frequency Variation Traing测试等,另外还支持专家模式,可以实现调测、抖动容限、灵敏度、定制BER测试等,如下是接收端的测试组网图:

图:USB4接收端电气一致性测试组网

校准和接收BER测试时,相比USB 3.2,USB4有诸多不同点,新增AC CMSI noise(100mVpp@400MHz)压力参数,修改了SSC参数(32kHz@+300ppm~-5300ppm),支持2m和0.8m两种无源线缆构建的场景case1和case2,两种场景对应的channel loss分别是18~19dB@5GHz和16~17dB@10GHz,需要用到20GHz矢量网络分析仪进行标定,在case1和case2场景下开启SSC校准压力参数涉及DDJ、AC CMSI、RJ、PJ、TJ和Eye,精确校准是测试基础,BER测试方法也不同,调用校准参数,误码仪使用校准中选用的Preset和DUT沟通,USB4控制器通过USB ETT软件使用SBTRX信号配合高速链路进行链路协商,误码仪根据协商情况选择合适的Preset,之后检查DUT内部error counter计数器是否正常,并完成计数器清零,最后进行误码率测试(完成PJ:1MHz/2MHz/10MHz/50MHz/100MHz@1E-12)。

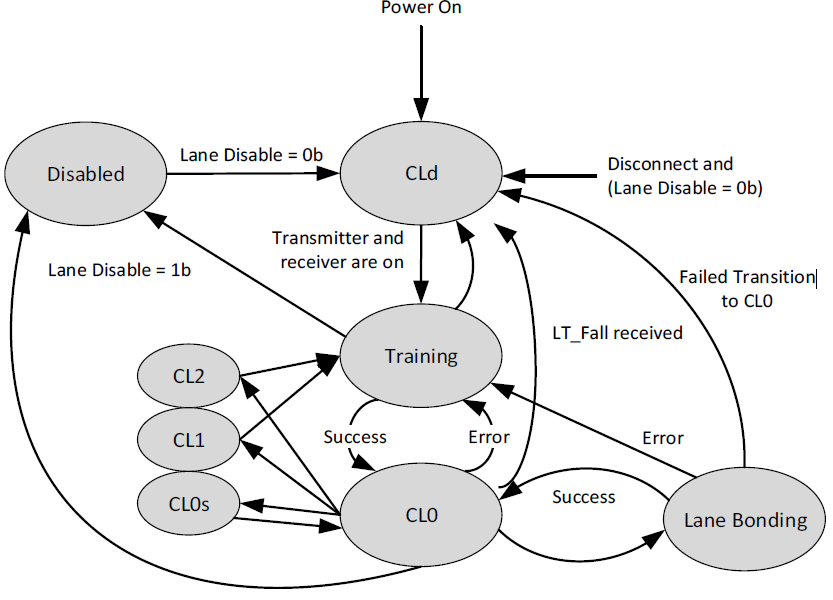

物理层除电气子层外还有逻辑子层,对于芯片和终端产品调试还需了解电路上电lane初始化和链路建立情况,这就需要熟悉逻辑子层的状态机(参考“USB4逻辑子层状态机”)包含Disabled、CLd、Training、CL0、Lane Bonding和Low Power这6个状态,其中CLd中涉及lane初始化相关,Sideband Channel(SBTx和SBRx信号/1Mbps)借助3类事务完成初始化,初始化包括5个阶段:P1-初始条件确定、P2-Router探测、P3-USB4端口特性确定、P4-lane参数同步和发送开始、P5-lane均衡。

图:USB4逻辑子层状态机

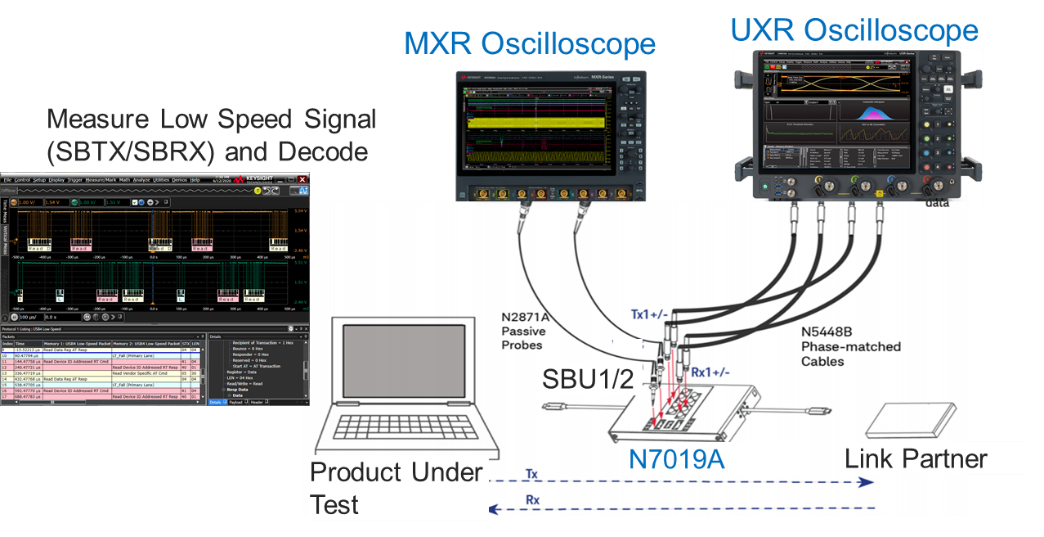

基于MXR/V/Z/UXR示波器平台,借助N7019A硬件和D9010USBP软件实现对USB4逻辑子层的解析和触发设置等,如下图:

图:USB4.0协议解析与触发

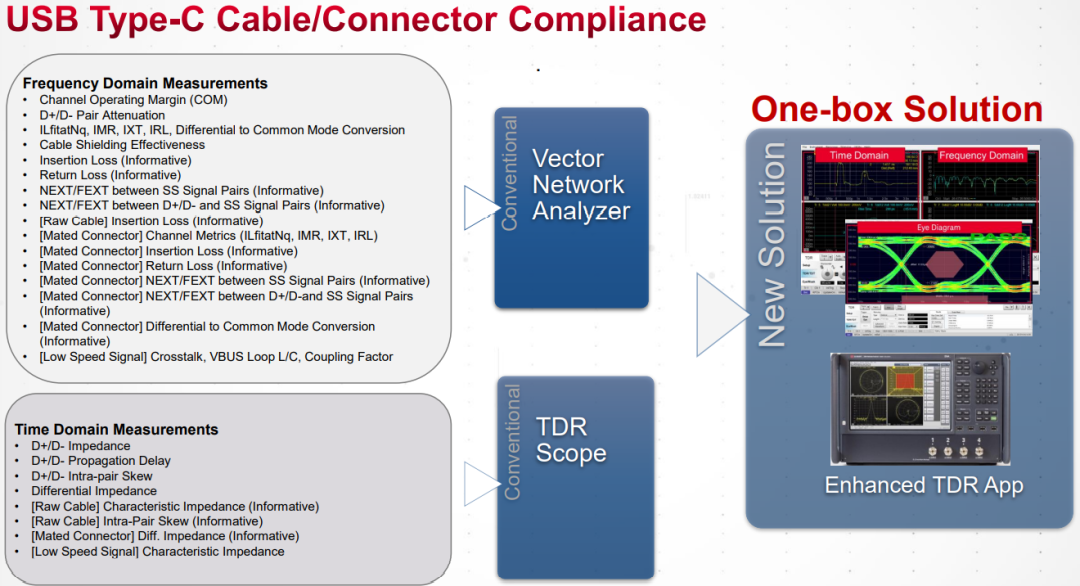

对线缆和连接器等一致性测试,其类型和信号种类复杂多样,不但包括USB 2.0、USB 3.2、USB4等高速信号而且包括CC、SBU、VBUS等低速信号。表征高速信号的关键指标包括ILFit(插损拟合)、IMR(积分多次反射)、IRL(积分回损)、IXT(积分串扰)等,相比线缆通用的S参数,比如IL、RL等不同,涉及复杂的数学计算。

另外还借鉴IEEE 802.3标准引入了COM技术通过SNR指标去评价。是德科技根据“USB Type-C Cable and Connector Specification“和”USB Type-C Connectors and Cable Assemblies Compliance Document“文档,基于E5080B 4 Ports/P5000 USB VNA/M9804A Multiport VNA推出了USB Type-C线缆和连接器的一致性测试解决方案。

图:USB Type-C线缆和连接器一致性测试方案

DP2.1技术

除支持USB4(Tunnel技术仅支持到DP1.4a/HBR3),Type-C接口也可支持DP2.1用于音视频传输。DisplayPort的发起组织是VESA,Genesis、Intel、AMD、Analogix、HP、Dell包括Keysight等都积极参与了标准的制定,其主要优势在于非常高的数据速率、方便的连接、完善的内容保护及基于包交换的数据传输方式,支持4对差分通道,可以级联多达32个显示器。

基于DP技术的通信架构需要高速链路、低速Aux通道及HPD(全尺寸DP接口需要)等的参与。Aux Channel是差分信号,工作在双向/1Mbps速率,进行链路管理和测试模式控制,可以获取EDID和DPCD信息,链路训练仍需高速通道参与。DP2.1支持1或2或4 lane通道数,可选支持SSC、拥有7种不同速率,其中借助Type-C连接器可支持高速率UHBR13.5、UHBR20,编码使用128b/132b编码效率提高到97%,同时收发物理层电气架构也变得复杂,发送使用3抽头的FFE实现16种不同presets、接收使用CTLE和DFE的组合来克服高频损耗,CTLE支持10种不同DC增益电平设置,考虑发送FFE,组合多达160种。

DisplayPort物理层电气一致性测试涉及Source、Sink端测试、连接器/线缆。

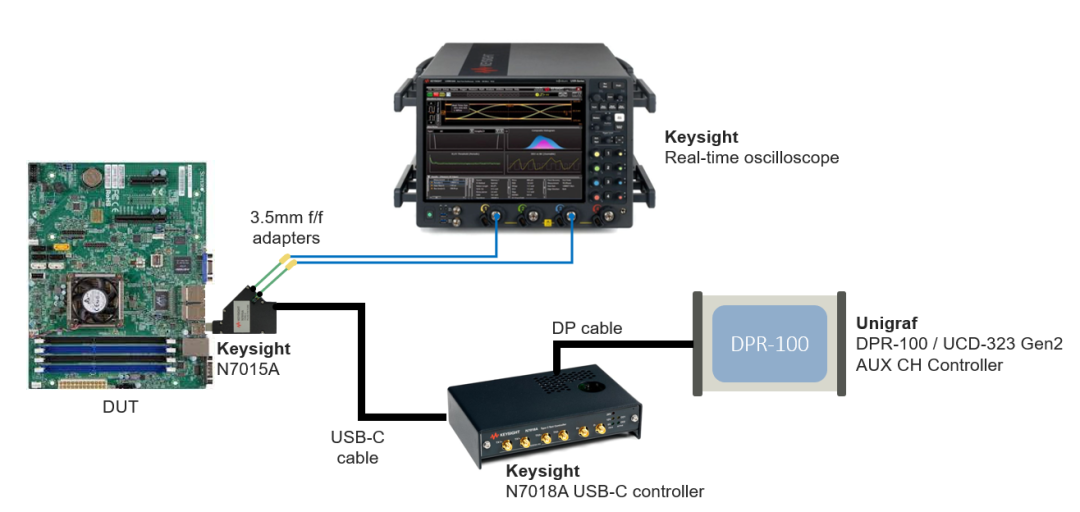

下图是DisplayPort Source发送端一致性测试的连接示意图。和其他的高速串行总线接口发送端一致性测试方案类似,主要有夹具、低损耗相位匹配电缆(或者SMA/2.92mm探头套件)、实时示波器组成。

根据CTS测试规范要求(DP2.1 Spec和CTS还未正式发布),首先,测试要明确一致性测试点,Source在TP2测试,示波器要支持嵌入S参数和均衡能力实现TP3及均衡数据处理,其次,要求被测设备支持不同速率,比如UHBR10/13.5/20速率,支持测试码型,比如PRBS15、PRBS31、SQ128,支持SSC,支持P0~P15 Presets,再次,明确测试参数,遍历3种不同速率,包括TP2相关:Rise time fall time、EQ(PS/DE/Swing-P15)、Preset Cal(P0~P15)、UI、Main Link Frequency、SSC、Voltage、AC Common Mode、TJ、RJ、UJ、UDJ、ISI、DCD、DDJ、LFUDJ、Eye ;TP3相关:Eye-TP3、Preset&Eq Cal-TP3_EQ、TJ-TP3_EQ、RJ-TP3_EQ、UJ-TP3_EQ、DDJ-TP3_EQ、ISI-TP3_EQ。

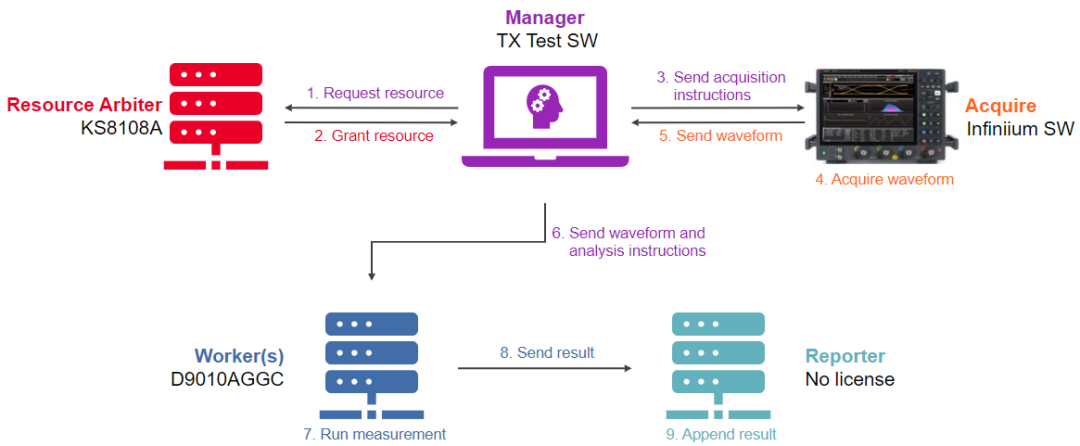

除芯片厂家有专门的软件,可以配置DUT外,业内通常会使用一个经过协会认证的Reference AUX controller(DPR-100、UCD-323等),配置示波器的DisplayPort一致性分析软件D9040DPPPC/D9042DPPC通过AUX channel和DUT通讯,让被测设备在合适的时间产生相应的相应速率和测试码型,从而形成一个全自动化的闭环测试。测试速率多、码型多、参数多,仅靠示波器仍需很长时间完成4 lane所有测试,是德科技推出测量解耦方法,示波器顺序采集,通过更多外部电脑实现并行数据处理,减少处理时间,提高效率。

图:DP一致性测试点和说明

图:DP Source电气一致性测试组网图

图:测量解耦

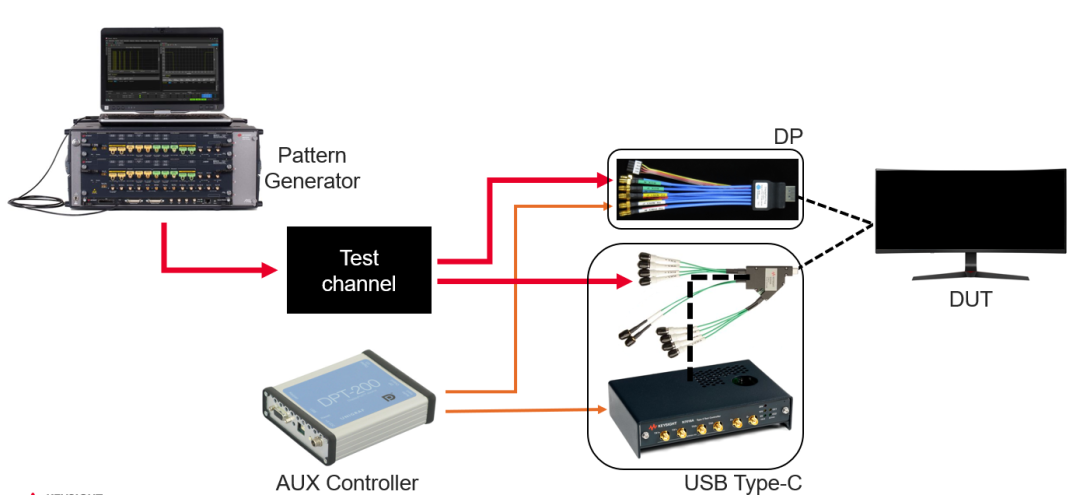

对于DP Sink,进行电气一致性测试,它作为接收机需要一台能够激励信号并且压力参数可调的设备。是德科技的误码仪M8000系列,内置了经过校准的抖动源,可以直接产生带抖动的信号,如产生RJ、PJ/SJ、ISI的抖动和带SSC的信号,同时可支持注入AC CMSI干扰。而如何保证Stressed Signal经过不同的测试附件和测试夹具,在Sink设备的测试点严格满足CTS的测试规范要求,就需要在进行Sink设备测试前,用高带宽示波器对信号进行校准。是德科技N5991DP2A DP2.0 Sink一致性测试软件,通过图形化界面,可以准确的控制示波器和误码仪的输出,全自动化完整信号校准。在进行Sink测试时,N5991DP2A软件控制误码仪产生相应的带压力的码型序列通过夹具注入到Sink设备,同时,控制Aux Controller完成和Sink设备的链路协商、Symbol lock和误码率测试(DUT内有Error Counter)。因此,一个完整的DP Sink测试方案要求有误码仪、高带宽示波器、自动化控制软件、Aux Controller和必要的测试附件/夹具,如下所示

图:DP Sink测试组网

DP souce和sink实现互连,连接器/线缆必不可少,同样需要网络仪参考规范进行一致性测试。速率提高到10G、10.3125G、20G,高速测试的时域和频域关键指标仍然可以借鉴USB Type-C提到的ILFit(插损拟合)、IMR(积分多次反射)、IRL(积分回损)、IXT(积分串扰)等。

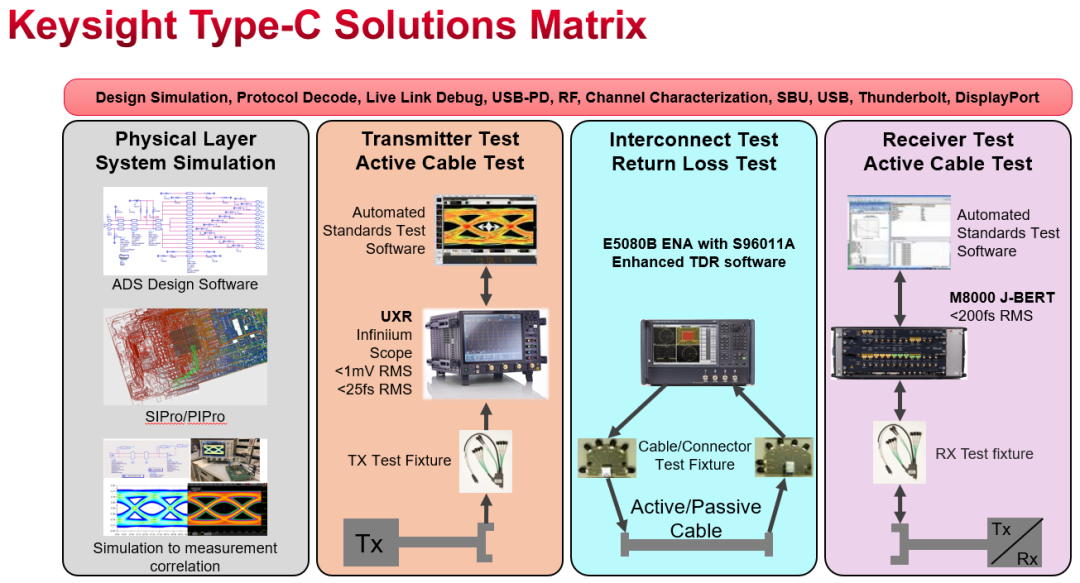

VESA DP2.1规范也提及增强型的mini DP和全尺寸DP连接可改善链路性能支持更高速率。目前DP2.1一致性测试规范还在制定之中,是德科技参与相关验证测试,新发布的D9042DDPC和N5991DP2A可以支持UHBR速率。面对更高速率的接口技术、更复杂的收发架构和新增测试参数,是德科技可以提供从仿真、调试、物理层电气一致性测试到互联通道测试等整体方案,如下图:

图:是德科技Type-C整体测试方案框图

关于是德科技

我们致力于帮助企业、服务提供商和政府客户加速创新,创造一个安全互联的世界。自 1939 年惠普公司成立,到 2014 年 11 月 1 日是德科技作为一家新电子测试测量公司独立运营,我们继续秉承不变的企业家精神和激情开启新航程,鼓舞全球创新者,帮助他们实现超乎想象的目标。我们的解决方案旨在帮助客户在 5G、汽车、物联网、网络安全等领域不断创新。

原文标题:极简连接之Type-C新技术及接口芯片测试

文章出处:【微信公众号:是德科技KEYSIGHT】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

USB Type-C连接器解决方案2025-05-19 2404

-

LDR6500如何实现Type-C转DP或DP转Type-C2025-02-10 2713

-

Type-C转DP线方案2024-11-11 3855

-

上海雷卯推出一种USB4接口的静电浪涌保护方案2024-02-28 2393

-

选对一个插座 玩转USB4 第 3 代 Type-C2023-11-27 2077

-

你知道80Gbps USB4 V2怎么测吗?USB Type-C测试方法一文搞懂2023-08-23 13585

-

Type-C新技术与接口芯片2023-04-28 5420

-

力科扩展Type-C连接器的USB4信号传输2023-02-10 1023

-

DisplayPort 2.1标准发布 与USB Type-C规范、USB4 PHY规范在底层打通 AMD有望首发2022-10-18 4727

-

USB Type-C拓展坞方案简介2022-09-05 9087

-

如何通过TPS65994AD和TUSB1046A实现USB Type-C DP Mode2021-11-10 4903

-

USB4、Type-C和雷电接口一对一区别2021-06-13 77650

-

USB Type-C拓展坞方案特点及相关信息2019-10-16 14183

-

USB Type-C的技术特点2016-01-13 5039

全部0条评论

快来发表一下你的评论吧 !