基于多数决定逻辑门的全加器电路设计

模拟技术

描述

O 引言

加法运算是算术运算中最基本的运算。减法、乘法、除法及地址计算这些基于加法的运算已广泛地应用于超大规模集成电路(VLSI)中。全加器是组成二进制加法器的基本组成单元,所以提高全加器的性能是提高运算器性能的最重要途径之一。

对于全加器结构的研究,国内外有许多相关报道,大多数研究致力于提高全加器的速度和降低其功耗。设计全加器的方法有很多种,最简单的方法是用组合门实现所需的逻辑函数,另外一种常用的方法是采用传输门实现。由于传输门具有很强的逻辑功能,且输入电容小,因而用传输门实现的全加器速度快,且结构简单。采用传输门实现的全加器比组合门实现的全加器电路要简单。但这种电路以CMOS传输门为基本单元,而不是在管子级进行设计,因而,这种全加器电路存在冗余,需进一步简化。

结合上面的讨论,提出一种结构更加简单,性能更好的加法器单元电路,它仅由输入电容和CMOS反向器组成,而且通过电路简化设计,克服了功耗问题。

本文首先提出多数决定逻辑门的概念和电路设计,然后提出了一种基于多数决定逻辑门的全加器电路设计。该全加器三个主要特征是较少的管子、工作于极低电源电压以及短路电流的消除。模拟结果表明,这种新的结构能够很好地完成全加器的逻辑功能。

1 多数决定逻辑非

1.1 多数决定逻辑非的提出

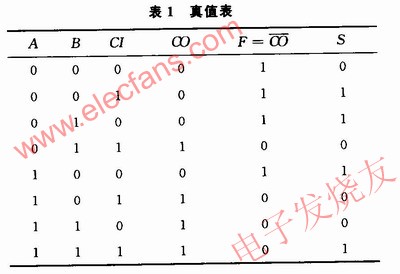

多数决定逻辑(Majority Logic)定义为:若逻辑1的个数大于逻辑0的个数,则输出为逻辑1;若逻辑O的个数大于逻辑1的个数,则输出为逻辑O。表1中CO即为A,B,CI的多数决定逻辑,逻辑式表示为CO=M(A,B,CI)。多数决定逻辑非(Majority-not Logic)则为多数决定逻辑非函数,表1中即为A,B,CI的多数决定逻辑非函数,逻辑式表示为F=F(A,B,CI)。

1.2 多数决定逻辑非门的电路设计

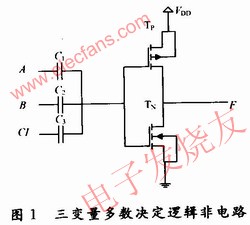

图1即为三输入端的多数决定逻辑非门电路。其中,C1=C2=C3,它由输入电容和一个静态CMOS反向器构成。只需增加输入电容的个数,即可增加输入端的个数。电容网络的作用是分离电压。当输入端中O的个数多于l的个数,电容网络的输出为0,经反向器之后输出为高电平1(VDD);当输入端中1的个数多于0的个数,电容网络的输出为1,经反相器之后输出为低电平O(0 V)。输入电容的电容值大约为O.05 fF,它对电路没有影响。欢迎转载,本文来自电子发烧友网(http://www.elecfans.com/)

输入电容可选择用金属氧化物半导体(MOS)电容。与其他电容相比,MOS电容具有占用芯片面积小,电容值大,更容易匹配等优点。一个MOS电容所占用芯片的面积与一个普通晶体管相当。通常,对于相同的面积,PMOS电容值大于NMOS电容值。所以可选用PMOS电容来实现多数决定逻辑非门的输入电容。

普通CMOS门电路的功耗主要由动态功耗Pswich、短路功耗Pshort、静态漏电流功耗Pleak三部分组成,见式(1)。如果满足式(2),则两个管子不能同时导通,除去Pshort,功耗将显著减小。

式中:fcp表示系统时钟脉冲;Vim为节点i的电压变化范围(理想情况下为VDD);CiL为节点i的等效负载电容;ai为节点i的活动因子;Iisc和IL分别为短路电流和漏电流;P为总功耗。

式中:VthP和VthN分别是PMOS管和CMOS管的开启电压。开启电压指的是绝缘栅场效应管(MOSFET)沟道形成时的电压。

图1中因为电路仅用了两个管子,所以电源电压可减小,相对于电源电压,Pswich将以二次方的速度衰减。只需满足式(2),除去Pshort。所以其功耗大大小于传统的CMOS门电路。

虽然减小电源电压可以减小功耗,但是会影响电路的输出波形。式(3)、式(4)给出电源电压的减小和开启电压的增大对管子高低电平转换延迟时间的影响。

2 全加器的设计

2.1 全加器的逻辑设计

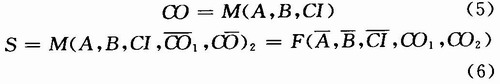

根据全加器的定义,其真值表如表1所示。其中,A和B为加数和被加数,CI为来自低位的进位;S为和输出,CO为进位输出。根据前面的分析,全加器的进位输出CO可表示为输入A,B,CI的多数决定逻辑,而和输出S则为A,B,CI,,五变量的多数决定逻辑,或表示为,CO1,CO2(其中CO=CO1,=CO2)的多数决定逻辑非。可用逻辑式表示出来:

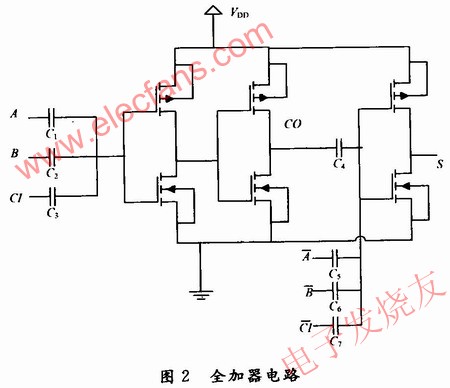

2.2 全加器的电路设计

根据逻辑式(5)、式(6),设计电路如图2所示。该设计中,仅用了两个多数决定逻辑非门。只需6个MOSFET即可实现优化的CMOS全加器,用PSpice进行了晶体管级模拟。结果显示,这种新的全加器能正确完成加法器的逻辑功能。图2中,C1=C2=C3=0.05 fF,2C4=C5=C6=C7=2.88 fF。

3 结语

提出一种低功耗的仅用输入电容和CMOS反向器实现的一位全加器电路设计。该电路仅用了6个管子,从而达到降低功耗的目的。较少的管子、工作于极低电源电压以及短路电流的消除是该全加器3个主要特征。

-

逻辑门及组合逻辑电路实验2008-09-25 4733

-

集成逻辑电路、组合逻辑电路2008-12-11 5869

-

如何用两片四位全加器和必要的逻辑门设计数制转换电路2016-07-04 5164

-

【数字电路】关于逻辑或门的电路设计教程2021-01-21 5163

-

如何利用输入电容和CMOS反向器实现一位全加器电路设计?2021-04-08 2470

-

什么是8位全加器和8为带超前进位的全加器?2022-02-09 1577

-

钟控传输门绝热逻辑电路和SRAM的设计2010-02-23 598

-

数字逻辑电路设计课程2010-05-24 1288

-

一种基于互补型单电子晶体管的全加器电路设计2017-02-07 856

-

逻辑门是什么?基础数字逻辑门详解2017-05-22 61857

-

全加器逻辑表达式_全加器的逻辑功能2020-04-23 134587

-

浅析数字逻辑电路之逻辑门或逻辑2021-10-29 10615

-

Verilog数字系统设计——复杂组合逻辑实验2(8位全加器和8为带超前进位的全加器)2021-12-05 659

-

门极栅极驱动电路设计方法2022-11-09 510

-

关于逻辑门的基本知识2023-04-30 5375

全部0条评论

快来发表一下你的评论吧 !