打造面向新一代通信的全新芯片架构

今日头条

描述

来源:Awanish Verma,赛灵思首席架构师兼技术营销总监

第一部分 打造面向新一代通信的全新芯片架构

5G 新无线电 (NR) 网络规范需要新的无线电和接入网架构。虽然 5G NR 架构包括新的频谱和大规模 (mMIMO) 天线,但相应的接入网架构也必须演进发展才能实现5G 定义的服务, 其中包括增强型移动宽带、超可靠低时延通信与大规模机器类通信。实施这些服务需要在不同级别的网络聚合节点上进行网络切片。由于纯软件解决方案无法满足不断攀升的时延和吞吐量需求,导致网络加速成为巨大需求,而这个问题则可以通过可编程硬件得到良好解决。在本部分,我们专门讨论采用自适应射频 (RF) SoC 加速的第一级 5G 接入网聚合。

为了满足这些新要求,3GPP 标准组织在 5G 无线电单元 (RU) 和 5G 基站之间定义了不同的分割架构。不同的分割架构在决定 gNodeB 架构方面起着决定性的作用。上层分割定义了集中式单元 (CU) 和分布式单元 (DU) 之间的功能划分,而下层分割则定义了 RU 和 DU 之间的功能分区。下层 (RU-DU) 分割在时序和时延方面更为关键和敏感,并且没有标准化。

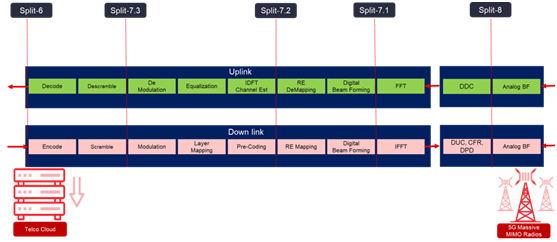

图 1:下层分割有多种选择

虽然Split-8 在传统的 4G-LTE 网络中更为常见,但在 5G 网络中 则更多采用的是Split-7.2。分割选项 7.2 具有多种变体,因此也被称为选项 7-2x,因为它可以根据部署场景向左或向右移动,如上图所示。由于分割选项很灵活,并且 DU 和 RU 之间的接口在接口协议、带宽、时延和时序方面也没有严格定义,因此为实现接口与功能而在 RU 和 DU 处部署可编程处理器,通常是较为理想的选择。

商用网络接口卡 (NIC) 可用于终止 5G 基站在 DU 的前传。然而,基于 ASIC 的网卡只能处理 L2-L3 流量,并且依赖于软件进行 O-RAN 处理,而且大多数通用网卡都没有定时同步功能。由于 DU 需要与无线电单元和相邻基站实现严格的时间同步,因此它们需要支持来自中央GPS时钟源的主、从和边界时钟操作模式。另一个重要的定时功能,是在基站硬件上实现的时钟保持电路,以便在丢失参考时钟的情况下保持时钟的同步。

一旦来自 RU 的无线电 IQ 数据可用于处理,就需要对其进行处理,以便在上行链路和下行链路方向上识别为用户平面、控制平面、管理平面和同步平面数据。同步和管理平面协议消息的吞吐量明显低于 U 平面和 C 平面消息,因此,大部分时间消息的同步和管理在软件中处理,而应用则在用户空间中运行。

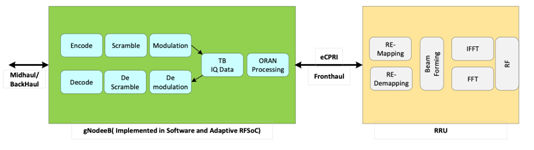

3GPP 分割选项 7-2 split 还定义了 High-PHY 和 low-PHY 功能之间的明确划分,其中 Low-PHY 功能(如预编码、FFT/IFFT)与资源元素 (RE) 映射/解映射功能,要么在远程无线电单元 (RRU) 实现,要么在 RU 和 DU 之间的前传网关网络节点实现。High-PHY 功能(主要包括编码/解码、加扰和调制/解调制)在 DU 中执行。

图 2:采用赛灵思自适应 RFSoC 的 5G 分割选项 7-2 split 实现方案

gNodeB (DU) 中的 High-PHY 功能可以完全通过软件实现,也可以通过将软件与可编程硬件相结合来实现。软硬件之间的 High-PHY 功能划分取决于众多因素,例如:

软件(或硬件)对整体性能的性能限制,即软件不应限制硬件的性能,反之亦然。

时延考虑因素:由于 5G 规范对不同类别的服务提出了严格的时延要求,因此该划分不应对时延产生负面影响。

与行业标准软件API 的兼容性:一些High-PHY 功能具有用户空间API 的标准定义,因此任何硬件实现方案都应保持与标准 API 的兼容性,以实现无缝过渡。

上述标准概述了赛灵思等公司基于可编程硬件的加速器所需的功能。理想的加速器架构可能需要在硬件中实现完整的 5G High-PHY,这将实现最高性能和最低时延,同时还可以跨多个基于 mMIMO 的 RRU 配置进行扩展。随着 5G 和 O-RAN 标准与功能的演进发展,赛灵思已开始在可编程加速器卡上实现 O-RAN 处理和后备通道编码/解码。通道编码是 High-PHY 功能之一,由于其计算密集型特性,最适用于可编程硬件。此外,它还可以与混合自动重传请求 (HARQ) 功能相结合,以提高性能并降低时延。

加速 5G L1 High-PHY 功能的一种方法,是基于自适应和可编程的赛灵思 T 系列电信加速器卡。这些卡带有自适应 RFSoC,可强化基于软决策的前向纠错 (SD-FEC) 模块,并通过板载 DRAM 实现 HARQ 功能,以便获得更优异且可扩展的性能。

在下一篇文章中,我们将深入探讨有关电信加速器卡的一些细节,同时还将探讨 5G 基带加速的下一步发展。

第二部分 5G 基站前传和 L1 High-PHY 的实现

在文章第一部分中,我们讨论了 5G 分割架构,重点介绍了广泛采用的分割选项 7-2 split。在第二部分中,我们将介绍 5G 基站前传和 L1 High-PHY 的实现。5G 分布式单元 (DU) 可用于通过 O-RAN 处理与部分卸载处理前传数据,以进行 High-PHY 处理,其中包括 LDPC 编码器、LDPC 解码器以及编码器与解码器逻辑的包装器功能。

前传处理:下面的示例架构假设有两个网络接口连接至 5G 无线电单元 (RU),如图 3 所示。5G DU 必须能够在 5G 和 5G 基站之间进行全容量的网络连接数据传输。网络接口模块包括连接至工业标准接口光学模块的以太网 MAC 接口,用于发送和接收增强型通用公共无线电接口 (eCPRI)、以太网无线电 (RoE) 或来自 5G RU 的时间敏感型网络 (TSN) 以太网数据。主机接口通常是 PCIe,包括采用直接存储器访问 (DMA) 的高速数据传输机制。

前传处理可以分为以下主要子模块,接下来我们将进一步介绍每个模块。

图 3:5G 基站节点上的前传处理。

1. 精确时间协议 (PTP) 功能:通过利用亚纳秒粒度的流量时间戳,使本地时钟(充当从节点时钟)与系统主时钟实现同步。DU 将接收到的 1588v2 PTP 数据包作为流量的一部分,并将其标识为同步平面数据包。然后,在将时间戳字段替换为由参考时钟生成的时间戳字段后,它们将被发送到在 x86 上运行的 S 平面应用。该模块的其他功能包括延迟请求的处理、从软件更新一天时间的主时钟定时器值以及在主模式下产生 1PPS(每秒脉冲)。

2. 流量分类器/聚合器:该模块的功能支持控制、用户、同步和管理(C、U、S 和 M 平面)消息的路由。流量分类器模块可以执行流量规则,用于丢弃或处理来自传入网络端口的传入前传流量。该模块可以在上行链路和下行链路方向上接收 eCPRI 数据包(C 和 U 平面)和以太网数据包(S 和 M 平面)。

对于上行链路处理,eCPRI 数据包由数据包报头中的 eCPRI 消息类型字段进行识别。这包括根据配置规则检查源 MAC 地址、目标 MAC 地址和虚拟局域网 (VLAN) ID,以及在规则不匹配时丢弃数据包。对于上行链路方向的 S 和 M 平面以太网数据包,它可以实现一个简单的仲裁器,以进行调度并将其传输到主机接口队列。

对于下行链路,它可以根据 eCPRI 报头中的消息类型字段配置不同 eCPRI 消息的优先级。此外,它还可以根据 C 和 U 平面配置添加 VLAN 标签,而且 VLAN 标签中的优先级字段可用于为 C/U 平面消息分配优先级。也可以对 S 和 M 平面进行 VLAN 标记并分配优先级。与此同时,该模块还可以实施优先级调度程序,以便根据分配的优先级将数据包发送到已连接的前传端口之一。

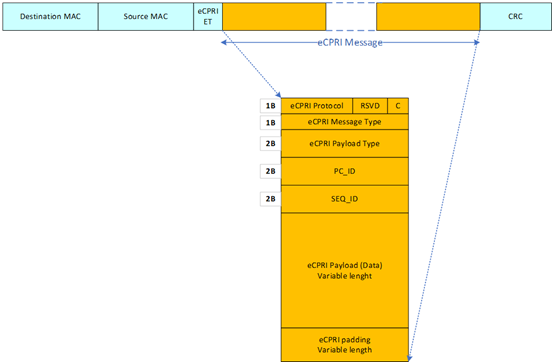

3. eCPRI 成帧器和解帧器:eCPRI 成帧器/解帧器处理负责上行链路和下行链路 C/U 平面消息的 eCPRI 协议处理。eCPRI 处理需要包括单独的上行链路和下行链路数据路径处理。由于 eCPRI 处理必须支持基站中的多天线载波 (AxC) 配置,因此该模块的灵活应变能力使其能够根据部署场景进行放大和缩小。eCPRI-over-Ethernet 消息的数据包格式如图 4 所示。添加填充(零填充)字段是为了使短消息的 eCPRI 最大传输单元 (MTU) 的大小为 64B。

图 4:以太网数据包中的 eCPRI-over-Ethernet 消息。

由于下行链路的 C 平面消息也在 5G DU 处生成,因此 eCPRI 成帧器同时处理上行链路和下行链路 C 平面消息以及下行链路 U 平面消息。通过使用分层调度程序和多路复用方案,eCPRI 消息的多个流/层可以由单个 eCPRI 成帧器数据路径共享。eCPRI 成帧器生成 eCPRI 消息的不同字段并进行填充,以创建 eCPRI-over-Ethernet 数据包,通过前传接口进行传输。

eCPRI 解帧器模块具有以下功能:

以太网报头的处理与删除

eCPRI报头的解析与删除

删除eCPRI 填充,其中包括基于报头字段的流标识和序列号

删除eCPRI 数据中的零填充(对于短消息)

检查长度和其他协议错误

每个eCPRI 流的统计信息

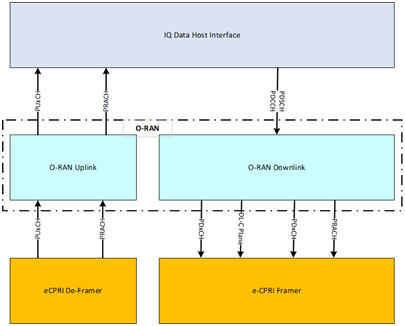

4. O-RAN 处理器:O-RAN 模块与 eCPRI 模块一起工作,通常与主机接口连接以提供以下功能:

从e-CPRI 解帧器接收上行链路 U 平面消息,以提取 IQ 数据并将其传送到主机

提取C 平面IQ 数据的包装信息,并将其相应地用于上行链路U 平面消息

延迟管理并将C 平面消息转发到eCPRI 模块

从主机到O-RAN 消息的U 平面IQ 数据成帧,并传送到 eCPRI 成帧器

O-RAN 模块接口如图 5 所示。

图 5:上行链路和下行链路数据的 O-RAN 模块接口。

O-RAN 上行链路和下行链路模块均设计为与四个独立的 AxC 接口连接。在上行链路方向上,O-RAN 模块根据 O-RAN 报头中的参数将 U 平面消息分为物理随机接入信道 (PRACH) 或物理上行链路共享信道 (PUSCH)。然后对这些消息进行解帧,以提取相应的 IQ(用于无线电信号的数据格式)样本。在下行链路模块中,对 C 平面消息进行解析,以提取 U 平面成帧所需的信息。

5. IQ 数据主机接口:主机接口模块向 CPU 发送并从其接收 IQ 数据样本,处理 U 平面和 C 平面消息的延迟管理。对于 IQ 样本的缓存,可以使用外部存储器来确保数据包无损传输到前传接口。主机接口模块读取存储在存储器中的数据以及自适应片上系统 (ASOC) 生成的定时信号,以确保 ASOC 和主机 CPU 之间的插槽同步。

如上所述,前传处理和 L1 High-PHY 加速需要能够适应各种大规模多输入多输出 (mMIMO) 天线配置,以实现前传连接和吞吐量。数据路径处理应该能够提供具有 eCPRI 和 O-RAN 处理的线路速率接口,同时满足 5G 规范的时延和同步要求。

赛灵思在其 T1 电信加速器卡中实现了前传参考设计,可处理的总吞吐量为 50Gbps,这大约相当于 8 层 4T4R 100MHz 的主备配置。该卡使用自适应 MPSoC 和 RFSoC 器件保持功能的灵活性。在大多数 DU 实现方案中,在自适应器件上使用 O-RAN 处理器,x86 软件可实现完整的无线 L1 堆栈,并且可以提供显著的吞吐量和时延优势。

我期待在我的下一篇文章中分享更多内容,下一篇文章将重点介绍 L1 High-PHY 功能的部分卸载,以及使用可编程器件可在灵活性、吞吐量和时延方面获得哪些优势。

关于我们

《半导体芯科技》(Silicon Semiconductor China, SiSC)是面向中国半导体行业的专业媒体,已获得全球知名杂志《Silicon Semiconductor》的独家授权;本刊针对中国半导体市场特点遴选相关优秀文章翻译,并汇集编辑征稿、国内外半导体行业新闻、深度分析和权威评论、产品聚焦等多方面内容。由雅时国际商讯(ACT International)以简体中文出版、双月刊发行一年6期。每期纸质书12,235册,电子书发行15,749,内容覆盖半导体制造工艺技术、封装、设备、材料、测试、MEMS、IC设计、制造等。每年主办线上/线下 CHIP China晶芯研讨会,搭建业界技术的有效交流平台。独立运营相关网站。

审核编辑:汤梓红

-

宝马发布全新一代智能电子电气架构2025-03-13 848

-

龙芯中科携手百代存储打造基于龙架构的新一代国产统一存储解决方案2023-10-09 1828

-

【新品】全新一代LoRa无线扩频模块2023-01-12 2023

-

德州仪器(TI)推出新一代KeyStone II架构2021-05-19 2572

-

新一代军用通信系统的挑战2021-03-02 2457

-

MIMO之新一代移动通信核心技术2020-07-17 3247

-

新一代音频DAC的架构介绍2019-07-22 3066

-

基于4G和Beyond 3G的新一代移动通信系统讨论2019-07-17 2642

-

TI 全新一代宽输入降压芯片性能特点及应用介绍2019-05-09 5234

-

Imagination推出全新一代PowerVR Furian GPU架构 满足下一代消费类设备图形运算需求2017-03-10 1182

-

全新 ARM Cortex-M 处理器为物联网安全树立新一代行业标准2016-11-12 3198

-

借助iMX6打造新一代工业互联网智能核心2014-11-18 3739

全部0条评论

快来发表一下你的评论吧 !