DS1647为512k x 8非易失性静态RAM

缓冲/存储技术

14人已加入

描述

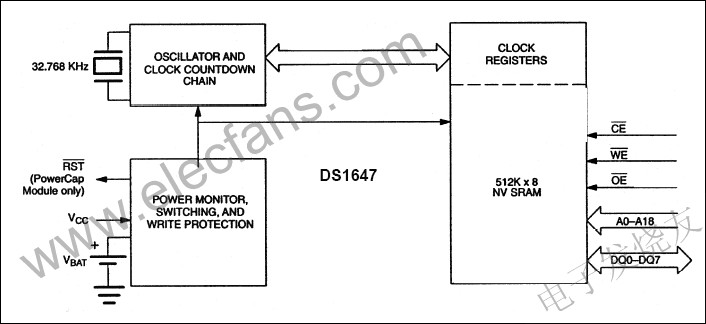

DS1647为512k x 8非易失性静态RAM,包括一个完备的实时时钟,两者均以字节宽度格式访问。非易失性时间保持RAM功能等价于任何一款JEDEC标准的512k x 8 SRAM。该器件也能够轻松替代ROM、EPROM及EEPROM,提供读/写非易失性以及增加实时时钟功能。实时时钟信息占用8个最高端RAM地址。RTC寄存器包括年、月、日、星期、时、分、秒等数据,以24小时制、BCD编码格式表示。对于每月天数及闰年的修正是自动完成的。RTC时钟寄存器是双缓冲的,以避免在时钟更新循环期间可能引起的不正确数据存取。双缓冲系统也能阻止存取时间寄存器数据时所引起的时间损失。DS1647还包含自身电源失效电路,一旦VCC电源进入超出容差状态,则禁止访问该器件。该特性由于避免了错误的访问和更新周期,因而阻止了较低VCC引起的不可预测系统运行的数据丢失。

关键特性

集成了NV SRAM、实时时钟、晶振、电源失效控制电路及锂电池

时钟寄存器访问方式等同于静态RAM,这些寄存器占用8个高端RAM地址

无电源供电时,可保持非易失性10年以上

BCD编码的世纪、年、月、日、星期、时、分、秒,同时具有自动闰年补偿至2100年

电源失效写保护允许±10% VCC电源容差

DS1647 (DIP模块):

标准JEDEC字节宽度128k x 8 RAM引脚

DS1647P (PowerCap模板):

表面可贴装的封装形式,直接连接到包括电池和晶振的PowerCap模块

电池可更换(PowerCap)

电源失效输出

引脚兼容于其它密度的DS164xP时间保持RAM

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

深入解析DS1554:256k非易失性Y2K兼容计时RAM2026-03-24 253

-

DS1557 4M非易失、Y2K兼容时钟RAM技术手册2025-02-27 1207

-

基于CY15B104Q 4-Mbit(512K x 8)的串行FRAM2020-07-22 1401

-

DS1746,DS1746P非易失时钟RAM2012-03-19 3333

-

DS1251,DS1251P全静态非易失RAM2012-01-04 1146

-

DS1250 4096k、非易失SRAM2010-12-07 1787

-

DS1225Y 64K非易失SRAM2010-11-03 2350

-

DS1646是一个128K的× 8非易失性与全功能实时时钟2010-10-22 1228

-

DS1220Y 16k非易失SRAM2010-10-20 1448

-

非易失性SRAM DS17472010-09-28 1506

-

非易失Y2K兼容时钟RAM DS15572010-09-15 1081

全部0条评论

快来发表一下你的评论吧 !