AI Engine架构的构成及应用优势

描述

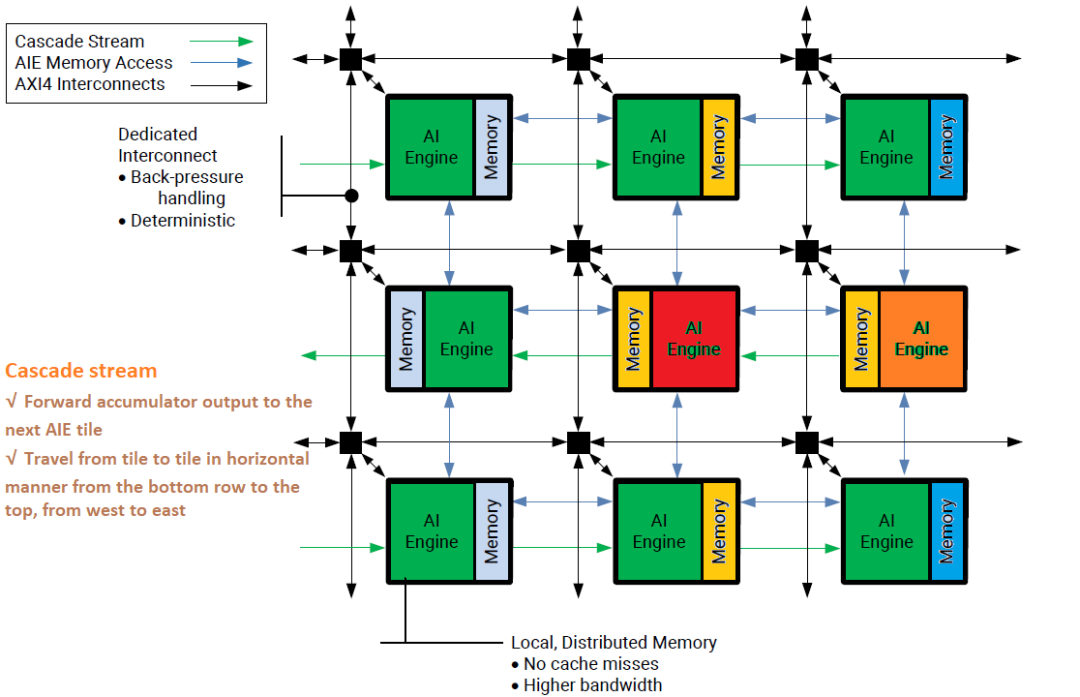

AI Engine阵列是由一系列的AI EngineTile构成。每个AI Engine Tile包含一个AI Engine,一个存储单元和一个互连单元,如下图所示。可以看到相邻两行AI Engine Tile的存储单元与AI Engine的位置正好相反。

存储单元可被东西南北四个方向的AI Engine共享,当然这也跟AI Engine的位置有关。例如图中红色AI Engine可访问与之相邻的4个存储单元(黄色标记)。最右侧的橙色AI Engine就只能访问三个存储单元,因为其位于边界。每个方向的存储单元都有对应的存储器接口,AI Engine在访问相应方向的存储单元时正是通过这些接口实现的。每次访问的最大位宽为256。

水平方向相邻的两个AI Engine之间还有级联端口,用于传送累加器的结果。仍以上图为例,最下方的一行AI Engine可从左至右级联,倒数第二行的AI Engine可从右至左级联。同时,最下方级联至最右侧时可与倒数第二行最右侧的AI Engine级联,形成蛇形级联。

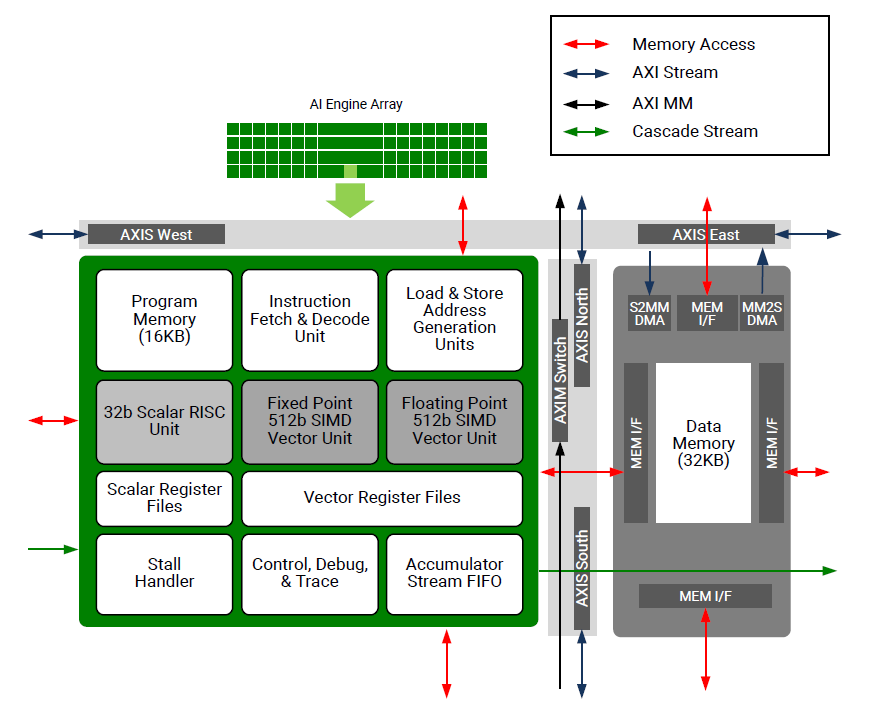

互连单元采用AIX4 Stream接口将数据在东西南北四个方向传送。同时每个AI Engine Tile的存储单元都包含一个DMA。每个DMA由一个独立的S2MM和一个独立的MM2S构成。前者用于将数据从Stream上取下来写入到存储单元,后者用于将存储单元的数据上传到Stream,如下图所示。

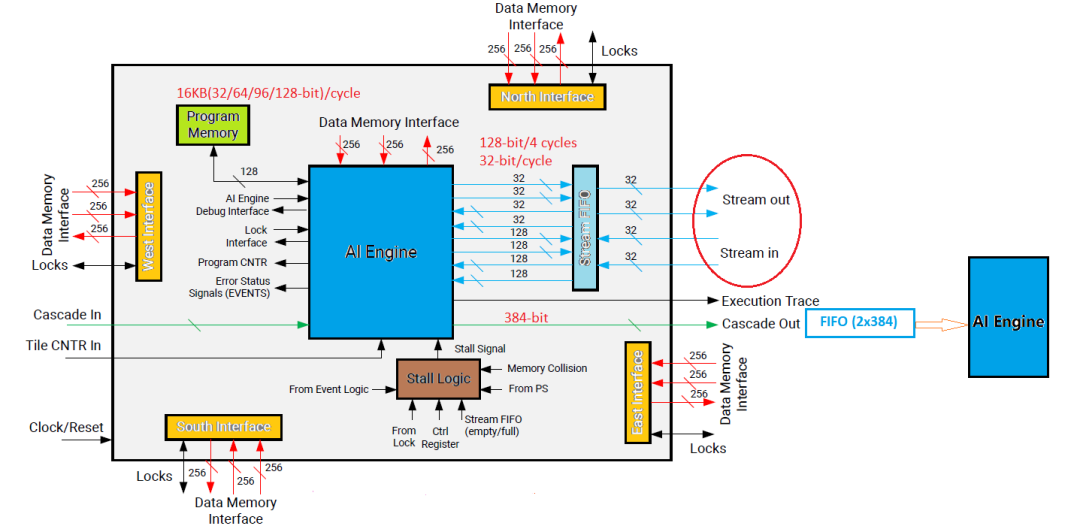

再看AI Engine自身,如下图所示。每个AIEngine包含一个程序存储单元,大小为16KB,有2个Stream输入接口和2个Stream输出接口,均为32位。因此,每个时钟周期可从一个Stream上获取一个32位数据或每4个时钟周期可从一个Stream上获取一个128位数据。每个AI Engine还有4个存储单元访问接口,但每个时钟周期只可以有两次读操作和一次写操作。

至此,我们可以看到AI Engine有三种数据源:存储单元、AXI4-Stream和级联接口。因此,编程时需要充分了解AIE的数据访问能力:2个32位AXI4-Stream输入,2个32位AXI4-Stream输出,1个384位级联Stream输入,1个384位级联Stream输出,2个256位读操作和1个256位写操作。

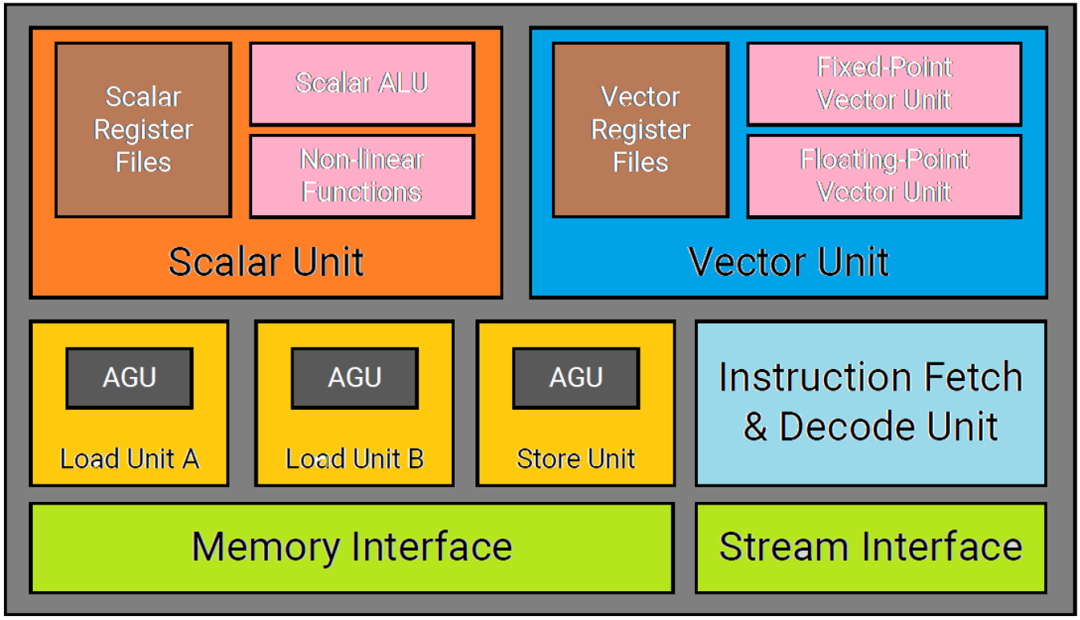

AI Engine本身是一个高度优化的SIMD(Single Instruction Multiple Data)& VLIW(Very Long Instruction Word)处理器,包含1个标量处理单元,1个向量处理单元,2个读地址发生器,1个写地址发生器,1个取指和译码单元,如下图所示。正因为有2个读地址发送器和1个写地址发生器,所以每次访问可实现2个256读操作和1个256写操作。

审核编辑:郭婷

-

基于Vitis Model Composer完成全流程AI Engine开发2025-12-31 6323

-

蚂蚁数科发布新一代融合AI风控引擎“AIR Engine”2024-06-26 2576

-

NanoEdge AI的技术原理、应用场景及优势2024-03-12 1619

-

【CC3200AI实验教程14】疯壳·AI语音人脸识别-AI人脸系统架构2022-08-31 29544

-

【CC3200AI实验教程11】疯壳·AI语音人脸识别-AI语音系统架构2022-08-30 25325

-

基于CMSIS标准的软件架构是怎样构成的2021-11-04 2609

-

XILINX FPGA 芯片整体架构是如何构成的2021-10-29 3483

-

基于docker技术的工业App架构是如何构成的2021-09-28 1712

-

UltraScale DSP48 Slice架构的优势是什么?2021-05-24 3481

-

基于ATCA的测试系统架构是如何构成的?2021-05-11 2076

-

AI芯片热潮和架构创新是什么2020-04-24 2104

-

AI芯片热潮和架构创新有什么作用2020-04-23 2376

-

Qualcomm推出人工智能引擎AI Engine2018-03-20 2265

-

Map Service Engine Based On We2010-07-23 542

全部0条评论

快来发表一下你的评论吧 !