易灵思Programmer工具的配置模式过程分析

描述

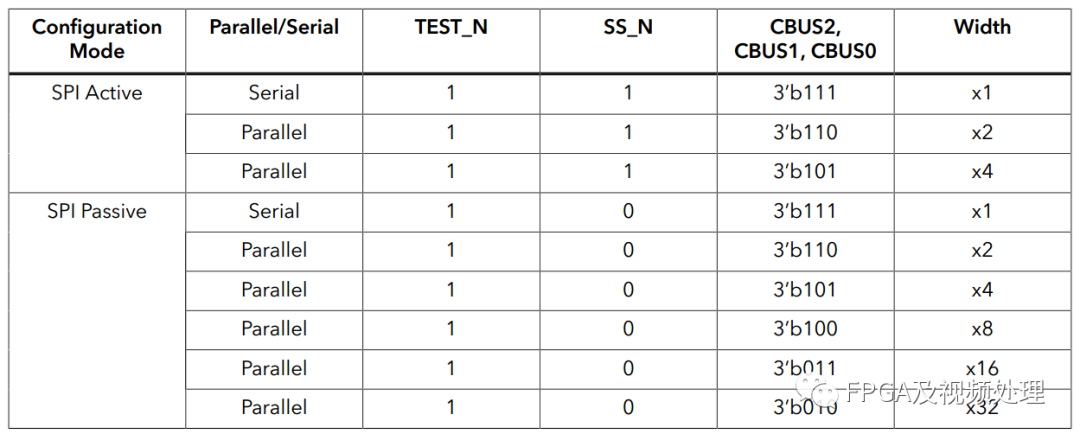

易灵思Trion FPGA的配置模块主要由CBUS[2:0]、SS_N和TEST_N几个信号控制。FPGA进入用户模式前不要对这几个信号进行翻转。

目前易灵思的Programmer工具只支持PS x1模式,x2及更高位宽需要通过外部微处理器,如MCU来操作。

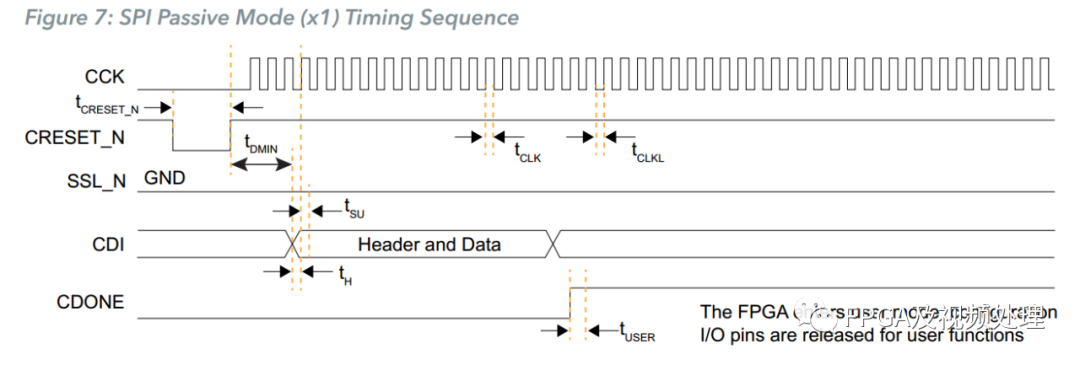

为了保证配置成功,微处理器在发送完最一个配置数据之后,在Trion最好再连续发送100个时钟。实际上也确实有客户因为没有拉时钟而启动不了的情况。

目前测试PS x4模式。时钟为30MHz,tCRESET_N拉低790ns,tDMIN为2us,数据配置完成后又继续发送时钟100个以上。可以启动。用时104ms

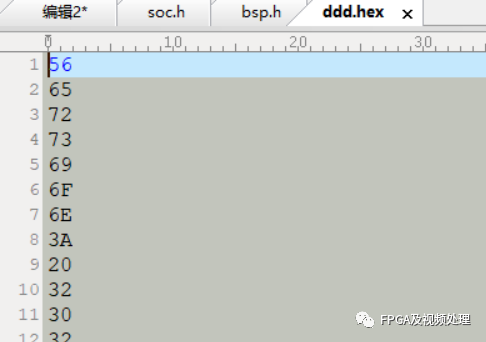

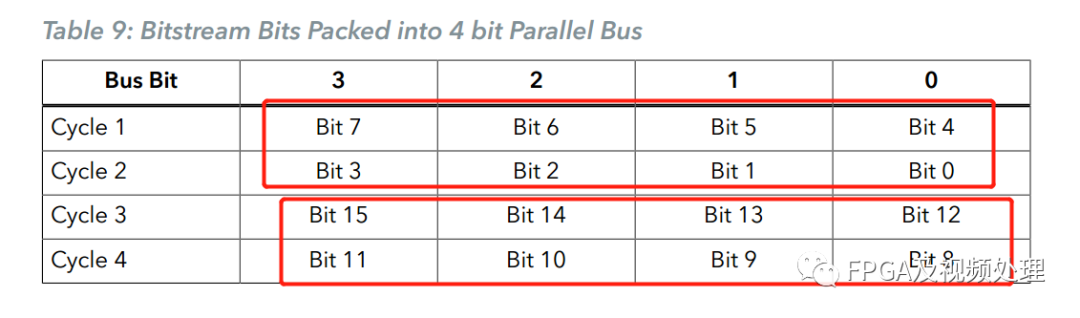

另外要提下数据顺序问题,实际在发送过程是依次发送的。

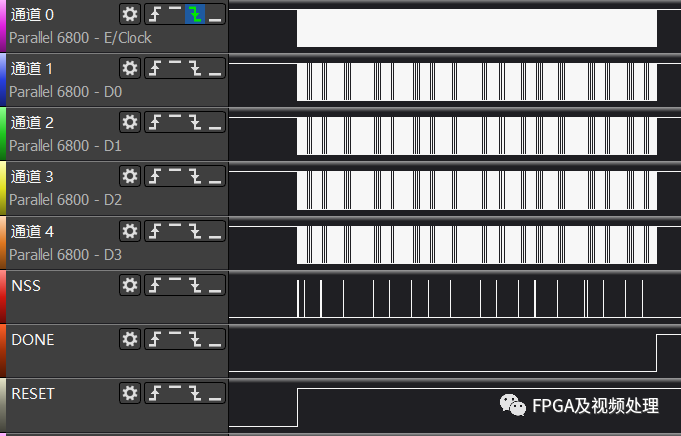

整体配置过程波形如下,SS_N有时会有很多毛刺,时钟之间也会有一些持续拉高的地址,但都不影响 。

审核编辑:gt

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

易灵思FPGA PS配置模式--v72024-12-24 2169

-

易灵思JTAG写入Flash工程的创建过程和烧写操作2022-03-09 6903

-

易灵思内部重配置实现远程更新2023-05-30 2581

-

易灵思Trion FPGA PS配置模式--update(6)2024-07-23 1333

全部0条评论

快来发表一下你的评论吧 !