易灵思JTAG写入Flash工程的创建过程和烧写操作

描述

易灵思在通过JTAG写入Flash时,需要手动创建一个打通JTAG到Flash的bridge,这里我们来介绍下工程创建过程和烧写操作。

一、创建spi_flash_loader工程

1、在工程安装路径"C:Efinity2021.2ipmipefx_spi_loadersource"有用于打通JTAG与Flash路径的源文件。

2、复制工程安装路径 "...Efinity2021.2ipmipefx_spi_loaderfpgaT8Q144_eng_board"下的demo工程到相应的位置,并打开。

3、添加约束C:Efinity2021.2ipmipefx_spi_loaderfpgaconstraint

4、修改需要配置的器件 ;

4、把步骤1中的source文件添加到工程中。

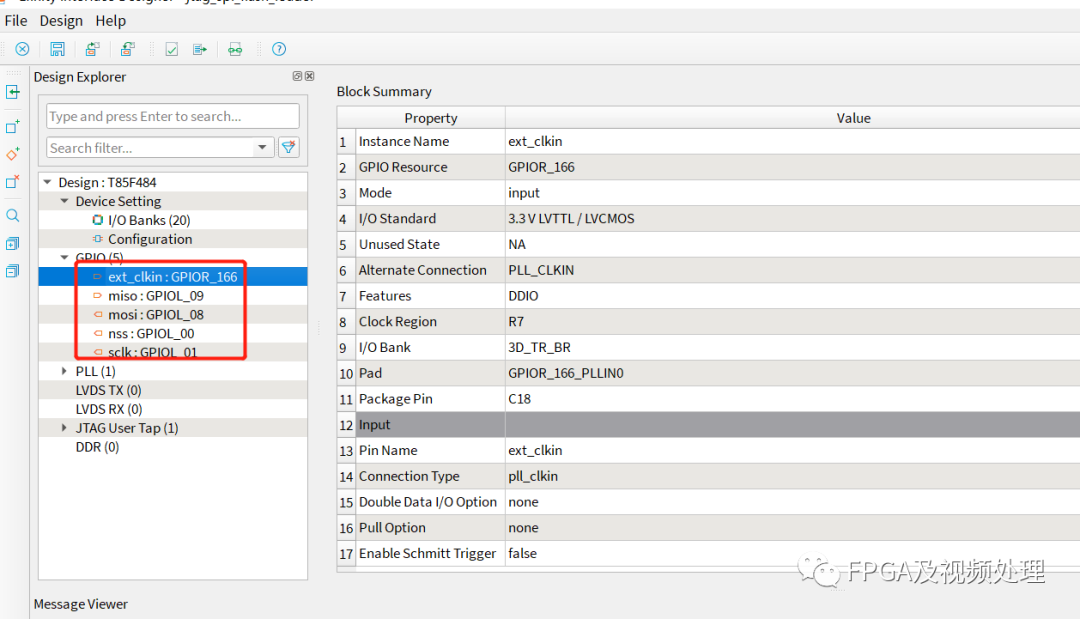

5、修改interface designer中时钟。trion FPGA没有内部振荡器,所以需要外部时钟;主要保留ext_clkin,miso,mosi,nss,sclk等信号。另外注意修改pll的输入输出时钟,其中ext_clkin是pll的参考时钟,Bridge使用的时钟频率最好不要超过50兆

6、删除每个module部分的“'IP_MODULE_NAME”module,如下操作:

把 `IP_MODULE_NAME(adbg_crc32) (clk, data, enable,...);修改成 adbg_crc32(clk,data,enable,...);

7、修改top module信号定义。把用不到的信号屏蔽掉。并在内部重新定义rstn信号并赋值为1。

moduleefx_spi_loader_top(//System// input rstn,input clkin,// input locked,// SPI flash interfaceinput miso,// input miso_1,output sclk,output nss,// output nss_1,output mosi,// output mosi_1,// output wp_n,// output hold_n,);... ...wire rstn;assign rstn =1'b1;8、添加约束。

9、编译即可以生成

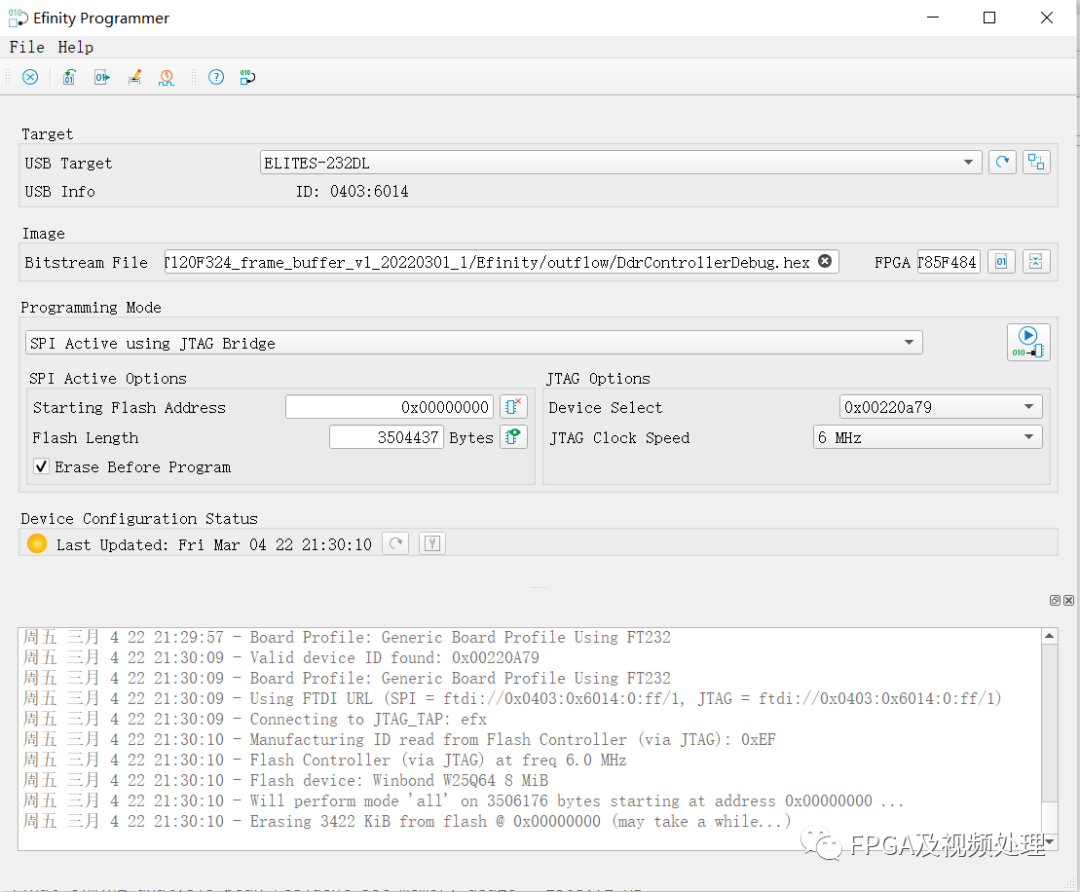

10、烧写过程先在programmer中选择jtag模式,配置spi_flash_loader.bin文件,完成之后,再选择工程的hex文件,并把programming mode中的SPI Active using JTAG Bridge

目前发现修改了FIFO的深度可能 造成Flash的读取验证不成功。所以如果在小器件,比如T8上发现存在资源不够,可以把和mosi_1,miso_1相关的模块屏蔽。

parameter WFIFO_DEPTH = WFIFO_DEPTH_256 * 256;parameter RFIFO_DEPTH = RFIFO_DEPTH_256 * 256;审核编辑:郭婷

-

易灵思FPGA flash操作原理2024-04-09 1862

-

易灵思Jtag_bridge_loader生成-v22024-04-15 2991

-

概述FPGA烧写JIC文件到底是个怎样的过程2020-02-06 4200

-

TMS320F2812片内Flash在线烧写技术2010-12-20 964

-

基于CCS的DSP片外Flash直接烧写设计2009-10-04 4144

-

JTAG接口在线烧写Flash的实现2011-09-16 16532

-

CCS4向内置flash烧写程序过程2015-12-04 1373

-

FPGA配置– 使用JTAG是如何烧写SPI/BPI Flash的?2017-02-08 10568

-

使用JTAG烧写Nand Flash实验解析2017-10-18 2038

-

如何采用DATA进行Flash的在线烧写2019-02-06 4498

-

可供用户修改的FLASH烧写驱动介绍2022-06-08 843

-

FLASH烧写/编程白皮书2025-07-28 481

全部0条评论

快来发表一下你的评论吧 !