FPGA重构优势有哪些

电子说

描述

术语“重构”是指FPGA已经配置后的重新编程。FPGA的重构有两种类型:完全的和部分的。完全重构将整个FPGA重新编程,而部分重构只取代设计的一部分,设计的剩下部分仍正常工作。部分重构不被视为完全重构的特殊情况,因为两者基本相同。对FPGA执行部分重构通过使用与完全重构(JTAG、ICAP、或SelectMAP接口)相同的方法来进行,比特流的结构对于完全和部分重构来说都是相同的。

FPGA重构具有以下几个优点。它允许多个设计共享同一个FPGA结构,这反过来又降低了FPGA的面积、成本和系统复杂性。完全和部分重构为许多FPGA的创新应用程序提供了可能,负责,高昂的成本将影响应用程序实现。利用FPGA重构优势的一些应用如DSP、音频或视频处理器等,他们根据用户输入,由包括集成深度包检测的通信控制器修改处理算法,以改变基于协议的数据包处理器。

很多工业和学术性的FPGA重构方面的研究不断产生有价值的应用、研究论文和学位论文。

虽然部分重构技术不是一项新功能,也不是主流的研究方向,但是设计和实现流程、工具支持甚至名词术语都在不断发展,用户界面越来越友好。最终目标是向FPGA开发者提供简单和透明的设计流程,无需详细了解配置逻辑和比特流结构。

部分重构是一项复杂过程,在设计实现。工具流程和重构本身的过程中充斥着多重挑战。面临的一个挑战是在FPGA配置的变化过程中,完成平滑切换而无须中断剩余设计功能或损害其完整性。而在完全重构过程中,FPGA架构和IO不能保持在复位。另一项挑战是在改变过程中,防止设计的未改动部分进入无效状态。设计者必须正确界定和约束未改动和改动部分之间的接口,这样,FPGA物理实现工具才能进行配置并使用完全相同的布线资源。

有三个部分重构流程可用于XIlinx FPGA;基于差异的(difference based)、基于分层的(partition based)及使用动态重构端口。

基于差异的部分重构

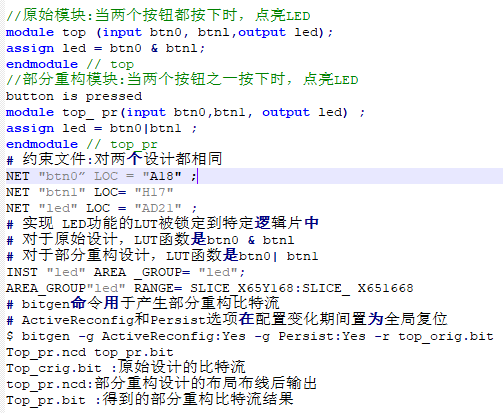

其于差异的部分重构2最活合用于将小型设计转化为LUT方程、IO特征和BRAM中的内容。以下是一个简单的、 基于差异的部分重构代码和流程举例,它可以运行在Xilinx的ML605 Virtex-6 开发板上。

上面例子中基于差异的部分重构流程包括以下步骤:

(1 )编译top模块。结果是比特流文件top_orig. bit。

(2)编译top_pr模块。结果是布局布线后文件top_pr. ned。

(3)使用top._orig.bit比特流和top_pr.ned,生成包含两个设计之间LED LUT方程差异的比特流。

基于分层的部分重构

与基于差异的重构不同,基于分层的部分重构流程支持重构大型部件FPGA设计。PlanAhead工具只支持Xilinx Virtex-6系列(不支持Spartan-6 FPGA), 它提供了用于配置、实现和使用分层管理部分重构项目的集成环境。设计和实现流程的简要概述如下所示:。

1.FPGA开发者指定待配置的部分设计。

2.在FPGA芯片上包含所需逻辑、嵌人式存储器、IO和其他资源的区域。

3.开发者定义覆盖该区域的所有可能设计变量。

4.PlanAhead工具管理所有诸如编译设计的细节,包括管理多个网表、静态的和可重构的设计部分,执行DRC,并产生合适的比特流。

Xilinx应用提示XAPP8833)提供了使用部分重构的示例,以允许嵌人式PCI Express接口模块的快速配置。

动态重构端口

改变Xilinx GTX收发器、混合模式时钟管理器(MMCM)和SystemMonior原语设置的另一种方法,是使用动态重构端口(DRP)。DRP提供了一个简单的用户逻辑接口,不需要更多地了解配置寄存器和比特流结构。例如,DRP允许输出时钟频率、相位和MMCM4的占空比动态变化。

原文标题:FPGA知识汇集-FPGA的重构

文章出处:【微信公众号:FPGA技术联盟】欢迎添加关注!文章转载请注明出处。

-

关于FPGA可重构技术分析2022-11-03 1434

-

FPGA有什么优势?FPGA的应用方向是什么?2021-10-08 2374

-

FPGA的重构是什么,具有哪些要点2021-07-02 3597

-

怎么实现基于FPGA的动态可重构系统设计?2021-05-10 3028

-

怎么实现基于FPGA可重构智能仪器的设计?2021-05-06 1574

-

如何去实现FPGA动态部分的重构?2021-04-29 4020

-

如何利用ARM与FPGA设计重构控制器?2019-08-09 1593

-

有什么FPGA可重构方法可以对EPCS在线编程?2019-07-31 2462

-

基于CPLD的FPGA快速动态重构设计2017-11-22 1579

-

FPGA可重构设计的结构基础2011-05-27 3989

-

基于对EPCS在线编程的FPGA可重构方法2009-12-08 1764

全部0条评论

快来发表一下你的评论吧 !