碳基电子技术的进展、应用与挑战

电子说

描述

近六十年来,以硅为核心材料的半导体技术,特别是CMOS集成电路技术推动了人类信息社会的深刻变革,但也逐渐接近其物理极限和工程极限,全球半导体产业已经进入后摩尔时代。半导体性碳纳米管具有高迁移率、超薄体等诸多优异的电学特性,因此成为后摩尔时代新型半导体材料的有力候选。基于碳纳米管的碳基电子技术历经二十余年发展,在材料制备、器件物理和晶体管制备等基础性问题中也已经取得了根本性突破,其产业化进程从原理上看已经没有不可逾越的障碍。因此,本文将着重介绍碳基电子技术在后摩尔时代的本征优势,综述碳基电子技术的基础性问题、进展和下一步的优化方向,及其在数字集成电路、射频电子、传感器、三维集成和特种芯片等领域的应用前景。最后,本文还将分析碳基电子技术产业化进程中的综合性挑战,并对其未来发展做出预测和展望。

1引言:碳基电子技术的发展背景与历史机遇

20世纪40年代末,巴丁(Bardeen)、布拉顿(Brattain)和肖克利(Shockley)经过长时间的研究后发明了点接触型和结型晶体管,开启了半导体技术的研究浪潮;20世纪50年代末,基尔比(Kilby)和诺伊斯(Noyce)分别独立设计并制作了最早的集成电路,芯片技术的雏形得以问世;1960年左右,贝尔实验室和仙童半导体公司先后发明了硅基场效应晶体管(Metal-Oxide-Semiconductor-Field-Effect-Transistor,MOSFET)和互补型金属氧化物半导体技术(Complementary Metal Oxide Semiconductor,CMOS),MOSFET和CMOS随后成为了集成电路的基础单元并被使用至今。至此,历经二十余年的早期探索,以集成电路为核心的硅基半导体技术才终于步入正轨并开始高速发展。依循摩尔定律和Dennard微缩定律这两个半导体技术的商业规律和技术理论,硅基集成电路的集成度和性能每隔18~24个月就翻一番,五十余年来不断推动着人类信息技术的蓬勃发展与深刻变革。然而从2000年起,硅基晶体管的微缩难度不断增大,人们虽然引入了各种复杂的技术解决方案如应变硅(StrainedSi)技术、高k金属栅(high-kmetalgate)技术、鳍式晶体管技术(FinFET)和深紫外(DUV)乃至极紫外(EUV)光刻技术等等。但硅基晶体管的微缩速度却在持续降低、微缩收益也在逐渐收窄,硅基集成电路更是遇到了工艺上的瓶颈(频率瓶颈或功耗墙问题)和架构上的瓶颈(冯诺依曼架构的内存墙问题)。随着先进技术节点的艰难推进,硅基晶体管和集成电路也逐渐接近其物理极限和工程极限,全球半导体产业步入后摩尔时代[1,2]。

在后摩尔时代,虽然信息技术的基石—半导体产业面临着巨大的技术挑战和工程困难,但人类社会对数据计算能力和存储能力的需求却与日俱增。因此,半导体学界和业界在艰难发展硅基技术的同时,也越来越频繁地将其目光和精力放到新材料和新器件的探索中来,以求从根本上延续和拓展摩尔定律。在众多新型半导体材料中,碳纳米管(Carbon-Nanotube,碳管或CNT)由于其独特的准一维结构和优异的电学性质而受到了人们的高度重视。国际半导体路线图委员会(ITRS)早在2009年就推荐碳纳米管作为延续摩尔定律的未来集成电路材料选择[2,3];美国国防部先进研究计划局(DARPA)在2018年启动的“电子复兴计划”(ERI)中,投入高达15亿美元的经费,希望从系统架构、电路设计和底层器件三个方面探索未来的集成电路技术,其中最大的项目就是支持相关学术团队和芯片制造企业开展碳纳米管集成电路技术的研究和产业化[4];国际商业机器公司(IBM)和台积电(TSMC)等企业的半导体研发团队近年来也在持续跟进碳纳米管电子技术[5,6]。对碳纳米管这一新型半导体材料的广泛关注和看好根源于其电子学应用上的材料器件本征优势,因而催生了一系列对材料、器件物理、加工工艺乃至集成技术的深入研究。

自从1991年碳纳米管被发现以来[7],人们就对这种天然的纳米尺度准一维导体充满了兴趣,并深入系统研究了其材料特点。首先,碳纳米管可分为单壁碳纳米管和多壁碳纳米管,多壁碳管可视作由单壁碳管嵌套而成,由于单壁碳管与多壁碳管相比缺陷较少、结构简单、可控性好,而且半导体性比例高,因此碳基电子技术主要基于单壁碳管发展,下文所述碳纳米管一词也均默认为单壁碳纳米管。其次,碳纳米管可以看作由二维的单层石墨烯沿特定方向卷曲而成的空心圆柱状准一维晶体,其卷曲方向决定碳管的手性从而决定其晶格和能带结构,其表面碳原子间的成键方式为sp2杂化。根据手性不同,碳纳米管还可分为半导体性和金属性的,这种电子性质的多样性使碳纳米管具有广泛的应用前景,包括晶体管、互联和传感等等,下文主要讨论半导体性碳纳米管。从碳纳米管的基本特性出发,人们归纳了其主要的电子学材料优势:(1)碳纳米管的准一维结构大幅减小了其载流子的散射相位空间,因此具有较低的散射概率、较高的载流子迁移率和较长的平均自由程,是理想的低损耗甚至无损耗沟道材料;(2)碳纳米管的sp2杂化碳原子表面没有悬挂键,因此表面散射较弱,理论上可以兼容各种高k栅介质材料;(3)常见的碳纳米管直径仅为1~2nm,与体型半导体材料相比更容易受栅极调控,因此对短沟道效应的免疫能力较强;(4)碳纳米管的导带与价带在低能态下高度对称,电子与空穴具有相同的有效质量和迁移率,因此尤其适合用来制作CMOS集成电路。这些优势的具体表现将在下文深入讨论。

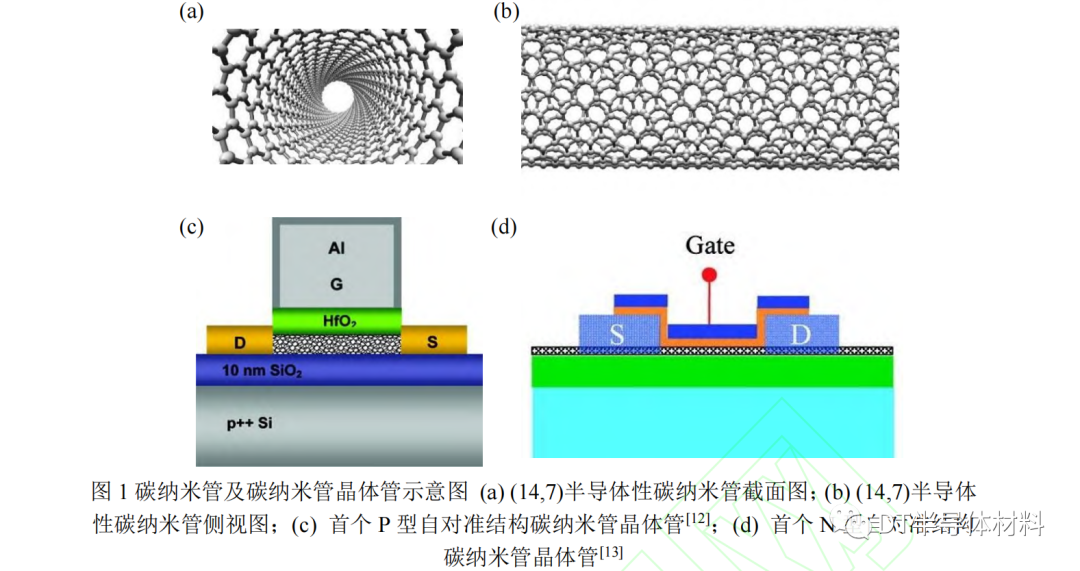

经过大量的早期探索,代尔夫特理工大学的Dekker等人和IBM的Martel等人终于在1998年分别独立制造出了第一个碳纳米管场效应晶体管(CNTFET)[8,9]。然而,最早的碳管器件性能尤其是开态电流远逊于同时期的硅基晶体管,这是因为碳纳米管场效应晶体管本质上是一种肖特基场效应晶体管,当沟道长度小于其平均自由程时(即准弹道甚至弹道输运),源漏电流主要受碳管和接触电极之间的肖特基势垒决定。而Dekker等人制造的碳管晶体管使用Pt或Au作为电极,接触势垒较大[8,9]。因此,2003年AliJavey和DaiHongjie等人经过大量尝试,发现可通过使用高功函数的金属钯(Pd)作为碳纳米管的电极来得到无势垒P型欧姆接触的弹道晶体管,其室温下开态电导接近量子电导的理论极限,首次展现了碳纳米管晶体管的高性能优势[10]。2007年,北京大学团队实现了以低功函数的金属钪(Sc)作为碳纳米管电极的N型欧姆接触弹道晶体管,其性能达到了P型碳纳米管晶体管的最好水准[11]。这两个工作展示了碳纳米管在场效应晶体管和CMOS集成电路应用上的巨大性能潜力,自此以后碳纳米管电子学领域的主要研究工作也都集中在这两方面。

经过这些原始探索后,以碳纳米管场效应晶体管和CMOS技术为核心的碳基电子技术终于开始迅速发展,在材料、器件结构、加工工艺和系统集成方面不断突破,并在数字电路、射频电子、传感探测、三维集成和特种芯片等电子学应用中充分展现了其优势与特色。碳基电子技术正如硅基半导体技术一样,已经完成了丰富的早期探索、进行了系统的技术积淀、得到了大量的资助支持,成为了后摩尔时代的重要技术方向,甚至在逐步走向实用化和产业化。有鉴于此,本文将介绍碳基电子技术在后摩尔时代的本征优势,重点讨论碳基电子技术的基础性问题与进展,梳理碳基电子技术的应用场景与发展方向,最后分析碳基电子技术产业化进程中的综合性挑战,并展望碳基电子技术的未来前途。

2碳基电子技术在后摩尔时代的本征优势

作为现代信息技术的硬件基础,集成电路自二十世纪六十年代发展至今,已然成为了一个极其成熟又极其复杂的高技术产业。对于集成电路产业发展的著名预测—摩尔定律,也因面临芯片成本急剧上升的经济学阻碍和微纳加工原子极限的物理学阻碍而开始逐渐失效,集成电路产业进入了后摩尔时代。后摩尔时代电子技术的核心需求主要分成三个方向:即more Moore、morethan Moore和beyond Moore或beyond CMOS。

在more Moore方面,集成电路领域虽然有器件结构、沟道材料、互联导线、高k金属栅、工艺设备等多个研究方向,但业界的核心需求仍是CMOS器件的性能提高、功耗下降,并对晶体管和电路进行尺寸缩减。近20年来,人们为了获得更高的器件能效,设计了各式各样的晶体管结构,如鳍式晶体管(FinFET)、全耗尽型绝缘层上硅晶体管(FD-SOIFET)、GAA结构的硅纳米片晶体管(SiNanosheet FET or MBCFET)和硅纳米线晶体管(SiNanotube FET)、二维材料晶体管(2DFET),以及本文所讨论的碳纳米管晶体管。在晶体管层面,一种沟道材料是否具有应用潜力、是否值得研究,首先需要考虑其在高性能和低功耗方面是否存在材料本征优势。而相关理论、仿真和实验研究表明,碳纳米管具有较高的性能潜力,反映为其载流子的平均自由程较长(不同散射机制对应数十纳米到微米量级)、低场迁移率较高(1×105cm2/(Vs))、强场饱和速度是硅的四倍(4×107cm/s)、弹道注入速度超过硅的三倍(3×107~4×107cm/s)[14-16]。这些特点有利于提高器件性能和电路速度,最新实验结果表明120nm栅长的碳纳米管晶体管电流密度在1V工作电压下可达1.18mA/μm、环振电路门延时可低至11.3 ps[17],该结果超过了同尺寸的硅基器件性能,充分展示了碳纳米管的高性能潜力。其次,碳纳米管作为直径1nm左右的准一维超薄体,其本征量子电容较小,容易被栅极调控,因此其载流子屏蔽自然长度较小,有利于抑制晶体管的短沟道效应。综合来看,碳纳米管相比于体型半导体更易于降低器件的工作电压和能耗:实验研究表明碳纳米管晶体管的工作电压甚至可降低到0.6V以下[18],动态功耗随之大幅降低;又由于碳纳米管的开态性能较高,在降低工作电压时,不需要降低阈值电压来弥补性能,理论上能有效抑制关态泄漏电流,降低静态功耗。以上特点使碳纳米管晶体管尤其符合现今集成电路产业功耗驱动的制程进化趋势(Power-Driven Technology Transition)。综上,碳纳米管晶体管理论上是一种兼顾高性能低功耗特性的器件,实验和计算结果表明其与传统晶体管相比具有5到10倍的综合能效优势,这种能效优势甚至能在亚10nm的实际物理栅长器件中得以保持[19]。可以说,碳纳米管晶体管完全具备延续摩尔定律所要求的材料器件本征优势以及微缩潜力,是后摩尔时代moreMoore方向的重要技术路线。在morethanMoore方面,集成电路的发展不再是一味的缩减晶体管尺寸和单元面积或提高单元器件能效,而是在系统层面上关注功能集成、集成效率和综合算力,研究重点包括但不限于应用导向的功能器件和三维系统集成技术(先进封装、三维异质集成、Monolithic三维集成),而基于碳纳米管材料的碳基电子技术恰好在功能器件和三维集成方向上具有独特优势。由于碳纳米管具备载流子迁移率高(速度快)、比表面积大(高灵敏度)、碳-碳键强度高且沟道体积小(辐照抗性好)、工作温区宽、衬底兼容性强等材料特性,近年来研究者们基于碳纳米管实现了多种功能器件,如高速射频器件和电路、超灵敏生物和气体传感器、自修复抗辐照芯片、柔性器件和电路等等[20-25]。整体而言,碳基电子技术不仅可以提供多种多样的功能器件,还能在多种器件的性能指标上具有一定优势或特色,这些具体进展将在下文展开讨论。在三维集成方面,研究者们希望在计算单元与存储单元乃至信息获取单元(传感器或探测器等)之间快速传递数据,从而提高内存访问带宽并突破内存墙、降低系统能耗并提高计算效率。要想实现这一点,我们需要实现高密度、高速的数据传输通道(I/O接点),而业界基于硅基集成电路所尝试的主要是三维封装技术和TSV三维集成技术,前者技术难度和成本较低,但I/O接点密度低、寄生效应强,后者I/O接点密度有所提高但每个通孔尺寸仍然在数十至百微米,只能提供有限的数据传输带宽。硅基集成电路因其工艺热预算有限(如后道工艺不能超过400摄氏度),难以在同一硅片上制造多层电路并对准层间高密度I/O通孔,因此其三维集成能力有限[26]。而碳纳米管技术由于其低温加工潜力,理论上可以在制造第一层晶体管及互联后,继续制造高密度、精细化(百纳米尺寸)的数据通孔和第二层乃至多层电路,从而有望实现单片(Monolithic)三维集成[27]。理论计算表明这种基于碳纳米管器件的三维集成系统相比于传统计算系统具有1000倍的能效优势[28],结合碳纳米管的功能器件多样性和三维集成潜力,未来或许可以实现丰富多样的超高能效碳基三维片上系统(3D Systemon Chip)。

在beyond CMOS方面,电子开关被研究人员重新定义,诞生了众多与传统CMOS工作机理不同的器件(亚60器件、自旋电子器件、谷电子学器件等),以期望解决CMOS器件在增加密度、提高性能、降低能耗时所遇到的原理性问题。其中,亚60器件由于其低功耗潜力受到了人们的广泛关注,重点包括两种器件:隧穿晶体管和负电容晶体管。虽然它们都可以实现亚60特性,但前者电流密度过低,后者工作机理不明确,因此实用化难度较高、概率较低[29]。与这两种器件相比,基于碳纳米管实现的狄拉克冷源晶体管可以在室温下同时实现小于40mV/decade的亚阈值摆幅和接近1mA/μm的开态电流密度,突破了传统CMOS器件亚阈值摆幅的玻尔兹曼极限,其工作电压可低至0.5V,是一种同时具备高性能和低功耗特性的新型晶体管,其应用潜力受到了业界的高度重视[30]。

综合来看,碳基电子技术在后摩尔时代的不同发展方向中均具有很好的技术优势和特色,究其原因是碳纳米管作为半导体沟道材料具有较强的电子学本征优势。

3碳基电子技术的基础性问题与进展

碳纳米管作为直径只有1~2nm的准一维半导体,其独特的低维特性决定了其材料特性和器件物理都与传统半导体有所不同。本章将围绕着碳纳米管的材料制备,和碳纳米管晶体管的金半接触、栅极工程、双极性抑制技术,以及碳纳米管器件的集成工艺进行讨论,重点分析其中的基础性问题和技术挑战,最后回顾近年来碳纳米管晶体管的尺寸缩减和综合性能提升。

3.1碳纳米管材料的制备:生长、提纯和自组装

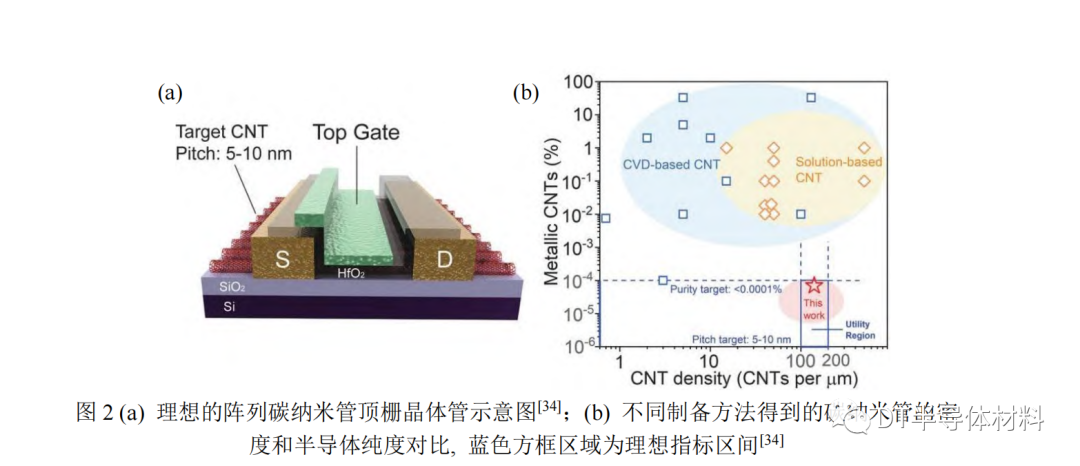

要兑现碳基电子技术在后摩尔时代的种种优势,首先需要合适的半导体性碳纳米管材料。而根据用途不同,半导体性碳纳米管材料主要可分成三类:单根碳纳米管、网络状碳纳米管薄膜和碳纳米管平行阵列。其中,单根半导体性碳纳米管主要用于早期的理论研究和原型器件展示;中高纯度、低密度的网络状碳纳米管薄膜可用于制造性能要求不高的电路(如显示驱动电路、柔性传感电路等);超高纯度、高密度的碳纳米管平行阵列则是高性能晶体管和集成电路的理想材料(图2)。根据理论分析,理想的阵列碳纳米管密度为100~200根/μm、均匀间距为5~10nm、半导体性纯度至少大于99.9999%(“6个9”)、管径为1.2~1.7nm,并且需满足晶圆级覆盖面积[31-33]。为了得到这种理想的碳纳米管材料,目前主要有两种思路:CVD法直接生长、基于溶液法的提纯和自组装,本小节将结合半导体性纯度、手性与管径、排列密度与可控性、可扩展性等指标分别讨论不同技术路线的发展现状和未来挑战。

CVD直接生长法最明显的优势就是可以在绝缘衬底上直接得到平行排列、表面洁净、缺陷较少的碳纳米管阵列,因此受到了学界的广泛关注,进行了大量尝试。比如在定向排列方面,CVD法通过生长过程中的气流诱导、基底晶格边界诱导或其他诱导手段,可以获得天然平行的阵列碳管[35,36]。在半导体性纯度方面,CVD法通过设计特定结构的催化剂来调控生长碳管的手性,如利用(1010)晶面富集的Co6W7作为催化剂可得到最高占比98.6%的(14,4)手性碳管和99.8%的半导体性碳管[37]。在碳管密度方面,有研究者同样基于特殊结构的催化剂设计来克服高温下催化剂的聚集和失活现象,从而实现了密度高达130根/μm的阵列碳管生长[38]。然而,这些基于CVD法直接生长的阵列碳管大都只具备高密度、高纯度或定向排列中的某一个指标[35-38],远无法满足集成电路应用的综合需求。因此研究者们提出了另一种思路:即用CVD法生长定向排列的中高密度阵列碳管,再通过各种后处理方法去除金属性碳管,从而得到高纯度的碳管阵列。其中后处理方法最洁净、对碳纳米管损伤最小的是2013年Jin等人提出的一种热烧蚀法。这种方法通过在CVD法生长的阵列碳管上覆盖一层有机物热敏材料,然后施加合适的栅压来“关闭”半导体性碳管、施加合适的源漏偏压来使金属管产生大电流,从而使金属管发热并蒸发热敏胶,最后用氧等离子体刻蚀掉裸露出的金属性碳管[39]。该方法对碳管的损伤较小且选择性也较好,但受到热敏材料的种类和厚度限制,只适用于较低密度的碳管阵列。此外,CVD法直接生长再通过后处理去除金属性碳管的技术方案存在一个本征缺陷:即无法保证碳管间距的均一性。在早期研究中,单个碳纳米管器件内碳管间距和数量的随机性并不会产生显著影响。但在大规模集成电路等实际应用中,由于器件实际尺寸较小,每个器件中的碳管总数并不多,碳管间距波动造成的碳管数量波动会产生较明显的器件性能波动,从而损害电路均一性。整体来说,目前采用CVD法直接生长的阵列碳纳米管材料在半导体纯度和密度等方面都与理想指标相差甚远,需要进一步研究探索。

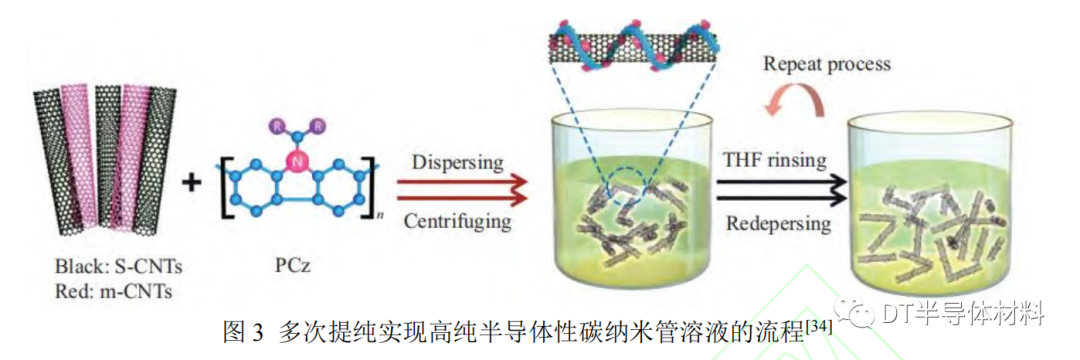

基于溶液法的提纯和自组装技术则是理想碳纳米管材料制备的另一有效路径。该技术的核心思想是:先对电弧放电法或CVD法生长得到的原始碳纳米管进行多次溶液分散和分离提纯,从而得到超高纯度甚至手性富集的半导体性碳纳米管溶液(图3),然后再进行自组装使其排列到目标基底上去。这一技术经过二十余年发展至今,获得了较好的成果,能初步满足高性能集成电路应用对碳纳米管材料的各种要求[34],因此接下来本文将分环节简要讨论该技术的原理、进展和现存问题。

就分散提纯方法而言,根据分散剂与碳纳米管的作用方式不同可分为共价分离和非共价分离。其中,共价分离法需要对碳纳米管表面进行官能团化,这破坏了碳纳米管的完美晶格结构,从而在器件中引入散射位点并降低电学性能,因此不是一个很好的选择。非共价分离则以特定的表面活性剂、共轭小分子、共轭聚合物或DNA羟基链等材料作为分散剂,分散剂通过范德华力选择性地包覆在半导体性或金属性碳纳米管表面,从而造成半导体性和金属性碳管与分离介质之间的相互作用出现明显差异,最后再用柱色谱法、密度梯度离心法等方法进行分离[40-46]。需要注意的是,在分散过程中长时间的超声会大幅缩短碳管长度并产生表面缺陷,因此我们需要进行分子设计以加强分散剂与碳管之间的相互作用强度,从而减少分散所需的时间;要想获得超高纯度(>99.9%)的半导体性碳管,分散剂和分离方法还需要对半导体性碳管具备尽可能强的选择性。基于这两点考虑,共轭聚合物这种与碳管范德华力相互作用较强的分散剂材料受到了研究者们的重点关注[34,44-47]。共轭聚合物中的共轭骨架可与碳纳米管表面形成π-π电子云相互作用,从而紧密缠绕在碳管表面,有助于分散和分离过程;共轭聚合物上的烷基链则帮助半导体性碳管在有机溶剂中悬浮,悬浮能力的强弱会直接影响分离过程的有效产率;共轭聚合物的分子量也会影响选择性和产率,一般认为分子量越大则产率越高、管径更小。基于以上原理,通过共轭聚合物的分子设计,研究者们利用噻吩[44]、联吡啶[45]、咔唑[46]、聚咔唑[47]等聚合物作为分散剂,得到了半导体性纯度可超过99.99%的碳纳米管溶液,相比CVD法具有明显优势。通过分子设计和工艺优化,基于溶液法的分散提纯技术理论上能获得超高纯度的半导体性碳管,但随之而来的问题是:如何快速、大规模、精准地表征超高半导体性纯度。现有的光学表征技术如拉曼光谱分析只能检测到最高99%的半导体性纯度[48],而基于场效应晶体管的电学表征技术虽然可以得到极高精度的结果(可分辨金属性碳管比例~0.0001%)[34],但其工艺流程长、表征速度慢、表征规模有限,同样不能满足未来碳基电子技术规模化应用时的材料表征要求,因此我们需要进一步研究开发碳管纯度的高通量表征技术。此外,共轭聚合物的使用也可能造成潜在的问题,这主要包括两方面:一是共轭聚合物中的极性原子或基团可能与碳管发生电荷交换形成电偶极子甚至引入界面态或改变碳管的能带结构,这不利于形成可控的碳纳米管金半接触并对沟道内的载流子输运造成了未知影响;二是碳管表面的共轭聚合物可等效为一层低介电常数、疏松不均匀的介质层,从而复杂化栅介质的生长机制与界面物理、降低碳纳米管晶体管的栅控效率。因此,在使用共轭聚合物作为分散剂进行碳管的分离提纯时,我们需要评估共轭聚合物的残留程度并尽可能地将其去除干净,以避免对后续的器件制造产生负面影响。

得到了高纯度的半导体性碳纳米管溶液后,下一步就是将碳管排列在绝缘基底上以供制造器件和电路。根据排列过程中准一维碳管的取向性差异,可分为介观尺度准各向同性的网络状碳纳米管薄膜和高度各向异性的碳纳米管平行阵列。

网络状碳纳米管薄膜可通过滴涂法、静置沉积法等方法制备,其工艺简单、碳管排列完全无序或具备一定宏观取向性。由于网络状碳管薄膜中存在大量碳管-碳管结(CNT-CNTJunction),载流子在其中的输运方式为渗流输运,实际输运路径具备一定随机性,输运长度通常大于器件设计的沟道长度[49]。虽然网络状碳纳米管薄膜在半导体性纯度较高时也能用于制造性能尚可的晶体管和均一性较高的电路[50-53],但这种材料存在一些本征限制:首先,载流子在输运过程中需要通过多个碳管-碳管隧穿结,其有效迁移率大幅降低,难以发挥碳纳米管材料的高性能本征优势;其次,即使在一切理想的情况下,即碳管手性全同、工艺不引起任何不均匀性,仅碳管取向随机性造成的电学波动就会限制晶体管在开态和关态性能间折中,即无法将器件的开态和关态指标(如跨导和SS)同时做好[54]。因此,面向高性能电子学应用的碳纳米管材料,只能是超高纯度、超顺排的碳纳米管阵列。

碳纳米管阵列的平行自组装技术根据其原理可分为:基于Langmuir膜法(包括Langmuir-Blodgett膜法和Langmuir-Scheafer膜法,即L-B膜法和L-S膜法)的自组装技术[55,56]、基于蒸发原理的自组装技术[57,58]、基于模板法的自组装技术[59,60]和维度限制自组装技术(DimensionLimitedSelfAlignment,DLSA)[34]。接下来本文将结合密度、间距均一性、排列取向性和可扩展性(产率和晶圆级覆盖能力)来讨论不同方法的优势和问题。L-B膜法或L-S膜法都是通过水-空气界面处碳管悬浮液的精细化压缩和释放过程自动调整其方向性,经过多个周期后,碳管将垂直于压缩方向紧密地平行排列,再经过垂直提拉(L-B膜)或水平提拉(L-S膜)将碳管转移到基底上,就得到了碳纳米管平行阵列[55,56]。然而,基于Langmuir膜法的自组装技术要么得到了仅40根/μm的碳管阵列[55]、要么得到了高达500根/μm的碳管阵列[56],均不满足理想碳纳米管阵列在密度上的要求(100~200根/μm),所制造的器件要么电流密度较低[55]、要么栅控效率较差[56]。在可扩展性方面,由于Langmuir膜法需要多个压缩-释放循环,该方法的产率较低,而且尚无工作展示其能实现晶圆级别的覆盖率。由溶剂蒸发驱动的碳管自组装技术则是将目标基底(固体)垂直浸泡在包含碳管的水溶液[57]或有机-水分层溶液[58]中,然后缓慢提拉基底,利用水溶剂[57]或有机溶剂[58]在气-液-固三相界面上的蒸发过程来将碳管排列到基底上。通过这种方式,可以得到取向角偏差在20°以内、密度约15根/μm[57]或50根/μm[58]的条带状碳纳米管阵列薄膜。该方法除了密度不达标外,条带状的覆盖特点更使其不可能用于碳基器件的规模集成。基于模板法的自组装技术则包括自上而下和自下而上两种思路,前者通过基底的图案化和选择性的表面化学修饰来实现可容纳碳管的人造“沟槽”,沟槽区域经化学修饰后可以吸附碳管,当沟槽宽度远小于碳管平均长度时,碳管由于空间限制就近似平行地排列在沟槽内部[59]。这种方法虽然可以得到晶圆级别的碳管阵列,但由于碳管只存在于沟槽内部,其有效覆盖率并不高(常低于30%),并且碳管取向性和间距均匀性在沟槽内部会大幅下降,产生较多的局部排列缺陷。这些问题虽然可以通过降低沟槽宽度和提高沟槽密度来改善,但其亚10nm精度的图形化成本是十分昂贵的。自下而上的碳管阵列模板法自组装技术则是由北京大学团队的孙伟教授提出的[60]:首先利用DNA“折纸”技术构建等间距的沟槽阵列和沟槽内部的悬浮脱氧核苷酸链,再对碳纳米管表面作互补DNA链修饰,利用脱氧核苷酸的配对原理实现沟槽对碳纳米管的选择性限制和自组装,最后再化学去除DNA分子就能得到表面相对洁净、取向角偏差极小(90%在7°以内)、密度约为40~120根/μm的等间距碳纳米管阵列。这种技术在密度、取向性和间距均匀性等方面都具有良好表现和优化潜力,但其产率较低(DNA模板的合成较慢、覆盖面积较小)、成本较高(DNA原料和合成价格较高),暂时不适用于碳基电子技术的产业化,有待进一步发展以满足28nm节点后的碳基集成电路应用。

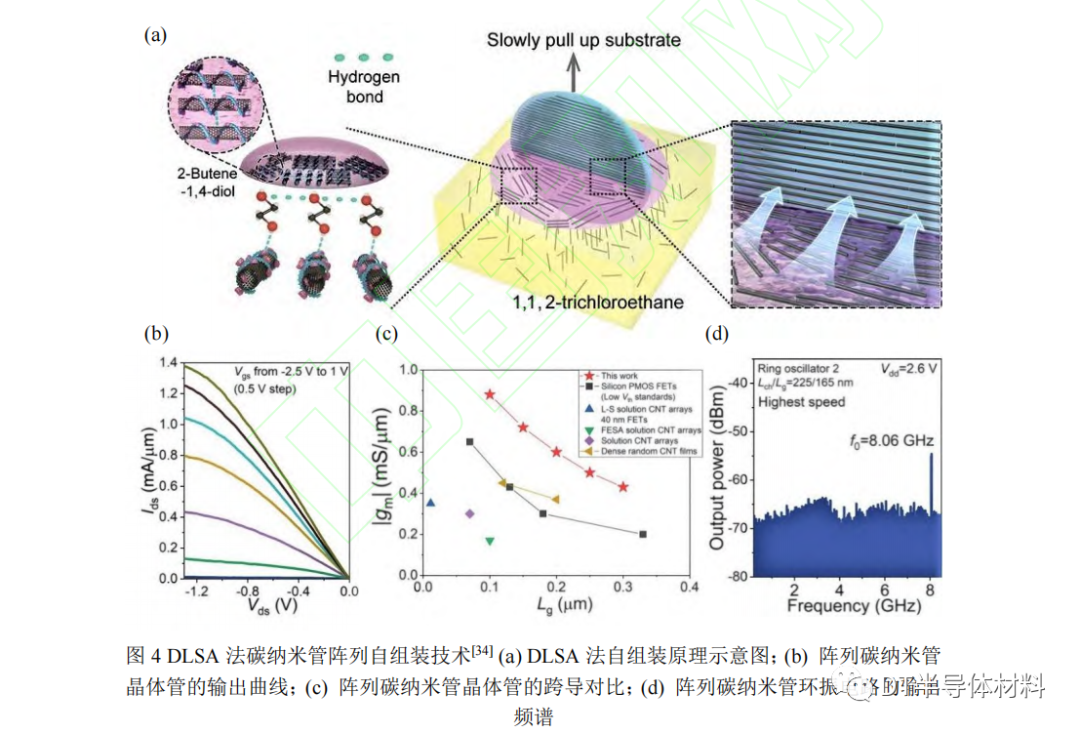

由北京大学团队提出的维度限制法碳纳米管自组装技术主要包括两个维度限制过程[34](图4):一是经过提纯的半导体性碳纳米管从体溶液中被吸引到双液相界面(即碳管从三维空间转移到二维平面),二是双液相界面上的碳纳米管受晶圆提拉作用和顶层溶剂的蒸发对流作用慢慢转移到固-液-气分界线上进而连续地沉积在晶圆表面(即碳管从二维平面向晶圆与液面的一维交线处转移)。通过优化液相界面性质、晶圆提拉速率和溶剂蒸发速率、悬浮液中的碳纳米管浓度以及共轭聚合物与碳纳米管表面的相互作用强度等工艺参数,该技术首次得到了100~200根/μm的可控密度、取向角偏差小于8.3°、碳管直径为1.45±0.23nm的晶圆级理想碳纳米管平行阵列[34]。此外,北京大学团队还基于前文提到的溶液法分散提纯技术,以聚咔唑共轭聚合物作为分散剂,经过多次超声分散、高速离心分离和过滤筛选,最终得到了纯度至少为99.99995%(批量电学器件表征结果)的半导体性碳纳米管溶液[34]。结合高度优化的溶液法分散提纯技术和维度限制的自组装技术,该团队首次展示了同时具备超高半导体性纯度、理论最优密度和良好取向性的晶圆级碳纳米管平行阵列,能基本满足碳基电子技术实用化和产业化的需求。基于该材料所制造的碳纳米管晶体管能在1V工作电压下具有1.3mA/μm的饱和电流、0.9mS/μm的峰值跨导以及75mV/dec的SS(液栅高效调控),环振电路速度可达8.06GHz,首次在同尺寸器件实测性能和电路速度上超过硅基技术[34],可以说是碳基电子技术发展的一块重要里程碑。

最后,需要提出的是,理想的半导体性碳纳米管阵列材料还需要对材料洁净度和电学质量进行精细表征和严格控制。在材料制备过程中的各种化学污染和金属离子残留会严重影响器件和电路的电学性能及可靠性,分散提纯过程中大功率超声对碳管的晶格损伤也会造成电学性能的下降。因此,碳基电子技术的实用化和产业化除了进一步优化材料制备工艺,还需要制定标准化的材料表征流程、开发高效的材料表征平台。

3.2 碳纳米管晶体管金半接触的基本原理、接触电阻和可靠性问题

对于碳纳米管晶体管,其载流子的本征速度优势转化为器件的实际性能优势的首要挑战,就是要形成电阻尽可能小的金属-半导体欧姆接触。因此本节将讨论碳纳米管晶体管如何形成良好的金半接触、不同接触构型的接触电阻随电极尺寸的缩放规律、金半接触的稳定性问题以及阵列碳纳米管金半接触的工艺挑战。

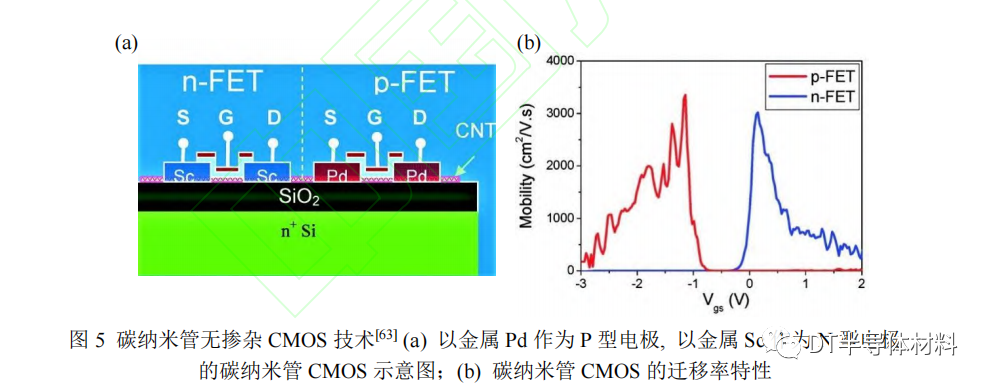

无论是硅锗还是半导体性碳纳米管,当它们与金属接触时,根据加工工艺和金属类型不同,会造成不同程度的晶格周期性破坏或电子波函数的交叠和扰动,从而在半导体带隙中引入与金属波函数共振的电子态,也被称作metal-inducedgap-states(MIGS)。MIGS的密度随着远离金半接触界面而指数降低,因此主要在界面处引入一层电偶极子,从而改变界面处费米能级的位置,形成一个受金属费米能级影响较小的肖特基势垒,其势垒高度由MIGS和半导体费米能级决定。在体材料半导体中,由于接触面的二维特性和相对较大的接触面积,该势垒可达微米尺度[61],因此难以形成穿透性接触、接触电阻较大。为了提高器件性能,体型半导体多采用源漏重掺杂的方式来降低接触势垒和电阻。然而对于碳纳米管器件,由于碳纳米管的准一维小体积特性,其与金属电极的接触面积较小,由MIGS引入的肖特基势垒宽度只有几个纳米,且随着远离界面而迅速衰减,因此其作用范围和作用强度都非常小[61]。在这种情况下,碳纳米管和金属电极之间的接触势垒主要由两者的费米能级差决定,并不存在传统半导体金半接触的费米钉扎现象[32],我们可以用特定功函数的金属来实现与碳纳米管的欧姆接触。此外,不同金属与碳纳米管的浸润性和相互作用强度不同,浸润性较差时接触界面存在间隙会引入额外的接触势垒,相互作用过强时金属会改变碳纳米管的能带结构从而影响接触区到沟道区的载流子注入效率[62]。综上,我们需要费米能级高于(低于)碳纳米管导带(价带)、与碳纳米管浸润性良好且相互作用适中的金属来分别实现N型和P型的欧姆接触。经过长时间的探索,北京大学团队发展出了一套系统的碳纳米管CMOS技术(图5),分别用金属Pd实现P型欧姆接触、用金属Sc或Y形成N型欧姆接触,P型和N型器件的电学特性对称,空穴与电子的迁移率均可超过3000cm2/V·s,开态电导更是达到了0.6G0,接近碳纳米管金半接触的量子电导极限[11,63-65]。这种碳纳米管CMOS技术完全舍弃了掺杂的概念,不需要多步离子注入和离子激活以及相关的光刻和成膜工艺,大大简化了器件制造工艺流程[63],此外还避免了掺杂原子引入的杂质散射和涨落效应。

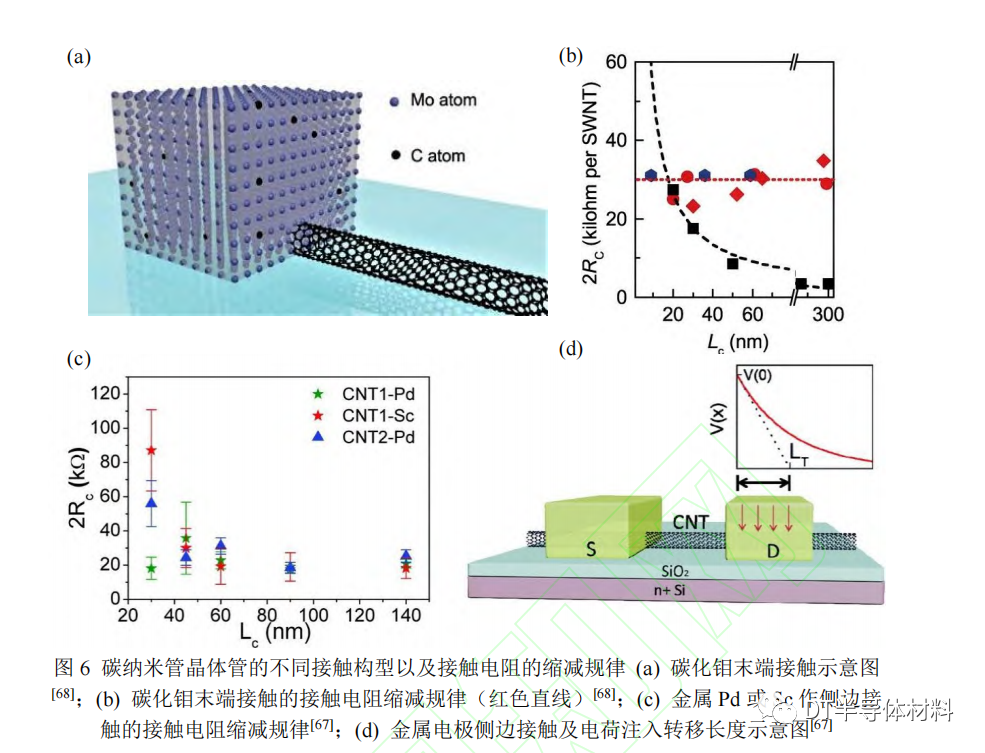

随着集成电路不断发展,晶体管尺寸越来越小,在尺寸缩减时,沟道长度的降低使沟道电阻下降,但接触电极的长度缩减却使接触电阻上升,对于准弹道输运的晶体管而言接触电阻几乎占据了全部的器件串联电阻。因此先进节点不仅要求沟道材料的迁移率尽可能高,还要求接触电阻在给定电极尺寸下尽可能小。国际半导体技术路线图IRDS就明确指出:2030年后的数字逻辑晶体管接触关键尺寸(Contact CD)应缩减至10nm、接触电阻应小于221Ω[66]。对于碳纳米管晶体管来说,其接触电阻主要包括两部分:量子电导决定的基本接触电阻和加工工艺决定的非穿透性接触电阻。对于一个弹道输运的介观一维导体和内部无散射的宏观金属电极所组成的理想体系而言,电流在其界面处会经历一个从多传输模式到少传输模式的转变,从而引入一个由沟道模式数决定的基本接触电阻12.9kΩ/Nch。对于单壁碳纳米管而言,其低能量简并次级能带的沟道模式数Nch为2,因此其基本接触电阻约为6.45kΩ。在实际的碳纳米管器件中,由于加工工艺的不完善,往往形成的是非穿透性接触,从而引入了额外的接触电阻,该部分电阻既和载流子从金属电极到沟道的透射率有关,也和接触长度有关。非穿透性接触电阻根据接触构型不同(范德华接触或共价键接触),随接触长度的变化规律也不相同,因此受接触电极缩减的影响不同。就实验中接触长度较长的侧边接触(sidecontact)而言,其总的接触电阻一般在10~15kΩ[11,63-65]。因此为了满足先进节点的要求,我们需要在器件沟道中平行放置多根碳管,使其并联降低单位长度的接触电阻。根据以上分析,在不考虑电极尺寸缩减的情况下,至少需要密度为40~70根/um的阵列碳纳米管作为沟道材料才能满足要求。进一步考虑实际的接触长度缩减情形:由于侧边接触中载流子注入效率会在一个阈值即转变长度LT附近急剧下降,因此当接触长度接近20nm时,碳管PMOS的接触电阻会增大至每根碳管60kΩ左右,碳管NMOS的接触电阻由于电极边缘氧化问题会进一步增大到每根碳管90kΩ左右[67]。此时至少需要密度为270~410根/μm的阵列碳纳米管作为沟道材料,如果进一步缩减接触电极长度到10nm左右而不改变工艺,则需要更高密度的阵列碳管才能满足先进节点接触电阻的要求。然而密度超过200根/μm的碳纳米管阵列会逐渐出现碳管间的库伦相互作用和屏蔽效应以及碳管间距的不均匀性,造成整体器件性能的下降[31-33]。因此,我们需要优化接触工艺和接触结构,尽可能降低单根碳管的接触电阻,比如采用末端接触工艺(endcontact)。该工艺在碳管上沉积可形成碳化物的金属如钼或镍,然后对接触部分进行高温退火形成金属碳化物,未被金属覆盖的碳管轴面直接“焊接”在金属碳化物上,从而构建出沟道碳原子和接触电极金属原子间的强共价键连接[68]。这种相互作用较强的接触结构能够在电极长度缩减时始终保持适中的载流子穿透系数,避免了接触电阻随电极长度减小而急剧上升的问题。碳化钼末端接触的单管接触电阻即使在10nm接触长度下仍能维持在36kΩ左右[68],即只需要150根/μm的阵列碳纳米管就可以满足先进节点对接触电阻的要求。然而,这种工艺目前只实现了碳管的P型接触且工艺难度较大。由于低功函数的金属较为活泼,易形成金属氧化物而非金属碳化物,因此是否能够以及如何实现N型末端接触尚未可知。另一方面,也有研究展示侧边接触的接触电阻在接触长度缩减时变化并不明显,且有几率在10nm接触长度下得到仅13kΩ的接触电阻[69]。由此发现,即使接触结构相同,不同的器件也会呈现出较大的接触电阻波动,这说明即使在工艺简单的侧边接触中,接触电阻受哪些因素影响、如何进行优化仍未被完全解释清楚,有待进一步研究。

除了接触电阻问题,金半接触稳定性也是碳纳米管CMOS器件的一大难题,虽然利用不同功函数的金属就可以实现器件极性的控制,但对于NMOS器件,低功函数接触金属如Sc、Y容易在低真空成膜过程中或暴露大气后氧化,从而使器件断路或接触电阻急剧增大。为了获得空气中稳定可靠的碳管N型接触,人们采取了各种办法如化学修饰[70,71]、静电掺杂[72-75]、钝化保护[76]。其中,化学修饰将铝纳米颗粒沉积在沟道或接触部位作为电子掺杂剂,利用电子转移来增强N型输运。但该工艺具有较大的工艺波动、且开态电流相比P型器件明显下降[70,71]。在顶栅结构中,金属离子更是可能成为可动离子电荷造成阈值电压漂移和器件稳定(a)c(b)c(c)c(d)c性的进一步下降。因此,化学修饰工艺并不适合高性能碳纳米管CMOS器件。静电掺杂则是指对碳纳米管界面处的栅介质进行工艺控制,使其带有较多的固定电荷或与基底界面形成电偶极子,从而通过静电力作用改变本征沟道的费米能级,等效实现传统MOS器件中晶格替位式掺杂的效果,最终得到可靠性较强的N型碳纳米管晶体管。如文献[72]在碳管表面沉积薄层金属铝然后热氧化形成非配位的AlOx,文献[73]在碳管表面沉积薄层金属钇然后热氧化形成非配位的Y2Ox,在这类氧化不完全的栅介质层中均存在较多氧空位与带有非配位电子的金属离子,从而提供较多的正固定电荷和电子施主,对被覆盖的碳管沟道产生N型掺杂效应。文献[74]和[75]则利用氧化铪与氧化硅界面氧原子扩散产生的电偶极子来实现类似的静电掺杂效果,还进一步引入了随机固定电荷对接触势垒的调制和改性作用。然而,基于栅介质静电掺杂工艺实现的N型器件在性能上远差于接触金属功函数调制工艺所制造的欧姆接触器件,这种牺牲性能换可靠性的做法并没有真正解决问题,只是将接触稳定性问题转化为了栅结构稳定性问题,更牺牲了碳纳米管晶体管的性能优势。除了化学修饰和静电掺杂,钝化保护是一种更为直接和有效提高N型接触稳定性的方法。通过在接触电极顶部和侧壁覆盖氧化铝钝化层,充分隔绝水氧影响,可在不明显退化器件性能的情况下大幅提高碳纳米管晶体管的可靠性[76]。需要指出,这种钝化保护工艺是在高校实验室有限的工艺水平下完成的,与工业界的高级封装技术相比极其简陋,如果采用工业标准和碳基适配的钝化保护工艺,金半接触稳定性或能大幅提升。

对于碳纳米管的金半接触而言,除了本节上述讨论的问题,还涉及一些二级效应,其中对器件性能影响较大的两种现象是:金属应力或毛细力导致的碳管形变和位移、金属与阵列碳管浸润性的一级相变现象,此处进行简单讨论。首先,在侧边接触中,不同的基底表面性质和不同的成膜工艺会产生不同强度的金属应力,从而导致碳管发生形变和位移。相关理论计算表明,碳管形变会改变其能带结构、减小带隙(10%~30%)并降低能带简并,且在形变碳管和本征碳管的界面处,由于能带不再对齐,接触电阻也会有所增大[77]。碳管位移则有可能形成碳管团簇,从而增大碳管间的库伦屏蔽作用、降低栅控效率。此外,在阵列碳纳米管金半接触中,随着碳管间距变化,金属包裹碳管的形状也有所不同。具体来说,当碳管间距减小到一个临界长度附近时,金属浸润性会迅速下降(类似于一级相变过程),碳管由侧边三面接触变为顶部单面接触[78]。这种金属包覆面积的下降无疑会降低载流子注入效率、增大接触电阻,因此需要尽量避免。碳管间距缩小而引起金属浸润性相变的成因较为复杂,与金属类型、碳管直径、金属与碳管以及金属与基底的相互作用强度都有关,有待进一步系统研究。

总的来说,碳纳米管金半接触从原理上相比传统半导体材料具有无需掺杂这一显著优势,多个研究组展示了高性能的原型器件,下一步研究主要集中在接触电阻的工艺优化、金半接触尤其是N型接触的可靠性提升以及阵列碳纳米管接触形貌研究这三个方面。我们需要基于现有的无掺杂CMOS技术,继续探索同时具有高性能和高可靠性的碳纳米管金半接触工艺。

3.3碳纳米管晶体管栅结构的优化与挑战

衡量一种半导体材料尺寸缩减和低功耗潜力的有效参数是自然长度l(thenaturallength),该参数由场效应晶体管的静电泊松方程求解而来[79],体现了栅极电场和漏极电场对沟道载流子的竞争关系。一般来说自然长度越小说明栅控潜力越好,亚阈值摆幅(SS)和工作电压也就越容易降低。并且晶体管的沟道长度应至少大于六倍的自然长度才能不出现明显的短沟道效应,因此较小的自然长度有利于晶体管的尺寸缩减。对于多栅器件,自然长度可用半经验公式表示,

可以发现,对于同一类型的栅结构和栅介质工艺,半导体介电常数和厚度越小,其自然长度就越小。而碳纳米管作为一种超薄半导体材料,其厚度只有1~2nm,自然长度仅为0.2~1nm[80],天然适合尺寸缩减及低功耗应用。然而,材料的本征优势不代表器件的实际优势,要想兑现碳纳米管的超薄体潜力,就必须发展出一套适配的栅结构工艺方案。从碳纳米管的材料属性出发,可以得到对栅介质的一些基本要求:首先,碳纳米管的超薄体特性使其更容易受到表面电荷的干扰(噪声与散射)[81],从而对栅介质电荷陷阱或随机固定电荷更加敏感,因此碳管器件需要更加“纯净”(栅氧电荷密度较低)的栅介质。其次,碳纳米管表面是一层sp2杂化的碳原子,没有硅锗等材料的界面悬挂键,这种完美的晶格结构虽然带来了诸多上文提及的材料优势,但也使碳管无法提供栅介质原子层沉积(ALD)生长所需要的成核中心,从而间接导致界面层栅介质质量较低或整体栅介质厚度增大,因此碳管器件需要一种适用于惰性表面的栅介质生长工艺。

经过以上分析可发现,碳纳米管CMOS器件的第二个核心问题就是如何设计和制造高效且稳定的MOS栅结构。碳纳米管器件栅结构的设计和制作,重点在于栅介质的几何结构或静电学设计、栅介质的材料选择及生长方法、栅介质陷阱电荷与界面态的控制和优化,以及栅金属的阈值电压调控这四个方面。本节将从以上四个方面展开,回顾各方向的关键工作,简要论证各种技术的优势与不足,总结关键的科学问题和技术挑战。

3.3.1栅结构的静电学设计

碳纳米管CMOS器件的栅极几何结构是影响器件静电学栅极控制效率(即静电栅控,效率越高则SS一般越低)的主要因素之一[6],也极大影响着后续栅介质的材料选择、生长工艺以及界面质量。主要的栅极几何结构有四种:背栅(Backgate,BG)、顶栅(Topgate,TG)、双栅(Doublegate,DG)和环栅(Gate-All-Around,GAA)。其中,底栅结构在碳管器件发展早期较为常见,制作底栅不需要在碳管表面上直接生长ALD,因此工艺难度较低,但静电栅控效率也较低[82]。并且底栅器件通常具有较大的SS和回滞,必须配合钝化工艺来减少碳管表面吸附的水氧等杂质[83]。顶栅结构则多被用于高性能碳管器件的制造[6,19,84],理论上具有较高的栅电容和栅控能力。但由于缺少能在碳管惰性表面上生长高质量栅介质的有效方法,顶栅器件大多是通过ALD工艺过量生长栅介质从而覆盖碳管[84]或利用各种分子修饰碳管表面从而辅助ALD生长[19]而制造的。这不可避免地增大了栅介质厚度或引入了低k介质层,从而降低了实际栅电容和栅控能力。双栅结构可看作背栅和顶栅的结合,理论栅电容和栅控效率进一步增大的同时,同样存在顶栅介质生长工艺的问题。而环栅结构则是工艺难度最大、栅效率最高的理想结构,其难点不仅在于如何在碳管表面共形生长均匀的栅介质,还对碳管排列的方向性提出很高要求,目前仅在单管上有所展示[85,86],且文献[85]所用工艺难以降低栅介质厚度和EOT,文献[86]的NO2预处理方法只适用于氧化铝,且由于界面陷阱等因素影响无法得到理想的亚阈值摆幅,综合来看都没有展现环栅结构的潜在优势。因此,目前碳管栅结构的研究还处于顶栅阶段,只有在顶栅工艺上有所突破,才能进一步考虑更复杂的双栅或环栅工艺。

3.3.2栅介质的材料选择和生长工艺

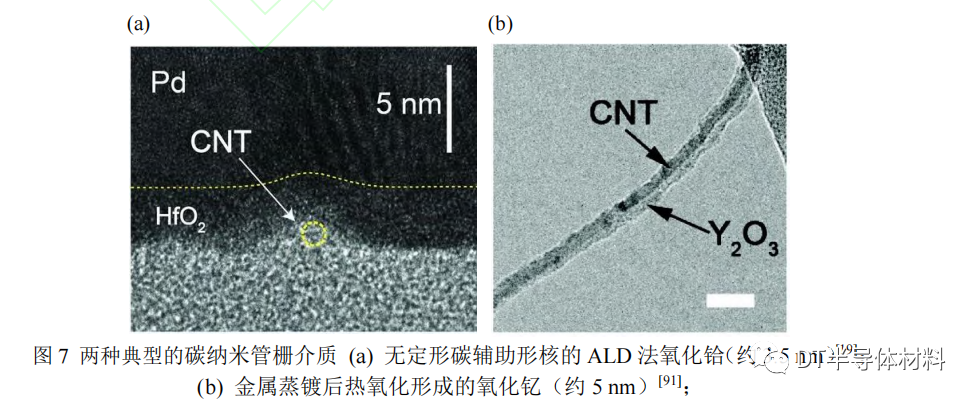

碳纳米管介质层的材料选择和生长方法首先需要考虑其用途,其主要用途有三类:钝化保护、静电掺杂和CMOS栅极介质层。钝化保护在背栅器件和N型器件中较为常见,通过在碳管表面制备一层PMMA或氧化铝等隔离介质,可有效减少空气水氧等杂质吸附,降低器件回滞和低频噪声[83,87],提高金半接触的可靠性[76]。静电掺杂在上一小节已经讨论过,主要用来实现N型碳纳米管器件。基于静电掺杂的N型器件虽然在性能上远差于低功金属接触的N型器件[72-75],但其揭示了氧化物栅介质中固定电荷对载流子输运的作用机理,对碳纳米管器件的设计优化具有一定参考意义。碳纳米管介质材料最主要的用途则是CMOS器件的栅极介质层,需要综合考虑器件的静电栅控、栅极漏电流、抗击穿特性和界面态等关键指标,其材料选择应主要关注材料的介电常数、禁带宽度和缺陷类型及密度,其生长方法应解决碳管sp2杂化的惰性表面难以形核这一难点问题[6,88]。学界尝试过的碳管器件栅介质材料种类较多,其中比较可靠的有:ALD工艺的氧化铪[13,63,89]、氧化锆[84]、氧化镧[90]和金属热氧化工艺的氧化钇[91-93]。其中氧化铪、氧化锆、氧化镧的主要优势为相对介电常数较高,分别可达18、25、27[13,63,84,89,90],但均未解决在碳管惰性表面形核和均匀生长的问题。由于金属钇与碳管的浸润性较好,热氧化后能形成包覆率较高的薄层氧化钇,但氧化钇的相对介电常数理论值仅为16、实际值一般仅为12左右[91-93]。并且考虑到金属成膜过程在亚5nm尺度下岛状生长带来的本征波动性,该工艺可能会在深亚微米尺寸的碳管器件中造成较大的均一性问题。原则上讲,在器件设计中需要权衡不同指标如栅电容和栅极漏电流等,栅介质材料往往难以同时兼顾大介电常数和大带隙等性质,因此选择栅介质材料时应综合考虑生长工艺是否成熟、与沟道材料是否适配等因素而非某单一指标。对于碳管器件而言,考虑到其特殊惰性表面,工业界主流的高k栅介质工艺基本都无法直接使用,因此学界曾尝试过包括DNA修饰、无定型碳种子层、化学基团键合等多种表面修饰方法以提供形核中心[19,88,94],再配合成熟的ALD工艺实现超薄栅介质。但这些表面修饰工艺的问题在于难以控制工艺均一性和可靠性,从而不具备大规模集成电路应用的潜力。化学修饰工艺中各种分子基团与碳管表面键合后还会造成碳管的结构缺陷和晶格畸变,甚至会引入散射中心,从而损害了碳管的高迁移率优势[94]。目前来看,较可行的技术路线是采用超薄中间介质层+ALD高k介质层的栅堆垛结构[6,93,95,96]。在这一结构中,中间介质层应能够在碳管和基底表面均匀生长,并具有尽可能高的k值、带隙和较低的缺陷密度,从而在辅助高k栅介质生长、拓宽其材料选择范围的同时不退化栅电容、漏电流和界面态等关键指标。对于具体的中间介质层材料,有研究利用氧化铝[6]、氧化钇[93]、氧化钛[96]搭配其他高k介质层实现顶栅结构,这些工艺方案均只考虑了以上所述中间介质层要求的某个或某几个方面,如氧化钇具有相对较少的界面缺陷但不具备超薄尺度下的共形生长特性[93],氧化铝具有大带隙和超薄尺度的均匀性潜力但缺陷态密度尚无正面数据[6]。就中间介质层的材料选择而言,目前并没有成熟或具有明显优势的方案,仅能根据一些基本特性来做初步筛选。在中间介质层的生长工艺方面,较容易实现的是PVD法沉积金属薄层再原位氧化的工艺[93,96],但由于PVD法在亚纳米甚至纳米尺度下并不具备较好的膜厚均匀性,这一方法很难实现严格的共形生长。基于ALD工艺的中间介质层则依然面临碳管惰性表面难以与常用前驱体反应的特点,只能针对性地开发特殊工艺,如引入可控的CVD成分来实现中间介质层的均匀成膜[6],但这一工艺目前还不够成熟,既没有明确的显微学证据表明中间介质层具备共形特点和亚纳米尺度的均匀性,也没有电学表征结果讨论其界面态情况。中间介质层工艺依然存在较多挑战,需要开展系统研究以确定适用于碳纳米管器件的具体材料和生长方法。

3.3.3 界面态与随机固定电荷

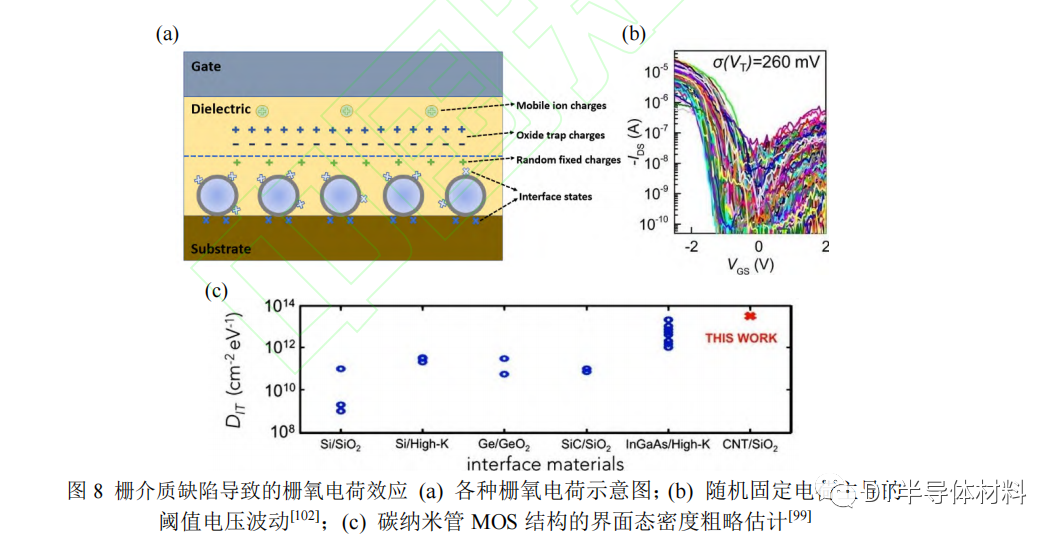

任何一种介质材料都不可避免的存在一些由结构缺陷或杂质造成的电荷陷阱,当这些电荷陷阱与半导体沟道或栅金属之间存在电学交互时,根据其陷阱能级与半导体或栅金属费米能级的相对位置,电荷陷阱会成为动态的陷阱中心或随机分布的固定电荷,也被统称为栅氧电荷。如何评估、减少甚至消除这些栅氧电荷对MOS器件的负面影响,或如何利用栅氧电荷来设计器件,是半导体领域的一大基础和重点问题。对于碳纳米管CMOS器件,较大密度且难以控制的栅氧电荷主要造成以下问题:可动离子电荷与栅氧体陷阱电荷主导的器件回滞、界面态主导的迁移率下降与栅控退化、随机固定电荷主导的阈值电压波动。其中,可动离子电荷与栅氧体陷阱电荷问题是场效应晶体管的共性问题,在硅基和三五族化合物等器件体系中有较多表征和解决方法,本文不加赘述。而碳管器件的界面态问题则与硅基等传统半导体器件有所不同,并具有较大影响。具体来说,在碳纳米管晶体管中无论是采用传统的单层高k栅介质工艺,还是中间介质层加高k栅介质的栅堆垛工艺,都存在界面态密度较高(可达1012~1013/(cm2·eV))、界面处栅介质形貌波动大等问题,从而引入较大的界面态寄生电容和较多的散射位点,使器件的饱和电流和跨导、SS和阈值电压均发生退化或漂移,从而降低了器件性能、均一性和可靠性。在此方面,学界早期研究主要集中于氧化硅背栅界面上水氧吸附的影响:水氧分子在碳管表面既会物理吸附和形成可动离子,也会形成氧化还原对并在碳管带隙中引入缺陷态[97,98];此外水分子与氧化硅的悬挂键还会形成多层Si-OHsilanol基团从而提供慢态电荷陷阱,这些都会造成器件的较大回滞[98]。基于顶栅结构的界面分析则进展寥寥,既缺少可靠且适用于碳管器件的电荷陷阱表征模型,更不用说准确的界面态定量提取结果。有研究者基于时域脉冲测试法和简单的数理模型,粗略提取并对比了顶栅碳管器件的界面态量级,认为在1013/(cm2·eV),比其他MOS界面体系如Si/SiO2、Si/High-k、Ge/GeO2、SiC/SiO2的常见界面态提取数值均高出一到两个量级[99,100](图8)。与体材料半导体MOS结构不同的是,由于碳管表面是sp2杂化的无悬挂键晶格结构,如此高密度的界面态不太可能来源于碳管本身,而更可能来源于碳管制备过程中的有机残留、栅介质的悬挂键以及结构缺陷如氧化铪中的氧空位等“外部”机制。碳管与栅介质通过范德华力非价键结合的特点虽然降低了界面散射、保护了碳管的高迁移率,但也间接导致界面态密度较高,在电应力作用下还会促使缺陷由沟道界面处向栅金属方向增殖,从而导致栅介质退化,因此如何处理栅界面是碳管栅结构制备的关键问题。针对界面态问题,最直接的处理思路是通过组合气体退火等工艺钝化界面处的栅氧陷阱;其次,我们还可以使用某种缺陷态密度较低的中间介质层将碳管与high-k电学隔离开来,以降低栅氧陷阱与碳管的电学交互强度。然而,现有研究几乎都是基于单根碳管或网络状碳管薄膜开展的,其半导体层的本征电容过小或表面势波动较大,难以测量准确可靠的CV数据,因此阻碍了对碳管器件界面态的系统研究。碳管CMOS器件的理想材料是定向排列的高纯高密度碳管阵列,而基于阵列碳管的界面态表征和工艺优化尚无文献报道,其主要困难包括但不限于制备理想的阵列碳管、设计合适的MOS测量结构、建立碳管界面态表征模型以及开发界面质量较好的中间介质层工艺。

随机固定电荷是指在栅氧内部、界面处甚至氧化物基底上的正负电荷,基本不受栅压调控,也不和沟道发生动态电学交互。随机固定电荷在半导体MOS结构中会屏蔽栅电场、使阈值电压漂移,从而造成器件和电路均一性问题,需要尽量降低其密度大小、控制其分布范围。碳纳米管的超薄体特性使其容易被栅极调控的同时,也更容易受到哪怕极少数界面电荷的电学影响[81],因此随机固定电荷对碳管器件的负面影响相比硅基器件更大。具体来说,随机固定电荷在碳纳米管晶体管中的作用机理主要包含两方面:1.对单根碳管器件而言,随机固定电荷会屏蔽栅电场、改变阈值电压,从而导致亚阈值摆幅增大以及器件间的开态电流波动[101](图8);2.对阵列碳管器件而言,随机固定电荷还会造成多根碳管之间的阈值电压波动,处于同一沟道内的多根碳管无法同时开启或关闭从而进一步退化亚阈值摆幅,但开态电流的波动范围由于平均效应会有所减小[102,103]。因此,为了降低器件电学性能的波动,除了要降低随机固定电荷的密度至5×1011cm−2以下(硅MOS常见值),我们还需要使随机固定电荷的分布尽可能均匀,从而减少管间阈值电压波动。可以发现,碳纳米管晶体管的均一性问题不仅要考虑器件间的材料和工艺波动,还需要考虑单个器件内的电学缺陷波动,因此对器件制造工艺提出了更高的要求。

3.3.4栅金属阈值电压调控技术

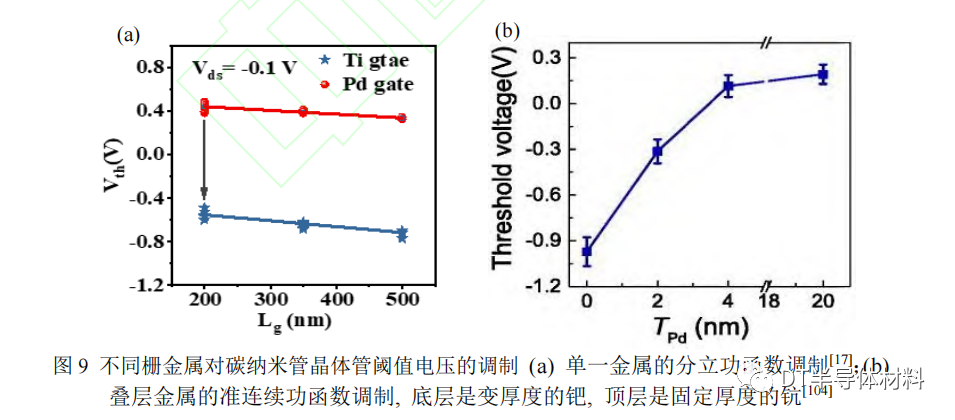

最后,在阈值电压调控方面,由于碳纳米管具有完美的晶格结构,其理想的(a)c(c)c(b)cCMOS技术是无掺杂的,因此也就无法像传统半导体器件一样通过改变沟道掺杂浓度来调控阈值电压,只能通过栅金属功函数调制与栅氧固定电荷调制来获得所需要的阈值电压。然而上文提到,栅氧固定电荷的随机性会导致多根碳纳米管间阈值电压的波动,从而导致亚阈值摆幅的退化,因此在不能精确控制固定电荷分布和密度的情况下,该方法并不适合短沟道碳管器件。与此同时有工作表明,通过使用不同功函数的栅金属如Pd和Ti,可以改变1V左右的阈值电压[17],从而根据需要实现耗尽型或增强型晶体管(图9)。然而,大规模集成电路应用需要对阈值电压进行精确乃至连续调制,有限的栅金属种类只能提供分立化的功函数选择,不能满足实际器件设计的需要。北京大学团队针对性地开发了阈值电压连续可调的栅金属技术,通过两种功函数差异较大的栅金属堆叠如Pd和Sc,精确调整底层金属的厚度就可以实现-1.0~0.2V的阈值电压连续变化范围[104],基本可以满足不同应用场景下的碳纳米管晶体管设计需求(图9)。为了进一步提高栅金属的稳定性和工艺可控性,碳管器件还可以借鉴HKMG工艺,采用硅基兼容的合金栅极实现特定的功函数和阈值电压。

本节深入讨论了碳纳米管晶体管栅极工程所涉及的各个重点和难点问题,针(a)(b)对栅结构的静电设计、栅介质材料生长工艺、界面态问题、随机固定电荷造成的电学波动问题以及阈值电压调控问题总结了碳管器件栅结构的现有进展、技术挑战和下一步研究方向。

3.4 碳纳米管晶体管的双极性抑制和漏电流控制

前文提到,理想的高性能碳纳米管CMOS技术是无掺杂的,利用不同功函数的金属与碳纳米管的导带或价带对齐,从而实现了载流子注入势垒近似为零的肖特基晶体管。然而,肖特基晶体管本身是一种双极性器件,金属源漏电极可以同时提供电子和空穴,在晶体管关态下施加足够大的源漏偏置电压,与器件极性相反的载流子就能隧穿过漏端势垒(碳管器件中该势垒高度约等于带隙、势垒宽度受关态栅电场调制而减小),从而导致随源漏偏置电压增大而增大的泄漏电流以及SS退化,此现象又被称作栅致漏电流(Gate-InducedDrainleakage,GIDL)[105]。此外,由于半导体性碳纳米管的有效质量(0.01~0.1m0)和带隙(0.2~0.9eV)与传统半导体如硅的有效质量(>0.15m0)和带隙(1.12eV)相比较小[106],其载流子更容易发生隧穿效应,GIDL效应更加突出。在实际电路应用中,较大的关态漏电流会造成电路静态功耗(Stand-bypowerconsumption)的急剧上升,根据应用场景不同,业界要求关态漏电流不高于100nA/10nA/1nA每微米,分别对应High/Standard/LowPerformance(HP/SP/LP)应用。因此,如何抑制碳纳米管晶体管的双极性、降低关态泄漏电流,就成为了碳基电子技术的另一重要问题。

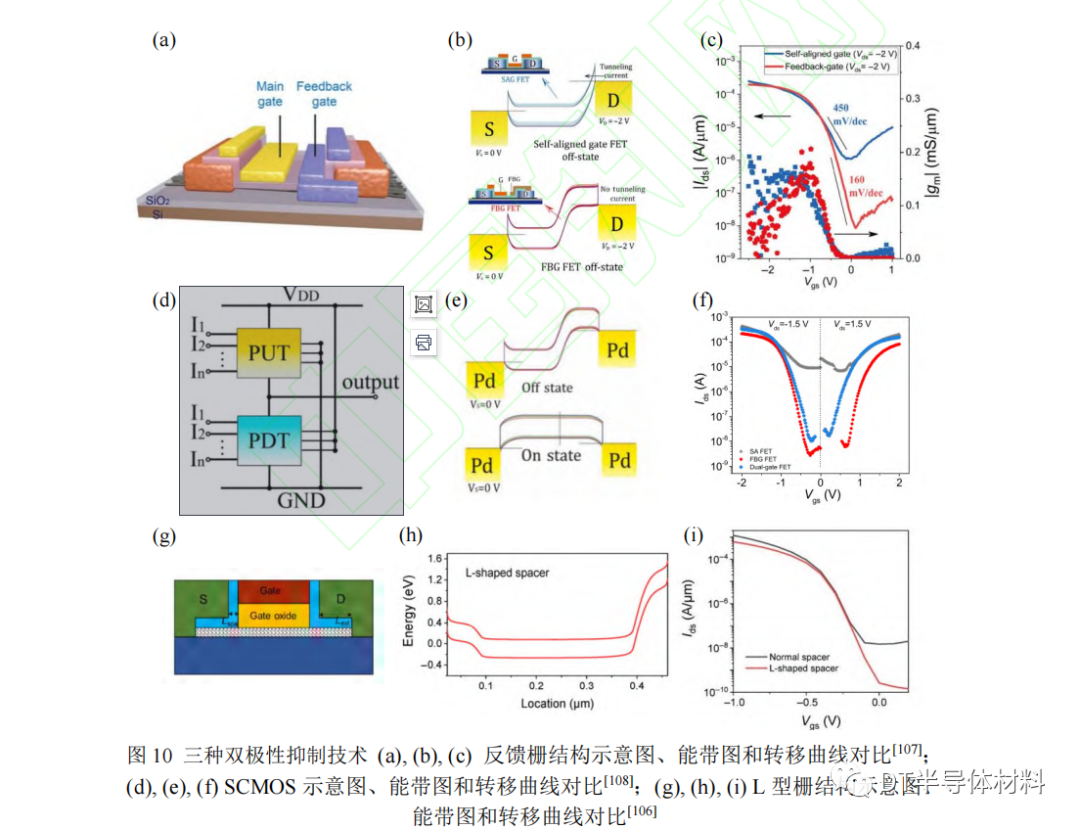

2015年,北京大学团队设计了碳纳米管反馈栅晶体管,通过两个分立的栅极来控制沟道的不同部位,一个是靠近源端、尺寸较大的主控制栅,另一个是尺寸较小、与漏端电极短路的反馈栅(图10)。在关态下,反馈栅由于直接和漏端相连,会增大势垒宽度,从而抑制隧穿电流。在开态下,反馈栅会引入一个高度小于源端注入能级的小势垒,略微降低开态电流。实验结果表明,对于碳管直径为1.5nm、沟道长度为500nm的顶栅器件,使用反馈栅结构可以显著抑制GIDL效应,获得最低0.1pA的关态电流、8个量级的开关比以及75mV/dec的亚阈值摆幅[105],同时不明显影响其开态性能。2019年,北京大学团队进一步在沟道长度小于400nm的深亚微米尺寸器件中验证了反馈栅结构的有效性,统计分析表明:即使受到短沟道效应和源漏电场变强的负面影响,反馈栅结构仍然可以在2V工作电压下维持4个量级的开关比以及小于200mV/dec的亚阈值摆幅、在1.5V工作电压下满足超大规模集成电路SP应用场景的要求[107]。

2020年,北京大学团队采用更符合集成电路设计原则的工艺,提出了一种增强型CMOS(StrengthenedCMOS,SCMOS)逻辑门技术(图10)。在该技术中,晶体管栅极由两个分立栅组成:源端的主栅G1和漏端的控制栅G2。通过将CMOS逻辑门中所有PMOS上拉晶体管的G2连接到地(GND)、将所有NMOS下拉晶体管的G2连接到电源(VDD),使得开态下施加于主栅和控制栅的电压相同、关态下施加于两者的电压相反,因此该技术在显著抑制双极性的同时,几乎不影响器件的开态性能[108]。基于SCMOS结构的多种逻辑门都能够表现出严格的轨对轨输出、降低三个量级的静态功耗以及更快的工作速度[108]。可以说SCMOS逻辑架构是一种适用于任何窄带隙半导体的技术,能同时提供高性能和低功耗表现。

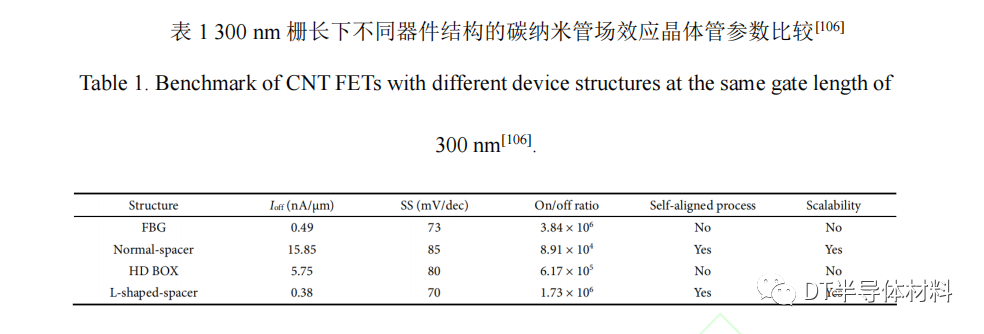

以上基于分立栅的漏端工程虽然能够抑制碳纳米管晶体管的双极性,但不可避免地牺牲了器件尺寸缩减的空间和灵活性,而这在先进节点大规模集成电路应用中是不可接受的。因此,我们需要在尽量不引入额外栅电极的情况下,设计一种更有利于尺寸缩减的漏端结构来抑制双极性。2021年,北京大学团队基于已有实验数据和TCAD仿真,系统研究了器件结构优化对关态漏电流的影响机理,定量分析了栅介质厚度、栅侧墙厚度和介电常数、埋氧层厚度和介电常数等结构参数,最终设计出了具有L型侧墙的碳纳米管晶体管(图10)。该器件结构抑制双极性的机理与前文提到的反馈栅结构类似,都是增强了漏端对碳管能带的静电控制能力。但不同的是,该结构与自对准工艺兼容,更有利于器件的尺寸缩减和大规模集成。仿真结果表明,该结构相比于反馈栅结构在相同栅长下具有更好的关态表现,并且能在最短50nm栅长的器件中保持6nA/μm的关态漏电流、85mV/dec的SS和六个量级的开关比[106]。该工作对器件结构的综合优化不仅使碳管器件的关态性能得以大幅提升,也为其他小带隙半导体的器件设计提供了有效参考。

综上所述, 我们可以发现通过漏端工程和结构优化, 碳纳米管器件的双极性可被有效抑制, 关态漏电流有望降低至业界要求范围(1~100 nA/μm)(表 1) 。当然, 为了尽可能降低器件设计难度和工艺难度, 我们还可以选择相对小直径、大带隙的碳纳米管阵列作为沟道材料来抑制关态漏电流。

3.5 碳纳米管器件的集成工艺挑战

碳纳米管虽然具有较强的材料本征优势, 也有研究者展示了高性能的碳纳米管原型器件, 但这些工作都是在实验室环境中完成的, 某些器件制造工艺并不符合工业标准、不适用于实用化生产, 这不仅仅是实验室设备工艺能力有限的问题,更和碳纳米管材料本身的物理化学性质相关, 存在一些可加工性上的基础问题。例如, 在微纳加工过程中的图形转移工艺方面, 实验室展示的碳纳米管晶体管大多使用剥离( lift-off)工艺, 而剥离工艺仅适用于微米级或亚微米级的图形尺寸, 在深亚微米节点中并不具备大规模可扩展性。虽然有工作针对性地发展了基于湿法刻蚀的碳管薄膜晶体管制造工艺[109], 但湿法刻蚀是一种各向同性工艺,其图形尺寸可控性较差, 同样只能用于大尺寸、中低性能器件的制造。与之相对的是, 小尺寸、高性能的碳纳米管 CMOS 大规模集成必须使用干法刻蚀工艺, 然而干法刻蚀工艺通过物理刻蚀过程来实现高度各向异性和精确的尺寸控制。等离子体的物理轰击有可能对碳纳米管造成晶格损伤, 因此干法刻蚀工艺难以直接应用于碳管器件的制造, 必须合理设计刻蚀停止层、精确控制刻蚀速率, 或者使用业界先进的原子层刻蚀(ALE)工艺。碳纳米管 CMOS 的干法刻蚀工艺所面临的困难其实反映了一种碳纳米管可加工性方面的基础问题:碳纳米管材料是一层不可再生的、纳米级的半导体薄膜,任何一道加工工艺甚至晶圆转移过程都有可能污染或损伤碳纳米管, 且这种污染或损伤有时是不可逆的。无论是超大规模集成电路还是分立器件应用, 都涉及较多的工艺步骤, 因此碳基集成工艺必须引入一个人造牺牲层(如覆盖一层包覆性较好且容易去除的介质材料) , 牺牲层能在易产生污染或损伤的工艺中隔离保护碳纳米管, 从而降低工艺难度、提高器件可靠性和良率。除了以上问题, 碳纳米管器件还存在其他集成工艺挑战, 如碳管与绝缘基底的粘附力不强可能导致薄膜沉积过程中碳管发生位移或 CMP 工艺中的碳管滑动问题等等。在碳基电子技术的实用化和产业化进程中, 我们需要结合碳纳米管的各种物理化学性质来思考集成工艺的适配设计, 这需要研究机构与产业界合作完成。

3.6 碳纳米管晶体管的尺寸缩减与性能提升

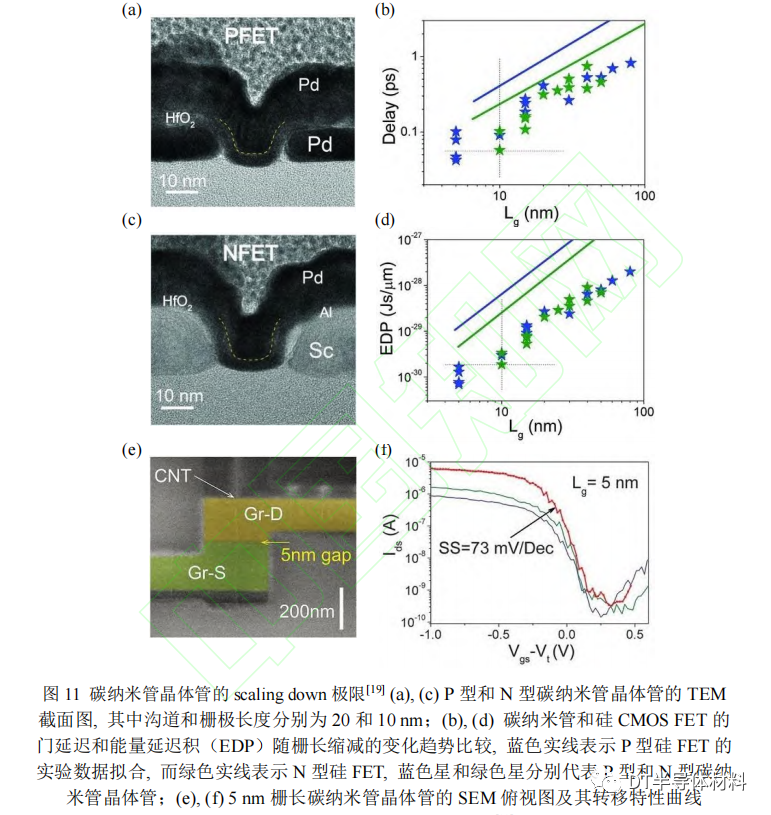

上文提到碳纳米管具有较强的电子学本征材料优势, 包括载流子速度快、超薄体栅控效率高等, 与此同时也存在较多问题与挑战, 如 N 型接触质量较低、栅介质生长难度大等。那么碳纳米管晶体管究竟能否表现出超越传统半导体材料的潜力、并成为延续摩尔定律的有力候选者, 就成了学界和业界十分关注的问题。因此, 为了实验证明碳纳米管晶体管的性能优势和尺寸缩减潜力, 研究者们做了大量努力, 得到了较为突出的结果, 本节将进行简要回顾与讨论。2004 年, 斯坦福大学戴宏杰等人制造的 P 型碳纳米管晶体管就已经在 50 nm栅长下得到了 25 μA 的饱和电流、 30 μS 的峰值跨导、 110 mV/dec 的亚阈值摆幅以及室温下 0.5G0 的开态电导[12], 基本实现了单管器件开态电流的理论极限。而N 型器件则在很长一段时间内无法得到与 P 型器件性能匹配的结果, 直到 2007年北京大学团队以 Sc 作为接触金属实现了无势垒的 N 型欧姆接触[11], 并于 2008年制造出了在 120 nm 栅长下饱和电流为 25 μA、 峰值跨导为 25 μS、 亚阈值摆幅为 100 mV/dec 以及室温下开态电导高达 0.32G0 的高性能 N 型器件, 其门延时低至 0.86 ps, 首次展示了碳纳米管晶体管的太赫兹工作速度潜力[13]。2010 年, 时任IBM 沃森实验室研究员的 Franklin 等人进一步缩减 P 型碳管器件的沟道长度, 在15 nm 沟道长度下获得了高达 0.7G0 的开态电导和 40 μS 的峰值跨导[110], 再次刷新了单管器件的性能极限。2012 年, Franklin 等人甚至进一步在亚 10 nm 栅长的 P型碳管器件中实现了 94 mV/dec 的亚阈值摆幅[82], 展示了碳纳米管晶体管对短沟道效应的惊人抗性以及优异的尺寸微缩潜力。后来, Cao Qing 等人还利用末端接触技术和 ALD 生长的氧化铝栅介质实现了接触长度和沟道长度均为 10 nm 左右、整体尺寸相当于硅基 5 nm 技术节点的单管 P 型器件, 0.5 V 工作电压下的归一化开态电流可达 700~900 μA/μm、 亚阈值摆幅约 85 mV/dec、 关态漏电流仅为 4 nA,整体性能优势达到硅基先进工艺节点的两倍、同时能耗仅为一半左右[5]。2017 年, 经过长期的探索和努力, 北京大学团队终于展示了碳纳米管单管器件的性能极限和尺寸微缩极限[19] (图 11):在 10 nm 栅长和 0.4 V 工作电压下,P 型器件开态电流为 17.5 μA、N 型器件开态电流为 20 μA(开态电导均超过 0.5 G0,N 型跨导更是高达 55 μS) , 归一化性能表现超过了同尺寸硅基器件;在 5 nm 栅长下, 以石墨烯作为接触电极的 P 型碳管器件仍能表现出良好的栅控能力(亚阈值摆幅低至 73 mV/dec) , 其本征门延时(43 fs)相对于硅基 10 nm 技术节点降低了两倍以上且接近二进制开关的理论极限(40 fs) , 其能量延迟积相比于硅基同尺寸器件降低了约一个量级。该工作充分证明了碳纳米管晶体管在高性能、低功耗以及尺寸微缩方面的巨大优势, 以及超越硅基半导体技术的巨大潜力, 是碳基电子技术发展历程中的重要里程碑。

4碳基电子技术的应用与发展方向

碳基电子技术经过长期发展, 不仅在材料制备和基础性器件物理方面取得了系统且深入的成果, 还在多个领域中表现出了巨大的应用潜力, 包括数字计算、射频电子、传感探测、三维集成电路和特种芯片, 以及显示驱动、光电器件等方向, 接下来本文将讨论碳基电子技术在几个重要方向上的进展、挑战与发展方向。

4.1 碳基数字集成电路

碳纳米管具有各种优异的电学性质, 包括前文提到的载流子迁移率/注入速度大、超薄体自然长度小等等, 其低维特性还能帮助实现无掺杂 CMOS 技术, 大幅简化了 CMOS 制造工艺。这些材料和工艺优势使碳纳米管晶体管在开态性能、栅控效率和功耗以及微缩能力等方面都有望满足数字集成电路未来先进节点的要求。碳纳米管数字集成电路(下文简称碳基数字电路)作为碳基电子技术的技术价值和商业价值最大的一个应用方向, 其近年发展主要包括四个方面:高性能电路探索、低功耗器件创新、完备的数字逻辑功能演示和大规模的集成系统研究。

在碳基数字电路的早期研究中, 电路的工作频率都比较低, 仅为kHz量级[111],这主要是受到材料不理想、器件结构优化程度较低以及测量系统寄生较大等因素限制, 并不能展现碳纳米管在数字计算方面的高性能潜力, 因此实现碳基高速数字电路就成了一大挑战。为了便于对比, 晶体管的单级门延时和环振电路的振荡频率常被用来衡量新材料新器件在数字电路工作速度方面的潜力大小。因此, 众多研究者就碳纳米管环振电路速度开展了不懈探索:2006 年, IBM 的 Z. H. Chen等人在单管上构建了 CMOS 五级环振, 获得了 52 MHz 的最高振荡频率, 换算为单级门延时仅 1.9 ns[112]。2017 年, 北京大学杨英君等人在碳管薄膜上构建了基于双极性器件的五级环振, 获得了 17.4 MHz 的振荡频率和 5.6 ns 的单级门延时[113]。2017 年, IBM 的 S.-J. Han 等人在阵列碳纳米管上构建了栅长为 100 nm 的 CMOS五级环振, 获得了 282 MHz 的最高振荡频率以及 355 ps 的单级门延时[114], 大幅刷新了碳基数字电路工作速度的记录, 然而距离硅基同尺寸电路依然存在较大差距。因此在 2018 年, 北京大学仲东来等人通过深入的器件结构优化和工艺优化,基于网络状碳纳米管薄膜和 115 nm 栅长的 Air-gap PMOS 实现了振荡频率高达5.54 GHz 的五级环振, 单级门延时只有 18 ps, 是届时低维材料电路中的最优值,也接近了同尺寸硅基器件的性能水平[52]。2020 年, 基于前文提到的 DLSA 法自组装碳纳米管阵列材料, 北京大学刘力俊等人在 165 nm 栅长的 PMOS 五级环振电路中得到了 8.06 GHz 的最高振荡频率, 单级门延时仅为 12.4 ps, 不仅以更低的工作电压再次刷新了低维材料电路的最快速度, 还首次超过了同尺寸硅基商用器件,充分证明了碳纳米管在高性能数字电路应用上的潜力[34]。然而, 基于理想碳纳米管阵列材料的电路速度上限并不止于此, 2021 年北京大学林艳霞等人通过器件结构工艺的进一步优化实现了增强型晶体管和多级环振电路, 得到了 11.3 ps 的单级门延时[17]。可以期待的是, 随着碳纳米管材料和器件工艺的进步, 其在数字计算电路方面的高速高性能潜力还将进一步被挖掘证明。

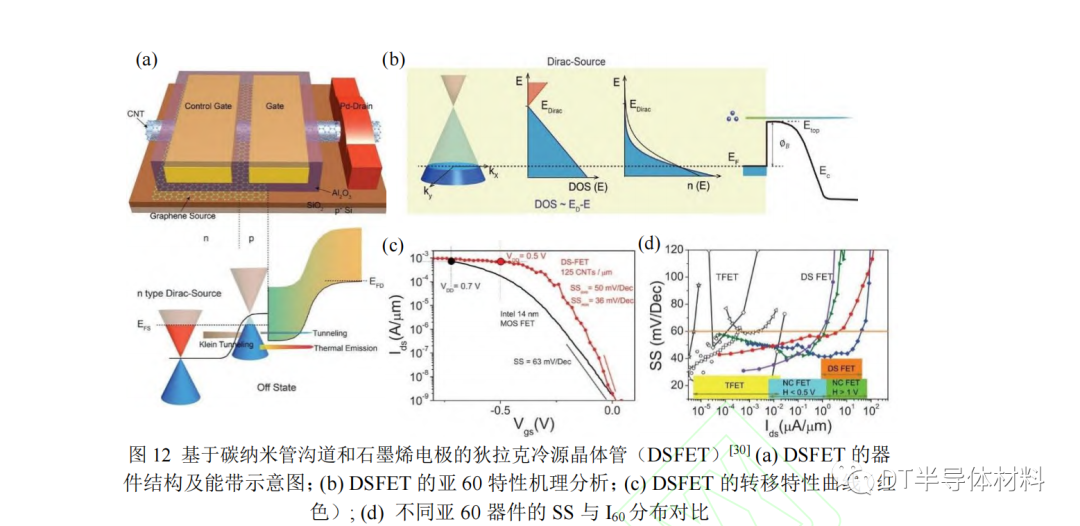

相比于性能方面的要求, 业界还越来越重视数字集成电路的功耗问题, 这是因为随着晶体管尺寸依循 Dennard 定律进行持续微缩, 晶体管的工作电压下降空间越来越小, 基本无法低于 0.6 V, 因此动态功耗无法进一步降低[115]。并且在工作电压缩减时, 阈值电压的调控范围也变得更加有限:不降低阈值电压会牺牲晶体管开态电流, 降低阈值电压则会增大关态漏电流从而增大静态功耗。这些问题的根本原因在于, 经典 MOSFET 的器件结构和输运机理决定了其亚阈值摆幅存在一个极限值, 即由载流子分布热带尾造成的玻尔兹曼极限:室温下器件亚阈值区每关闭或开启一个量级的电流至少需要约 60 mV。因此, 为了解决数字电路集成度增加时急剧上升的功耗问题, 我们必须设计出能打破玻尔兹曼极限的亚 60超低功耗晶体管。然而, 两种主流的亚 60 器件:隧穿晶体管和负电容晶体管都存在本征缺陷, 前者开态电流小且工艺复杂, 后者工作机理尚存在争议且无法展示严谨的器件结果[116, 117]。因此, 北京大学团队在 2018 年提出了一种全新的亚 60器件:狄拉克冷源晶体管(Dirac Source FET or Cold Source FET, DSFET or CSFET)[30] (图 12) 。DSFET 在不改变沟道输运机理的情况下, 通过源端工程将传统晶体管接触电极态密度随费米能级上升而增大的分布特性逆转, 从而在不改变载流子分布函数的情况下降低热带尾的影响。要想实现这一点, 我们需要使用态密度在栅压开启过程中随费米能级上升而下降的材料作为源端电极, 即“冷”源材料。DSFET 使用 N 型掺杂石墨烯与本征石墨烯形成的同质结作为 P 型器件的源端接触, 利用两段石墨烯的能带对齐实现上述态密度分布翻转, 利用石墨烯同质结内部穿透系数接近 1 的克莱恩隧穿以及石墨烯与碳管间势垒较小的穿透性接触实现载流子的高效注入, 从而突破了玻尔兹曼极限, 得到了室温下平均值为 40mV/dec 的亚阈值摆幅, 且优异的亚 60 特性能跨越四个电流量级[30]。此外, DSFET还能在工作电压降低近 30%的情况下(0.7 V 降低至 0.5 V) , 提供与硅基 14 nm节点相似的归一化开态电流, 动态功耗却仅为其 1/3[30]。基于类似的原理, N 型DSFET 也可以被制造出来, 其最低亚阈值摆幅为 37 mV/dec, 证明了冷源晶体管物理机制的正确性以及用其构建超低功耗 CMOS 的可能性[118]。因此, DSFET 是一种同时具备高性能和超低功耗潜力的新型亚 60 器件, 受到了学界和业界的高度重视, 未来或许能以此发展出碳基超低功耗 CMOS 集成电路 。

经过对碳纳米管晶体管基本结构和工作原理的先期探索后, 人们得以制造出回滞较小、驱动电流较大的顶栅器件, 从而开启了碳基数字电路的系统性研究,其研究内容除了以上提到的电路速度和低功耗器件外, 还包括另外两方面:逻辑功能演示和大规模集成系统。

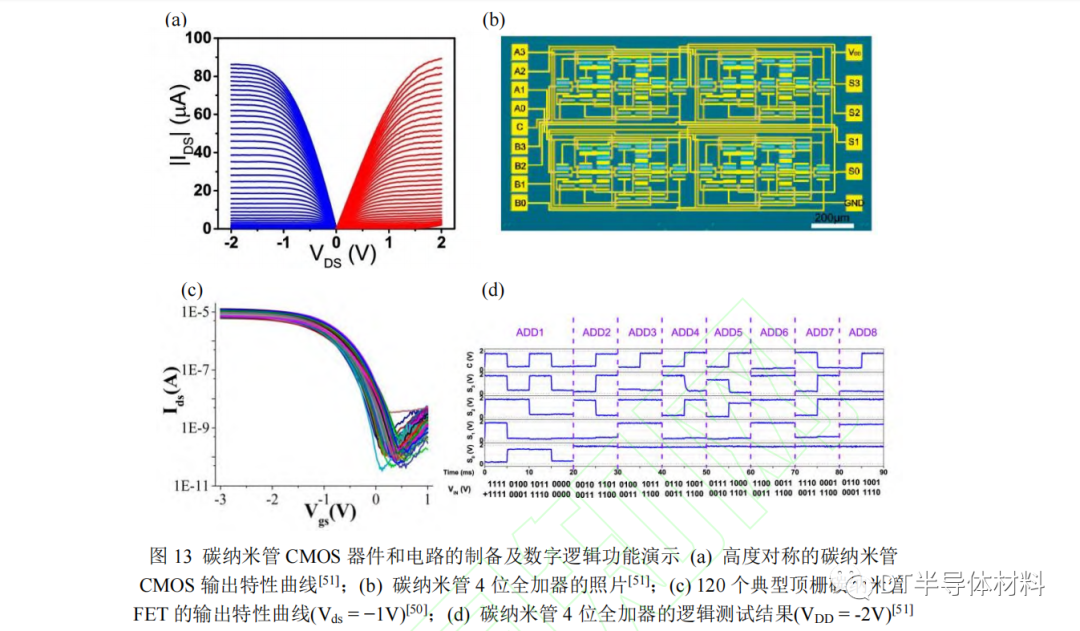

在提高数字电路集成度之前, 首先需要证明碳基数字电路的可行性, 即验证其逻辑功能的完备性和正确性。研究人员进行了积极尝试, 但基于单根碳管制造的早期碳基数字电路存在明显的不足, 如产率较低、逻辑输出电平损失较多、功能过于简单且性能不高等等[112, 119, 120], 这主要是由于材料和器件工艺不够完善。因此, 北京大学陈冰炎和杨英君等人采用更加成熟的网络状高纯碳纳米管薄膜和无掺杂自对准 CMOS 技术, 在 2016 到 2017 年分别基于 PMOS 和 CMOS 实现了良率 100%的非门(反相器)、与门、或非门等基础逻辑门单元, 以及移位器、 D触发器、 T 型锁存器等复杂时序逻辑单元, 甚至 83 阶环振电路、 2 位乘法器和 4位全加器等高性能中规模数字集成电路, 并且都实现了轨对轨的正确逻辑输出,(a) (b)(c) (d)基本证明了碳基数字逻辑集成电路的原理可行性[50, 51] (图 13) 。

在碳基数字电路的集成度和系统架构方面, MIT 的 Max Shulaker 等人做出了一系列成果。2013 年, 他们展示了首台碳纳米管计算机原型系统, 用 178 个碳纳米管晶体管构建核心计算单元, 以 1 kHz 主频在一个数据比特上运行单条指令,其电路性能和系统完整度都比较低[121]。于是, 该团队在碳纳米管器件结构、电路设计和加工工艺方面进行了长期努力, 提出了选择性去除缺陷碳管的 RINSE 技术、静电掺杂与金属界面工程实现 CMOS 的 MIXED 技术、冗余电路设计以克服金属性碳管的 DREAM 技术, 最终于 2019 年发布了全球首款碳纳米管 16 位通用型微处理器 RV16X-NANO[122]。该处理器具有超过 14000 个碳管 CMOS, 运行 32位 RISC-V 标准指令集, 可以执行指令获取、解码、寄存、计算以及数据存储等(c)(b)(d)(a)操作, 其在碳基数字集成电路领域的历史意义可以对标英特尔公司于 1985 年推出的硅基 80386 处理器芯片[122]。但是, 该芯片的晶体管数目仅为 57600 个、工作频率仅为 10 kHz、数据总线仅为 16 位, 与英特尔 80386 芯片的 27.5 万个晶体管、12.5 Mhz 的时钟频率、 32 位总线 4 GB 寻址内存相比, 在电路集成度和性能上都存在明显差距[122]。其集成度与性能差距的根本原因不在于加工平台限制或缺乏其他工业支持, 而在于其碳纳米管材料纯度及排列方式(网络状低纯度碳管薄膜)都不够理想、其器件结构(底栅结构)和工艺(掺杂式 CMOS)都性能较差。综合来看, 该工作虽然展示了碳管 CMOS 在系统集成方面的潜力, 但由于其材料、器件和电路性能的低下, 暂时还不具备产业化意义。

前文提到, 北京大学团队已经制备出了半导体性纯度满足大规模集成电路应用(> 99.9999%)、 排列方向性较好且密度可控(100 ~ 200 根/μm) 的晶圆级碳纳米管阵列材料[34], 这一工作为碳基数字电路的发展提供了坚实的材料基础, 也基本解决了其最大的挑战。因此, 碳基数字电路的下一步发展需要重点解决前文提到的其他碳基电子技术基础性问题与挑战, 继续优化材料质量、完善加工工艺、优化器件性能, 最终实现高速或低功耗碳纳米管 CMOS 的超大规模系统集成。

4.2 碳基射频电子学

未来第六代通信技术要求射频器件和电路的数据吞吐量、传输速度和集成度具有全方位、大幅度的提升, 并实现射频/数字单片混合集成芯片。在主流的射频电子技术中, 硅基 CMOS 晶体管虽然具有集成度优势, 但高频下噪声较大, 难以满足射频电路的需要, 化合物半导体射频器件性能较好, 但其工艺复杂且集成度较低, 两者都难以满足射频电子领域未来的商业需求。因此, 我们需要开发基于新原理、新材料、新器件结构的射频电子技术, 从而推动通信技术的进一步发展。

碳纳米管在射频电子学领域有很多优势:在材料方面, 碳纳米管的载流子迁移率和饱和速度较高、本征电容较小, 且热稳定性和导热能力较强, 因此适合用来制造高速射频晶体管, 其理论速度上限预测可达太赫兹范围[123-125];碳纳米管的准一维结构限制了其态密度和量子电容大小, 因此在晶体管线性区相比传统半导体而言理论上有更好的线性度[126, 127], 十分有利于模拟电路;碳纳米管的能带对称, 因此有利于实现射频 CMOS 电路和双极性射频器件。在工艺方面, 碳纳米管晶体管类似 SOI 架构, 能兼容多种绝缘衬底如石英、金刚石甚至玻璃, 因此在具有较小衬底寄生效应的同时, 还能根据不同射频应用需求来定制化衬底。在系统集成方面, 碳管射频器件与碳管数字 CMOS 集成工艺高度兼容, 有希望实现片上多功能系统(SoC) 。在功率方面, 碳纳米管虽然带隙较小, 看似不适合做射频功率器件, 但其热导率较高(大管径可超过 2000 Wm-1K-1[128]) , 用以评估材料在频率和功率方面综合性能的约翰森因子(JFOM)也高达 14.3×1012 ~ 19.1×1012 Vs-1(至少是硅的 30 倍) [129], 因此功率指标在理论上不会限制碳纳米管射频晶体管的应用。以上优势说明了碳纳米管射频电子学的应用潜力, 本小节将简要回顾碳纳米管射频器件的发展历程、现存问题以及未来发展目标。

为了深入分析碳基射频电子学的发展驱动力和阻碍, 我们可以选取两个核心指标来梳理碳管射频器件的发展脉络:电流增益截止频率 fT 和功率增益截止频率fMAX 。2006 年 Bethoux 等人基于电泳法制备的网络状碳纳米管薄膜制造了本征 fT为 8 GHz 的碳管射频晶体管[130];2007 年 Le Louarn 等人提高了电泳法制备的碳管密度并得到了 30 GHz 的本征 fT [131];2009 年 Nougaret 等人通过进一步提高半导体性纯度到 99%, 成功地把本征 fT 提高到了 80 GHz[132]。2007 年伊利诺伊大学厄巴纳-香槟分校的 John A。Rogers 课题组基于 CVD 法生长的半导体性顺排碳管制造了非本征 fT 为 0.42 GHz 的碳管射频晶体管[36];2009 年他们通过提高碳管密度到 5 根/μm, 将非本征 fT 提高到了 5 GHz[133]。可以发现, 碳纳米管材料的进步促进了早期碳管射频器件性能的快速提升, 无论是本征还是非本征电流截止频率均提高了约一个量级, 因此我们需要高密度高纯度的碳纳米管材料来为器件提供足够的开态电流并降低寄生电阻和寄生电容。2012 年 Steiner 等人采用埋栅结构和电泳法碳纳米管阵列制造出的短沟道射频器件非本征 fT 和 fMAX 分别达到 7 GHz和 15 GHz[134]。从 2012 年开始, 南加州大学的 Chongwu Zhou 课题组利用寄生电容更小、静电栅电容更大的 T 型栅结构来制造碳纳米管射频晶体管, 分别在网络碳管薄膜上得到了 23 GHz 和 10 GHz 的非本征 fT 和 fMAX [135]、在 CVD 法生长的阵列碳管薄膜上得到了 25 GHz 和 9 GHz 的非本征 fT 和 fMAX [136]、在溶液法制备的高纯度乃至手性富集的碳管薄膜上得到了 23 GHz 和 20 GHz 的非本征 fT 和fMAX [137, 138]。2016 年, 该课题组曹宇等人采用 T 型栅结构和 FESA 法制备得到的高纯碳管阵列, 并将沟道长度进一步缩减到了100 nm以下, 从而制造出了非本征fT 和 fMAX 均为 40 GHz、最高本征 fT 和 fMAX 分别为 100 GHz 和 70 GHz 的射频晶体管,是届时性能最高的碳纳米管射频器件[139]。可以发现, 器件的结构优化和尺寸微缩主要促进了碳纳米管射频晶体管实际性能的第二次提升。因此, 同时结合两种驱动力:以溶液法提纯的高密度网络状碳管薄膜为材料基础、以小于 100 nm的非自对准多栅结构为器件基础, 北京大学团队仲东来等人在 2019 年展示了峰值跨导高达 0.38 mS/μm、 最高非本征 fT 和 fMAX 分别为 103 GHz 和 107 GHz、本征 fT 和 fMAX 分别为 281 GHz 和 190 GHz 的高性能碳管射频晶体管[140], 这是届时碳纳米管射频器件的最高水平。在此基础上,周简硕等人还通过进一步优化器件结构、降低栅极寄生, 将实测 fMAX 提升到了 90 GHz, 展示了 K 波段射频放大器的应用潜力, 首次在器件综合性能上比肩三五族射频晶体管, 初步证明了碳基射频电子学的商业化价值[141]。然而, 即使是百GHz的截止频率, 也远低于碳纳米管在速度方面的理论预测上限(THz 范畴) 。从材料角度看, 这主要是因为网络状碳管薄膜的随机取向性导致了沟道内的实际碳管长度随机分布, 从而增大了栅电容、减小了跨导。针对于此, 2019 年 Rutherglen 等人以 FESA 法为基础开发了 ZEBRA技术, 制备了纯度大于 99.9%、 密度为 40-60 根/μm 的阵列碳管并以此制造了射频晶体管;然而, 其最高非本征 fT 和 fMAX 均仅为 106 GHz, 相对于网络碳管薄膜器件并没有显著优势[142]。这主要是因为其阵列碳管制备方法还不够成熟, 碳管的半导体性纯度和密度都不能达到要求。因此, 2021 年北京大学团队石惠文等人从射频电子学对碳管材料的要求(兼容不同衬底、合适密度超顺排、缺陷少、散射位点少、迁移率高)出发, 设计并优化了新的阵列碳管材料制备工艺[20]。该工艺用烷基链较少、氮原子和氢键作用位点较多的 PCO-Bpy 分子作为碳管分散剂, 经两次分散提纯和双液相自组装沉积工艺, 在不同绝缘衬底的四寸晶圆上实现了高纯度(> 99.99%)、管径分布集中(d = 1.51 ± 0.18 nm)、超顺排和高密度(100~120根/μm) 的碳管阵列, 其载流子迁移率最高达 1580 cm2V-1s-1[20]。基于射频专用的阵列碳管材料和器件结构上的寄生优化, 该团队在低损耗的石英绝缘衬底上制造了高性能射频晶体管, 其在 50 nm 栅长下的非本征 fT 和 fMAX 分别达到 186 GHz和 158 GHz, 是所有基于纳米材料的晶体管的最高值[20] (图 14) 。为了验证碳纳米管的频率潜力, 该团队还在高阻硅衬底上制造了开态电流高达 1.9 mA/µm、跨导高达 1.4 mS/µm(Vds = -0.9 V)的射频晶体管, 其 50 nm 栅长器件的本征 fT 和fMAX 分别为 540 GHz 和 306 GHz, 这是碳基射频器件首次进入到太赫兹频段, 证明了碳基射频电子学在第六代通讯技术中的应用潜力[20] (图 14) 。虽然本征截止频率的优异表现只能说明某种材料的速度上限, 并不一定能完全转化为器件的实际性能, 但太赫兹频段的候选材料极其稀少, 碳纳米管的出现无疑具有重要意义。通过进一步的材料优化如提高密度、减少聚合物残留, 和工艺优化如发展碳管中间介质层技术来优化栅界面, 以及器件结构的改进如采用 T 型栅等结构降低寄生效应, 碳纳米管射频晶体管有希望将其实际工作频率提高到 1 THz, 成为继InP HEMT 和 InP HBT 之后的又一种太赫兹射频器件, 并且有可能成为第一种太赫兹 CMOS 射频器件。

除了工作频率的本征优势, 碳纳米管在射频放大器中的应用潜力也逐渐凸显。射频器件最基本的应用就是信号放大, 因此射频放大器的性能表现能直接反映碳基射频电子学的应用潜力。然而, 射频放大器除了频率指标, 还注重放大功率和线性度指标, 在后两者上, 碳管射频器件的早期研究表现较差。具体来说, 在功率方面, 大部分碳管放大器的增益小于 10 dB 或为负值[135, 136], 有效正增益最高的是 2019 年 Marsh 等人在 1.15 GHz 频率下实现的 12 dB[143], 综合来看仍难以满(a) (b) (c)(d) (e) (f)足 5G 通信的要求。在线性度方面, 由于相似信号的高阶谐波尤其是三阶谐波会对基准信号造成很大干扰, 因此我们在接收和处理信号时, 需要保持放大过程的线性度以防止信号失真。有两个指标常用来衡量线性度:1 dB 增益压缩点和三阶交调点, 两者值越大对应的线性范围就越大, 放大器抗干扰能力就越强。然而,长期以来碳管放大器在这两个指标上也表现平平[135, 136, 143], 无法展现其小量子电容带来的本征线性度潜力。2021 年, 北京大学团队石惠文和周简硕等人采用多指栅结构提升碳管器件的负载驱动能力, 基于高纯度网络状碳管薄膜在 18 GHz(K 波段)下获得了 11 dB 的功率放大增益以及 15 dBm 的三阶交调点[141];基于高纯高密度阵列碳管在18 GHz下更是能实现高达23.2 dB的功率放大增益以及大于 9 dBm 的 1 dB 压缩点输出功率和 31.2 dBm 的三阶交调特性(对应的 OIP3/Pdc为 19.7 dB) [20] (图 14) , 各项关键指标均远高于之前美国南加州大学报道的届时最好的碳基放大器, 甚至与某些商业产品(如 HMC6981)相比也具有一定优势,且成本大幅降低。

此外, 在射频集成系统方面, 也有工作展示了基于碳纳米管晶体管的射频/数字混合电路:2019 年, 北京大学团队刘力俊等人以高性能碳纳米管 CMOS 器件为基础, 将 VCO 温度传感器、碳基 MOS 电路、锂离子电池和天线集成在一个柔性基底上, 展示了具有传感、信号处理、信号无线传输和电源的完整物联网节点系统, 且具备超高的能量效率和超低的动态功耗, 以及 0.4~1.5 GHz 范围的可调谐频率, 覆盖了 NB IoT 或 GSM 应用场景所需的频带, 展示了碳基数字/模拟混合集成系统在物联网领域的应用潜力[144]。

综合来说, 碳基射频电子学具备完整的理论基础和器件工艺基础, 已经展现了其较强的本征优势和一定的实际优势, 接下来需要重点优化金属-碳纳米管接触界面和栅介质-碳纳米管栅界面, 提高载流子注入效率并减少界面散射, 从而继续提高碳纳米管射频晶体管的综合性能指标, 并在功率放大器、高线性度模拟电路和数字/模拟混合电路等应用中展现优势。

4.3 碳基集成传感平台

碳纳米管场效应晶体管还可以用于制造晶圆级别均一和可靠的传感平台, 实现包括生物传感、气体传感、光探测等复合功能的集成化和小型化, 并展现出优异的灵敏度和精度。本节将主要介绍碳基传感平台的工作原理、性能特点、最新进展以及技术难点。

在本世纪处, 研究人员开始关注基于纳米线或纳米管的 FET 型传感器, 这主要是因为准一维沟道材料相比于体材料具有更高的比表面积, 并且对外界的静电势变化更加敏感, 因此具有超高灵敏度检测的潜力。单壁半导体性碳纳米管具有天然的小尺寸和优良的电学性能, 并且能和众多种类的检测分子如氢气、生物蛋白等发生范德华吸附、共价交联等耦合作用, 因此受到了广泛关注[145, 146]。经过早期探索, 人们归纳出了四种碳纳米管 FET 型传感器的基本工作原理[147]:1.待检测分子被直接或间接吸附于碳管表面, 从而造成电荷转移或静电掺杂, 使沟道能带移动、传感器 I-V 曲线平移。这种静电掺杂机制较为常见, 且能造成明显的沟道电势变化, 因此适用于高灵敏传感;2.待检测分子吸附在金属电极接触上并调节局域功函数, 从而改变肖特基势垒的高度, 由于空穴和电子的势垒高度变化方向相反, 因此传感器 I-V 曲线 P 支和 N 支的电导和电流变化相反。但这种金属功函数调制效应较弱, 需要较大的电极接触面积, 灵敏度较低;3.待检测分子覆盖在沟道表面, 形成一层等效的低 k 介质从而降低串联栅电容和栅控效率, 从而影响 I-V 特性。但实际上低浓度的检测分子不会紧密覆盖大面积沟道, 因此该机制大部分情况下可以忽略;4.待检测分子在碳管表面引入散射位点, 表面散射会降低有效载流子迁移率。但当电导主要由肖特基势垒主导时, 载流子迁移率的略微下降也可以忽略。以上工作原理分析对传感机制设计具有重要意义:待检测分子对碳管FET电学性能的影响可能存在竞争机制, 要想构建超灵敏通用型传感平台,就必须合理设计器件结构以排除干扰。除了传感机制, 我们还需要考虑沟道材料的选择:单根碳管虽然对沟道的静电扰动最敏感, 本征灵敏度最高甚至可响应单分子, 但其显然不适合大规模器件制造;阵列碳管理想情况下能提供更好的电学性能, 但实际制备工艺复杂, 且成本较高, 目前不适合传感器应用;网络状碳管薄膜存在较多碳管-碳管结, 其直接功能化难度较高, 但均一性好、制备工艺简单成熟, 相比之下更适合作为沟道材料。

基于以上对传感机制和沟道材料的分析, 我们可以发现, 目前最合适的器件结构方案为:基于网络状碳管薄膜和接触钝化的浮栅型 FET。这种结构使用超薄栅介质隔离碳管沟道, 然后在栅介质表面进行功能化, 这样既不会对传感机制和灵敏度造成明显的负面影响, 又能解决网络碳管不易于直接功能化的问题, 还能提供较高的电学基线稳定性和长期使用可靠性。基于该结构, 北京大学团队发展出了系统的超灵敏传感平台, 在生物传感、气体传感等应用方向中取得了突出成果, 下面进行简单介绍。

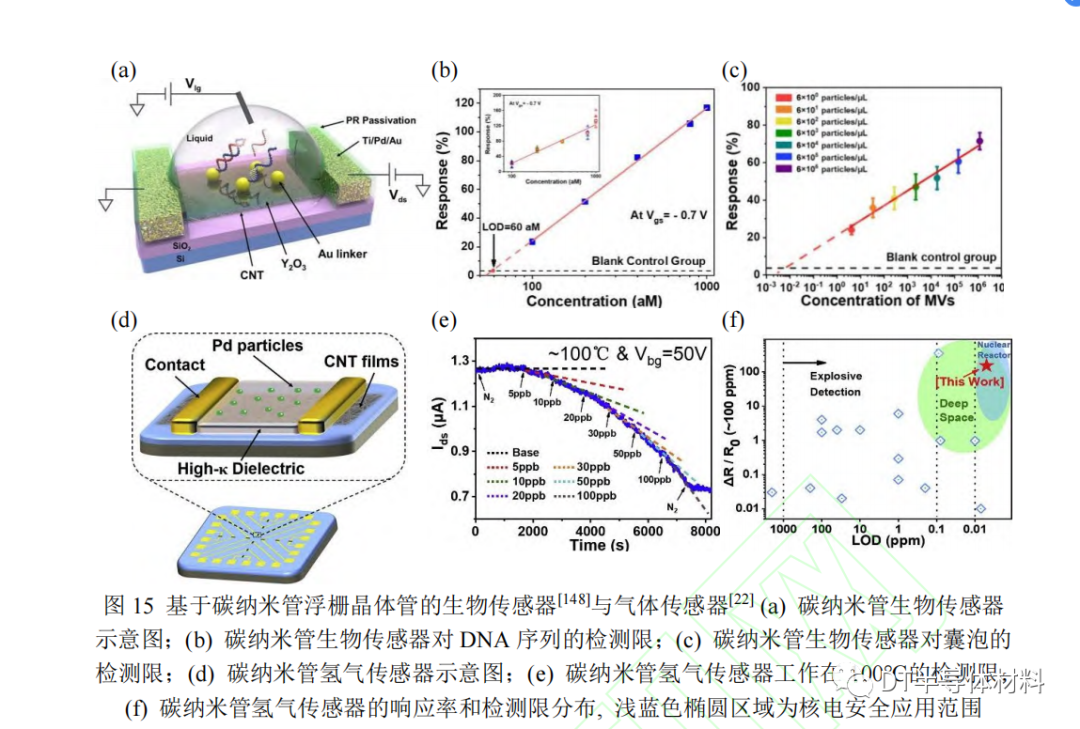

在生物传感方面, 梁玉琪和肖梦梦等人以氧化钇作为浮栅介质层、以光刻胶钝化隔离接触电极、以纳米金颗粒修饰栅介质表面, 并将识别探针分子如互补DNA 链通过巯基化等方式组装在金纳米颗粒上, 制造出了晶圆级碳管 FET 型生物传感器阵列[148] (图 15) 。该传感器去除了生物分子对接触电极的功函数调制效应, 其工作机制完全由沟道静电掺杂效应主导, 因此具有较强的器件可靠性和信号响应强度。此外, 该传感器还优化设计了直流工作偏置点:采用较小的源漏偏置如 0.1 V 使 FET 工作在基准电流较小的线性区, 从而增大响应电流的相对变化量;采用不同大小的栅压偏置使传感器工作在稳定传感模式(大栅压饱和区)或高灵敏传感模式(小偏压亚阈值区) , 且传感响应度与基准器件的阈值电压或亚阈值摆幅有关。经过合理的偏置点选择, 基准器件的均一性可以有效反映到传感响应的均一性上来, 这保证了碳基传感平台的均一性优势。基于以上结构优化和偏置设计, 该传感平台实现了对特定 DNA 序列和微泡(MVs)的定量和选择性检测, 分别获得了 60 aM 和 6 particles/mL 的超低检测限(LOD) [148], 有望取代昂贵耗时且不便携的 PCR 检测技术, 实现无标记的(lable-free)快速生物检测。该工作既刷新了FET型生物传感器的检测限记录, 充分展现了碳基传感平台的灵敏度优势;又实现了对生物信号的多功能检测, 集成了基因筛查与癌症诊断功能,展现了碳基传感平台的功能复合集成化优势。

在气体传感方面, 周绍元和肖梦梦等人同样基于浮栅结构, 以氧化钇或氧化铪作为栅介质, 以对氢气敏感的金属钯纳米颗粒为敏感层修饰栅介质表面, 批量制造了碳管薄膜 FET 型气体传感器, 不仅获得了较快的响应速度(~7 s)和碳基氢气传感器中最高的响应强度[22], 还首次演示了氢气的亚ppm室温检测, 其LOD在室温下低至 90 ppb、 在 100 ℃时低至 5 ppb [149] (图 15) 。该工作的重要应用价值在于:核发电站中钠泵常用以反应堆的冷却和热循环, 而钠泵系统泄漏或失效会产生易燃易爆的氢气从而威胁核电安全, 因此超高速痕量氢气检测是核电安全的关键技术, 碳纳米管 FET 型氢气传感器可探测出亚 ppm 的氢气标志物, 从而能够应对潜在的核电安全威胁。

以上进展充分证明了碳基传感平台在灵敏度、功能集成度、可靠性和均一性等指标上的优势, 以及碳基传感平台在生物检测、核电安全监测等应用场景下的商业潜力。为了进一步提高碳基传感平台的灵敏度、可靠性与通用性, 我们需要着重解决以下问题:1. 浮栅型 FET 结构和碳管材料的静电敏感特性虽然提供了超高灵敏度传感的基础, 但同时也放大了低频噪声。低频噪声是传感器或探测器中的常见噪声类型, 有研究表明碳纳米管的低频噪声本征幅值系数相比于其他半导体材料至少高了 3 个量级[150], 低频噪声的具体大小则与器件的电压偏置、栅界面散射位点密度、接触电阻大小以及导电通道即碳管密度都有关系[151], 因此需要进行器件综合优化和细致的偏置设计来减小低频噪声、增大传感响应。2. 传感应用并不都需要极高的灵敏度, 有的应用场景也对量程或分辨率有所要求, 因此碳(a) (b) (c)(d) (e) (f)管FET型传感器需要合理设计栅介质厚度和直流偏置点, 通过调节浮栅的静电耦合强度、基准电流大小和电流响应放大系数来获得不同量程和精度的传感性能,从而满足多种应用需求;3. 面向产业化和商用化的碳管 FET 型传感器还需要更准确的标定技术和更强的器件可靠性, 这需要我们在传感电学模型、器件结构和加工工艺方面进一步努力, 如建立准确的浮栅电容模型、采用更标准的钝化封装技术等等。

碳基传感平台的未来发展一方面要进一步提高传感灵敏度、器件可靠性和功能多样性, 另一方面要尝试与信号处理电路进行同片集成。理想情况下, 碳基传感平台不仅可用于各种气体分子、生物分子乃至红外近红外光波的超灵敏检测,还能通过在片的数字/模拟混合电路实现传感数据的快速预处理和无线传输, 从而实现功能丰富、高能效的物联网节点系统。

4.4 碳基三维集成电路

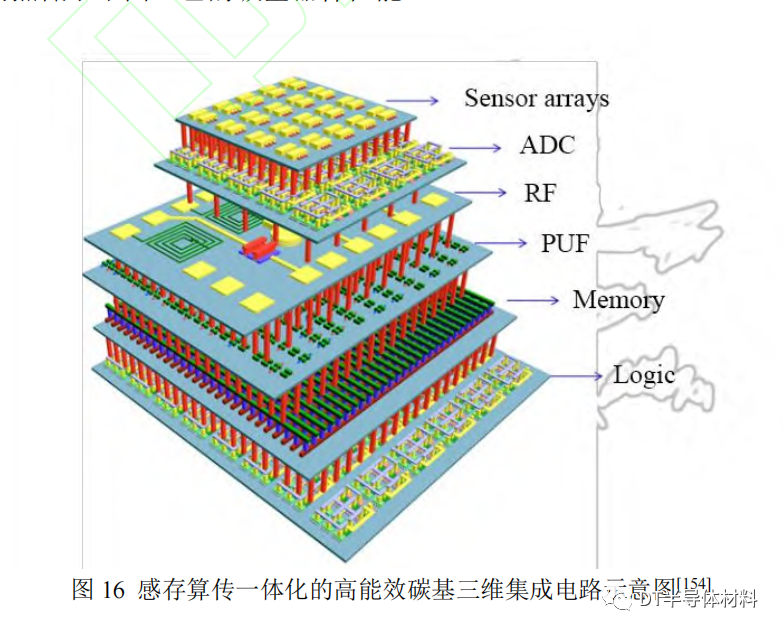

随着集成电路工艺进入亚 10 nm 节点, 仅依靠晶体管尺寸缩减带来的集成度提高越来越有限, 器件间的互连线也越来越复杂, 系统能效的优化空间也越来越小, 传统的系统架构更是难以解决内存墙问题。而三维集成电路为这一困境提供了新的选择:在不提高器件工艺难度的情况下, 通过三维堆叠多层计算电路或存储电路乃至射频传感电路, 来提高芯片的集成度、系统能效和功能多样性。然而,已有的硅基三维集成电路技术主要是利用高级封装技术(3D System-in-Package)和垂直硅通孔技术(Through-Silicon-Via)来将多个独立制造的电路模块简单组合在一起, 其数据通孔密度较低, 尺寸一般在微米级, 因此数据传输的带宽较低,无法发挥出三维集成电路的真正潜力。硅基三维集成技术的根本性困难在于其热预算有限:硅基器件加工温度可高达 500 ~ 1000 摄氏度(如氮化硅侧墙沉积或掺杂离子激活) , 而后道工艺如金属互联的热承受能力有限, 且前道工艺完成后为保证晶体管性能一般不允许后续加工温度长时间超过 500 摄氏度, 因此无法继续制造第二层乃至多层电路[26]。与之相反的是, 碳纳米管 CMOS 电路加工工艺所需温度较低:溶液法制备好的碳管材料向目标基底转移可在室温下完成、无掺杂CMOS 工艺不需要高温退火来激活掺杂原子、 成膜工艺中的最高温度也不超过300 ℃(ALD 生长氧化铪) [11, 63-65]。因此, 原则上讲碳纳米管 CMOS 电路既可以多层堆叠自身得到单片( Monolithic)三维集成电路, 也可以制造在硅基 CMOS电路的上方得到在片异质集成的三维电路。需要注意的是, 工艺热预算较低的优势并不是碳管独有的, 其他半导体技术如低温硅 CMOS 技术、多晶硅器件或金属氧化物半导体器件也能做到低温加工, 但这些方案要么在性能上远差于传统硅基CMOS 和碳纳米管器件(低温硅技术、多晶硅) , 要么不能制造 CMOS 器件(金属氧化物半导体) , 均无法满足三维集成电路的基本性能要求, 甚至可能拖累底层的硅基电路[111]。因此, 综合来看碳基 CMOS 技术是三维集成电路的最佳选择,基于碳纳米管的三维集成电路可以拥有密度更高的纳米级层间数据通孔(Inter-Layer-Via, ILV) , 将数字逻辑计算单元和数据存储单元的距离大幅拉近、降低数据传输耗能和耗时, 将数据传输带宽大幅增加、提高计算速度, 从而显著提高系统综合能效。理论分析和仿真结果表明, 理想的碳管单片三维集成电路相比于硅基平面电路的能效增幅甚至可达 1000 倍[28]。

碳基三维集成电路的实验演示也有一些突出结果, 下面进行简要回顾与分析。2014 年, 斯坦福大学的 Shulaker 等人首次展示了基于碳纳米管的异质三维集成电路, 该电路包括四层结构:底层是硅基数字逻辑电路、中间两层是 RRAM 存储电路、顶层是碳纳米管 CMOS 驱动电路, 其集成度和性能较低, 主要着眼于原理验证和工艺探索[152]。2017 年, Shulaker 等人进一步将 200 万个碳管晶体管、 100 多万个 RAM 存储器集成在硅电路的上方, 以高密度 ILV 作为层间互联, 构建了具备酒精嗅探电子鼻功能的高集成度三维电路, 初步证明了碳基异质三维集成电路的技术可行性[111]。2018 年, Shulaker 等人还展示了完全由碳纳米管 CMOS 器件和RRAM器件构成的碳基单片三维集成系统, 该系统不仅可以准确运行分类识别算法, 和同尺寸的硅基电路相比还具有更高的系统能效(35 倍的能量延迟积改善)和更小的电路面积(三分之一的面积, 相当于 3 倍的集成度提高) [153]。以上工作虽然在加工工艺和电路功能上展示了碳基三维集成电路的潜力, 但也存在碳管器件性能较低、电路速度较慢的问题, 如文献[111]中所用的碳管器件在 3 V 工作电压下的开态电流仅为 20 μA/μm, 远差于其他文献报道的高性能碳纳米管器件, 这显然不满足三维集成电路在电路性能方面的的发展目标。因此, 北京大学团队谢雨农等人针对性地优化了碳基三维集成工艺, 基于高纯度网络状碳管薄膜全程在170 ℃内制造了两层高性能碳管器件[27]。其实验结果表明, 该三维架构工艺相比于平面架构有着更大的布局布线灵活度以及更短的金属互联长度, 因此可获得38%的电路速度提升, 五阶环振电路的振荡频率更是高达 680 MHz, 单级门延时低至 0.15 ns, 这一电学性能是所有已报道的碳基三维电路所用器件的最好结果[27], 但仍然低于平面工艺的碳基器件性能。

尽管有着极高的系统能效潜力, 单片三维集成电路在立体空间中以高密度集成大量器件时会不可避免地遇到更为严重的原子迁移问题和互联散热问题:随着互联线尺寸的精细化和结构的复杂化, 高电流密度下的金属原子会更容易离子化并偏移其位置, 从而导致电路短路或断路;随着单位体积内互联线(层内和层间)密度的大幅提高, 金属互联大量的发热过程和层间介质有限的散热过程还会导致电路整体和局部的温度上升, 从而导致互联乃至器件本身的失效率增加。为了抵抗原子迁移现象, 我们需要原子相互作用力更强、电流负载密度更高的互联材料;为了解决金属互联的散热问题, 我们需要直流和交流信号传导损耗更小的材料。而金属性碳纳米管同时具有相比金属离子键更强的碳碳共价键、较高的电流负载能力(~ 109 A/cm2)以及长程弹道输运性质(微米量级) , 因此可能更适合作为单片三维集成电路的互联材料。为了具体考量金属性碳管能否用作互联材料, 我们首先需要分析其电阻特性。单根金属性碳管的理想电阻仅由接触电阻构成(包含 12.9 kΩ/Nch 的基本接触电阻和同量级的非穿透性电阻, Nch 对于单壁碳管一般为 2、对于多壁碳管则与内外壳层直径有关) , 然而随着互联长度增加, 碳管晶格振动过程的声子散射会额外增加沟道电阻。同时考虑接触和沟道电阻, 任意长度的碳管互联电阻可近似表示为,

在接触质量一定时, 决定互联电阻的参数显然是电子有效平均自由程, 该参数在低温低场下由声学声子散射决定、在高温低场下需引入光学声子散射的修正、在高场下主要由光学声子散射决定, 具体数值则需要更完整精确的模型来评估。以上对单根金属性碳管互联电阻的分析可近似线性地拓展到管束体系, N 根碳管组成的管束总电阻约为 1/N 倍的单管电阻。基于更复杂的电阻模型, Naeemi 和 Meindl 等人系统比较了低偏压下单壁和多壁碳纳米管管束与铜互联导线的电导率, 并得出结论:金属性碳管在较长尺度时具有最大电导率, 适合用作全局和半全局互联;而铜在较短尺度时具有更稳定的高电导率, 适合用作局部互联[155]。除了互联电阻我们还需要考虑互联的 RC 时间延迟特性, 由于碳管的准一维特性, 原则上讲其极小的静电电容和量子电容与铜互联电容相比具有一定优势, 相关文献对碳管 RC 延迟的半定量分析同样支持这一判断[156, 157], 金属碳管互联的准确电容值和高频传输特性则需要使用传输线模型来分析。总的来说,电子输运通道较多、电阻和电容较小的厚多壁碳纳米管管束更适合作为单片三维集成电路的互联材料, 但均匀且密集的碳管阵列或管束并不容易在平面上制备(碳管排列技术可参考本文 3.1 节相关内容) , 因此目前更为可行的方案是将其用作层间通孔材料。2020年, P.-Y. Lu等人通过Fe(C5H5)2气体的反应在 550 ℃的低温下生长出了高质量的金属性碳纳米管, 其电阻率约为 10-6 Ω-m、热导率约为 800Wm-1K-1、杨氏模量高达 1000 Gpa、通孔深宽比大于 25 , 将其用作三维集成电路的 TSV 可降低器件温度约 15 ℃、 提高系统可靠性约 10 倍、 减小布局布线面积中约 80%的保持区域面积(keep-out zone region) , 充分展示了金属性碳纳米管作为三维集成电路通孔材料的电学、可靠性和布局布线优势[158]。综合来看, 碳基三维集成电路目前还处于初级阶段, 既需要解决前文提到的碳基CMOS电路在平面工艺中的诸多问题, 又需要优化多层器件加工工艺以提高器件性能, 如使用更成熟的层间介质平坦化处理工艺以降低上层器件的衬底起伏和电学性能波动, 还需要重点解决三维电路的器件互联可靠性和散热问题。但是,碳基三维集成电路可同时发挥碳纳米管器件的高能效优势以及多功能形态优势(数字计算、射频电子、传感探测等) , 有希望实现感存算传一体化的高能效集成系统(图 16) , 无疑是后摩尔时代集成电路的重点发展方向。

4.5 碳基特种芯片技术

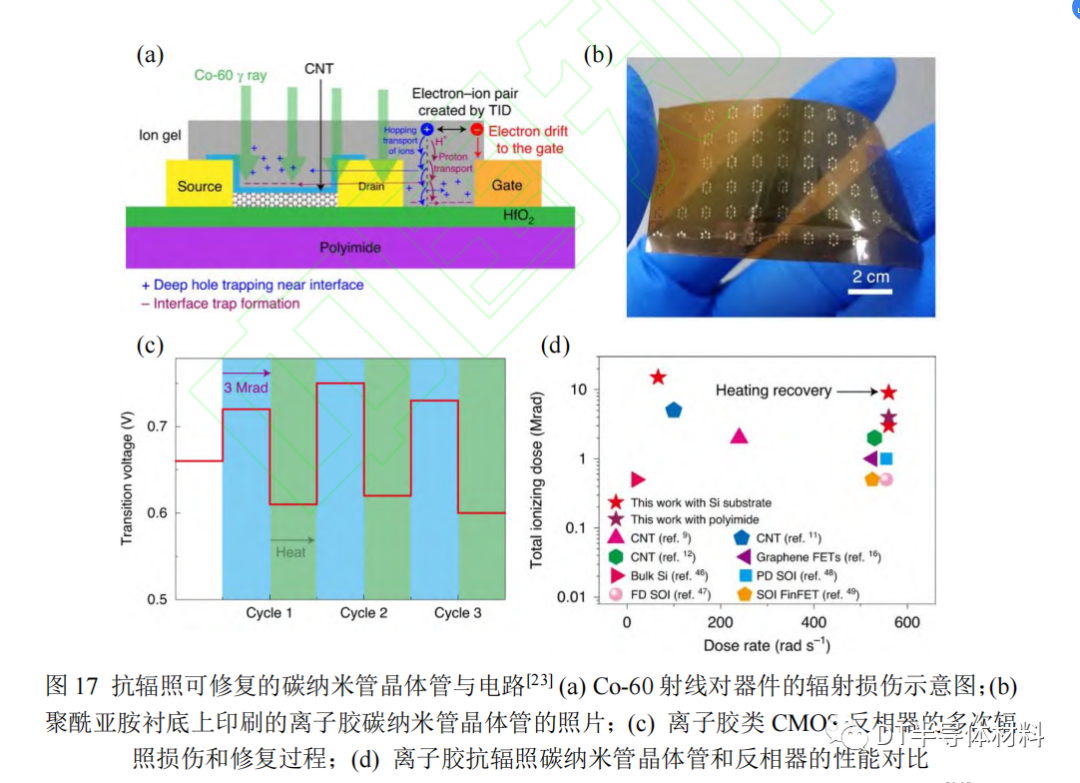

后摩尔时代电子学的发展除了追求更高集成度、更高能效的超大规模集成电路, 还需要发展以各种应用需求为导向的功能器件和电路。而碳纳米管除了优异的电学特性, 还具有其他材料优势, 使其适用于某些特种电路的制造。如碳纳米管具有强碳-碳共价键、纳米尺度的横截面积和低原子数等特点, 因此适合用来制造超强抗辐照电路;碳纳米管可制造无掺杂 CMOS 器件, 其载流子由金属电极注入, 不依赖于掺杂原子的热激发, 因此适合用来制造高性能低温电路;碳纳米管还具有柔韧性好、耐弯曲和耐疲劳强度高的特点, 因此适合用来制造柔性电子器件和电路。由于其独特的低维结构和物理化学特性以及优异的电学性能基础, 碳纳米管可用于制造多个类型的特种芯片, 本节将以碳基抗辐照电路、碳基低温电路和碳基柔性电路这三种功能应用为例, 说明碳基特种芯片的优势与发展潜力。在抗辐照电路方面, 随着我国航天事业的高速发展, 空间站和深空探测等应用都需要性能更好、可靠性更强的抗辐照芯片以避免各种太空辐射效应对电子系统的干扰甚至破坏。因此, 为了构建可用于航天航空级别的碳基抗辐照电路, 北大碳基团队朱马光等人首先分析了典型的顶栅碳纳米管晶体管受辐照损伤的机理, 通过对照试验解耦出了碳纳米管沟道、栅介质和基底这三个部位各自的辐照损伤特性, 发现碳纳米管晶体管中最容易受辐射损伤的是基底部位, 且碳纳米管沟道不仅本身抗辐照能力强, 还能起到保护基底的作用[159]。通过严谨的实验对比和模型拟合, 朱马光等人给出了碳基抗辐照芯片的性能预测:在进一步优化的情况下, 顶栅碳管晶体管可承受 15.5 Mrad 左右的辐照量, 相比于其他半导体材料具备显著优势[159]。基于这一分析和预测, 为了证明碳基器件和电路的抗辐照潜力, 2020 年朱马光和肖洪山等人针对性地采用了辐照加强设计, 系统优化了碳管器件的结构和材料, 制造出了抗 Co-60γ射线总剂量辐照高达 15 Mrad(Si)的可修复碳纳米管器件和电路(图 17) [23]。具体来说, 该工作使用离子胶作为栅介质,可有效减少辐照引入的陷阱电荷, 还使用聚酰亚胺( PI)作为衬底, 可有效消除高能辐照粒子在衬底上散射和反射所产生的二次辐照效应, 即使受到大量辐照损伤而性能下降后, 器件还可以在 100 ℃下退火 10 分钟以修复其电学性能和抗辐照性能[23]。结合超强抗辐照特性和低温加热可修复特性, 未来或许可构建对高能辐照免疫的碳纳米管晶体管和集成电路。此外, 抗辐照芯片不仅包含CMOS器件,还包含各种存储器件。因此朱马光等人还测试了 6T 碳纳米管静态随机存储器(SRAM)的抗辐照特性, 发现即使经受 2.2 Mrad(Si)的 Co-60γ射线总剂量辐照后, 晶体管的阈值电压漂移量依然小于 0.3 V, SRAM 电路仍可正常工作, 说明碳基抗辐照芯片的综合可靠性较高[160]。

在低温电子学方面, 无论是航天航空还是量子计算等应用, 都需要能在低温甚至超低温环境中工作的电路系统, 因此催生了低温硅基 CMOS 技术。然而, 主流的低温硅基 CMOS 技术面临着很多挑战, 如低温下电流过冲、载流子冻结、杂质不完全电离等负面效应, 器件的低温稳定性不够好[161]。与之相反, 基于网络状碳纳米管薄膜的无掺杂 CMOS 技术在低温电路应用中同时具有较强的材料优势和工艺优势:首先, 由于网络状碳管薄膜的随机取向特点, 载流子在沟道中的输运特性由热辅助隧穿机制和声子散射机制竞争决定, 温度依赖性较弱;其次, 无掺杂器件不涉及杂质原子的电离, 载流子密度弱依赖于温度, 器件性能的温度稳定性较好。因此, 碳基无掺杂 CMOS 电路非常适合在低温下工作。2021 年, 北京大学团队谢雨农等人实验探索了碳纳米管晶体管和电路在低温下的工作特性, 并发现当温度从室温降低至液氮蒸发温度时, 网络碳管薄膜晶体管比单管器件和主流的硅基器件都具有更好的温度稳定性[162]。具体来说, 该工作首先测量了网络碳管薄膜晶体管在不同温度下的性能表现, 结果显示:长沟道器件和短沟道器件的性能随温度变化的规律并不相同, 且对于同一沟道长度的器件在不同偏压下的性能变化规律也不同。通过对数据的深入分析, 可发现在网络碳管薄膜中存在两种势垒:碳管-碳管结势垒和聚合物包裹的碳管与金属接触间的势垒, 载流子需要在热辅助下隧穿过这两个势垒, 因此随着温度降低, 隧穿过程导致的电阻会增加。这一变化关系与声子散射随温度降低而减弱的规律截然相反, 互为竞争机制, 因此在合适的偏压和沟道长度下, 碳管器件的性能表现可具备较高的温度稳定性,其电流温度变化系数仅为-0.09%/K, 相比于单管和硅基器件下降了约一个量级[162]。为了进一步验证碳基电路的低温稳定性, 谢雨农等人还制造了五阶环振电路, 其振荡频率在 300 K 至 80 K 的温度范围内均高达 1.5 GHz, 且性能变化小于0.5%, 证明了基于网络状碳管薄膜的碳基集成电路在低温电子应用中的巨大潜力[162]。

在柔性电子学方面, 碳纳米管由于其超薄体特性和机械强度较大的特点, 还适合用来制造机械可靠性较高的柔性电子器件, 并应用于人体可穿戴电子、动植物检测、物联网等场景中。如 2017 年 Ray Baughman 等人基于碳纳米管纱线制造了可与衣物编织在一起的柔性传感器, 可用于呼吸检测[163];2018 年北京大学团队向立等人基于网络状碳纳米管薄膜制造了晶圆级别的柔性薄膜晶体管和电路,可兼容多种衬底如聚合物、人体皮肤甚至树叶表面, 以满足不同的柔性电子应用需求[25]。此外, 柔性电子器件常常面临着性能较低的问题, 其实际商业价值饱受争议。针对于此, 2018 年 IBM 沃森实验室 Tang Jianshi 等人基于高纯度高密度的网络碳管薄膜在柔性聚酰亚胺基板上制造了晶圆级的高性能碳纳米管 CMOS 电路, 基于环振电路提取的单级门延时仅有 5.7 ns, 展现了碳基柔性电路的性能优势[164]。在大规模集成工艺和电路可靠性方面, 由于碳基柔性电路相对于数字逻辑集成电路具有更大的单元器件尺寸, 其平均效应更强, 可以改善材料波动和工艺波动造成的器件均一性问题, 因此可做一些大面积中等性能的应用如柔性显示驱动。2019 年, 中科院沈阳金属所孙东明等人制造了包含 8000 多个碳纳米管薄膜晶体管的柔性显示驱动电路, 其均一性较好(像素良率高达 99.93%)、性能满足需求(开关比可达 107) , 展示了碳基柔性电路的均一性优势[165]。

碳基特种芯片还包括其他类型如透明芯片、瞬态芯片等等, 能满足多种应用场景需求, 具有巨大的发展潜力。但需要强调的是, 无论具体的应用特性如何,碳基特种芯片的基础要求仍然是性能和集成度达标, 因此其现阶段发展挑战仍然是前文提到的材料、器件结构、工艺等基础性问题。

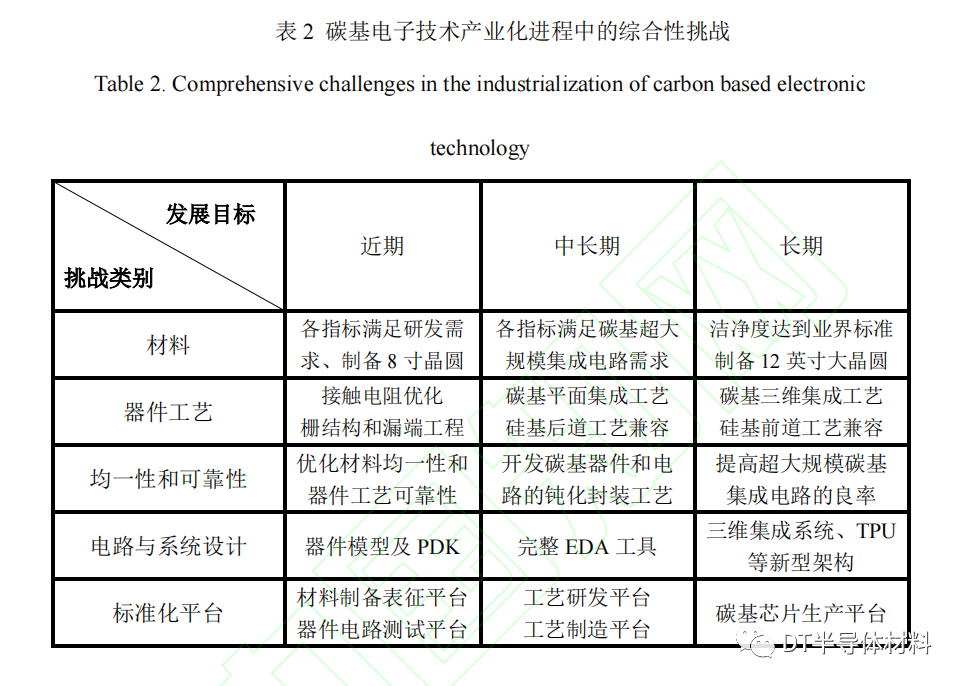

5碳基电子技术产业化进程中的综合性挑战

基于碳纳米管的碳基电子技术已经建立了完整而深入的理论体系、制造了性能优异的原型器件和中小规模电路、探索了多种功能器件和应用潜力, 虽然还存在一些基础性问题有待优化, 但已经没有明显的原理性问题阻碍其实用化和产业化进程。因此, 我们需要开始考虑其产业化进程中的综合性挑战, 从材料、工艺、器件可靠性与均一性、电路系统设计以及标准化平台五个角度分析其发展挑战。

在材料上, 理想的高性能碳基电子技术材料是超高半导体纯度、手性富集或管径均一、密度可控、间距和长度均一、定向排列的晶圆级碳纳米管阵列。目前最接近这一理想材料的是北京大学团队以溶液提纯 DLSA 法制备的阵列碳管, 其各项指标尤其是密度和纯度相比之前的工作都有较大的进步, 基于该材料也首次得到了真实电学性能超过硅基器件的碳纳米管晶体管和电路, 为碳基电子技术产业化奠定了基础[34]。但对于性能和均一性要求最严格的碳基超大规模集成电路而言, 碳管阵列材料仍需进一步优化提高, 包括但不限于以下方面:1. 在不显著增加成本和提纯损伤的情况下, 基于“6 个 9”进一步提高 2 ~ 3 个量级的半导体性纯度;2. 继续提高管径均一性乃至实现手性富集, 降低能带结构不一致造成的本征电学波动;3.严格控制碳管间距, 以提高器件均一性和局部栅控质量;4.实现 8 英寸乃至 12 英寸晶圆的完整覆盖和定向排列;5.彻底去除生长和溶液处理过程的金属离子和聚合物残留或其他杂质, 以提供洁净的半导体材料。此外, 碳管阵列还需要能在多种衬底上完成制备, 以满足射频、柔性电子等应用需求。总之, 与单晶硅材料对于硅基电子产业的重要性一样, 碳基电子技术的蓬勃发展始终离不开材料的持续进步。

在工艺上, 除了前文提到的金半接触、栅极工程等工艺优化方向, 碳基电子技术尤其是碳基集成电路应用还需要尽可能和硅基工艺兼容。这一方面可以极大地节约半导体设备、厂房等“硬”成本, 另一方面也可以借鉴甚至直接使用成熟的硅基半导体工艺, 从而节省工艺研发所需的时间和经济等“软”成本。实现与硅基工艺兼容的第一个障碍是碳管材料的杂质污染问题, 由于碳纳米管在生长过程中常使用金属催化剂、在溶液法提纯和自组装过程中需要使用分散剂和多种有机溶剂, 最终制备得到的碳纳米管晶圆上可能存在大量金属离子和各种杂质微粒,其工艺洁净度远低于硅基半导体产业标准。因此, 我们需要系统检测并去除碳管材料制备中的各种杂质来源, 以避免对半导体工艺设备的污染、提高器件可靠性和晶圆良率。除了洁净度问题, 碳基电子技术基础工艺所用的特种金属如钯也可能不被硅基半导体工艺线所接受, 尤其是硅基前道工艺。这主要是因为使用特种金属可能污染设备腔室, 从而有可能在硅中引入深能级或浅能级陷阱。这一问题的实际影响程度较为模糊, 一方面我们可以通过调整碳基器件的工艺顺序如采用先栅工艺来满足硅基工艺线上不同环节的限制, 另一方面硅基工艺本身在先进技术节点中也在不断引入各种特种金属, 因此特种金属工艺的兼容性问题不会成为根本限制。碳基器件的硅基工艺兼容性可能还有其他挑战, 但其基本发展路径可以分成两步:首先要初步提高材料洁净度, 满足硅基后道工艺兼容性;然后再进一步控制材料杂质, 调整工艺流程, 尽可能匹配硅基前道工艺。综合来看, 碳基电子技术产业化必然需要和硅基工艺部分兼容甚至完全兼容, 以加快其研发速度、降低各种成本。这一目标虽然有一定难度, 但并非不可实现:2020 年, 麻省理工大学Shulaker等人与美国芯片代工企业SkyWater合作, 在商用的硅基芯片产线上制造了 8 英寸晶圆范围内良率可控且均一性好的碳纳米管晶体管, 且碳纳米管薄膜沉积过程没有引入可检测到的杂质污染[166]。

在可靠性方面, 碳管晶体管的失效机制较为复杂, 如 N 型金属电极氧化、超薄栅介质漏电等机制造成的瞬态失效, 栅介质界面态密度较高造成的强 BTI 效应(包括 PBTI 和 NBTI) , 以及接触电极热效应导致的性能漂移等等。提高碳管器件可靠性需要重点解决前文提到的碳基器件基础性问题, 并采用标准化的器件加工工艺和封装工艺。而在均一性方面, 碳基器件的接触电阻、开态电流、阈值电压和亚阈值摆幅等核心参数更是受到多个波动源的影响, 尤其是材料波动、工艺波动、接触界面和栅界面波动。在这些因素被优化改善到一定程度之前, 均一性问题将是限制大规模碳基集成电路正常工作的核心因素。随着研究人员的持续努力, 材料和基本的器件结构工艺已经日趋成熟, 因此系统的可靠性研究需要被介入到碳基电子技术中来。

在电路与系统设计上, 碳基电子技术缺乏配套的电子设计自动化工具(EDA),难以自动化设计电路版图并仿真, 因此难以制造大规模甚至超大规模碳基电路。为了建立系统的碳基 EDA 平台, 首先需要对碳管器件建立完整准确的电学模型,然后根据应用需求开发工艺设计工具包(PDK) , 最后兼容适配于商用的 EDA 工具如 Cadence EDA。然而, 由于碳基器件的工艺在一直被优化, 其器件物理也在不断被修正深入, 目前难以得到一个标准化的工艺流程和器件结构, 也就难以建立准确的器件模型和 PDK。此外, 发展碳基三维集成电路还需要开发出包含层间隔离及通孔工艺描述的3D PDK以及三维电路设计规则, 这为碳基EDA工具开发提出了新的要求。最后, 碳纳米管器件具备高速低功耗的潜力, 如果要保持甚至放大这一能效优势, 可能需要在电路和系统设计上采用新的架构如 TPU 架构, 使用设计工艺协同优化(DTCO)的方法制造电路。

在碳基电子标准化平台方面, 主要包括标准化的材料制备和表征平台、标准化的工艺制造平台和标准化的器件电路测试平台。碳纳米管的材料制备需要标准化的表征方法, 即以合适的测量方法、测量仪器和数值参考范围来表征碳纳米管材料的不同指标。这些指标既包括精度在 ppb(part-per-billion)级别的半导体性或金属性纯度, 还包括碳管密度、管径和长度分布、取向分布、晶格缺陷和排列缺陷密度、金属离子含量、表面聚合物含量以及其他影响器件和工艺的指标。碳纳米管的制造工艺需要标准化, 即使用严格的半导体产业标准工艺, 在标准的超净厂房内, 批量进行大面积晶圆的加工。标准化的器件电路测试平台则有助于加快工艺迭代、提高器件可靠性、探索碳基电路的工艺设计规则。只有完成包括以上环节的制造全流程的标准化, 碳基电子技术才能真正步入产业化阶段。

6总结与未来展望

历经 20 余年发展, 碳纳米管已然成为后摩尔时代中最具潜力、最受关注的新型半导体材料, 碳基电子技术也显现出了其延续、扩展乃至超越摩尔定律的突出技术价值。在诸多碳基电子技术的基础性问题中, 学界已经取得了根本性突破,如理想碳纳米管阵列材料的成功制备、无掺杂 CMOS 技术的发明等等。基于这些材料上和器件工艺上的进步, 碳基电子技术还在多个应用领域中展示了其优势与特色, 如高性能低功耗的碳基数字电路、高速碳基射频器件、超灵敏碳基传感平台和高能效多功能的碳基三维集成系统等等。这些进展说明:碳基电子技术的产业化从原理上看已经没有不可逾越的阻碍, 从技术上看有着充分的商业价值。当然, 想要真正将碳基电子技术从学术界引入产业界和商业界, 还需要对材料、器件结构和集成工艺做进一步优化, 如提高金半接触稳定性、降低接触电阻及栅介质界面态、抑制器件双极性等等。综合来看, 碳基电子技术的原理性优势凸显、工程性挑战与产业化挑战并存, 需要加强产学研合作并借鉴成熟的硅基半导体经验, 从而发展其标准化的材料制备、器件加工、电路设计和表征测试平台。

在目前全球芯片行业商业热情高涨但硅基技术发展却进入瓶颈期的大背景下,碳基电子技术为半导体领域提供了一个应对后摩尔时代挑战的可行技术方案, 更是为我国提供了一次“换道超车”的机遇。结合碳基电子技术目前的发展态势, 其很有可能在短期内实现碳基传感技术等高性能、中集成度的应用, 在中长期实现碳基射频电子、特种芯片等高性能高集成度的应用, 在完成足够的技术积淀以及产业迭代后实现技术复杂度最高、商业价值最大的超大规模碳基数字集成电路。

原文标题:后摩尔时代的碳基电子技术:进展、应用与挑战

文章出处:【微信公众号:微波射频网】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

钠离子电池碳基负极材料研究进展2022-12-29 5844

-

电力电子技术2008-06-23 16831

-

《电力电子技术》电子教案2011-03-10 5963

-

高频电子技术2015-05-10 5122

-

报名 | 宽禁带半导体(SiC、GaN)电力电子技术应用交流会2017-07-11 5066

-

电力电子技术的概念2019-07-10 14976

-

SiC技术怎么应对汽车电子的挑战2019-07-30 3240

-

模拟电子技术概念_模拟电子技术的应用2020-05-15 5473

-

纳电子技术2009-08-03 680

-

碳基双电层电容器的结构机理及研究进展2009-11-16 637

-

电子技术基础实验课件2009-12-07 1070

-

汽车电子技术,汽车电子技术是什么意思2010-03-11 2505

-

《模拟电子技术实验》课件简介2011-03-30 1070

-

印刷电子技术应用2019-05-22 8874

-

中国碳基芯片最新进展20212021-12-16 72051

全部0条评论

快来发表一下你的评论吧 !