基于高分辨率乘法DAC的交流信号处理

处理器/DSP

描述

简介

所有数模转换器(DAC)都提供与数字设置增益和所施加基准电压之积成比例的输出。乘法DAC与固定基准电压DAC不同,因为它可以将高分辨率数字设置增益应用施加到可变带宽模拟信号上。本文将讨论电阻梯乘法DAC及其对交流信号处理应用的适用性。

基本原理

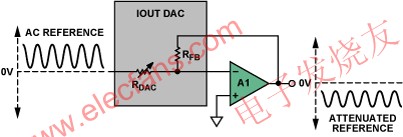

从1974年ADI公司推出世界首款(10 位)CMOS IC乘法DAC 以来,ADI公司就一直是乘法DAC设计与生产的领先者。它们采用一个具有适当带宽的放大器,利用一个切换式R-2R梯和一个片内反馈电阻实现了调整交流增益或可变直流基准电压输入信号增益的简单方法,从而用DAC取代了典型反相运算放大器级的输入和反馈电阻(图 1)。数字调整电阻梯和片内反馈电阻一起,提供与数字输入成比例的增益(D/2n ),使RDAC起到了可变输入电阻的作用。

图 1. 反相增益配置

乘法DAC的市场发展迅速,历经数代更新,产品的分辨率、精度和速度有了大幅提升,增加了各种数字存储功能、串行通信选项,尺寸和成本大大降低并且每个芯片上还可以配置额外的DAC。最新一代的乘法DAC提供理想的构建模块,用于控制可变直流或快速交流电压信号的增益。

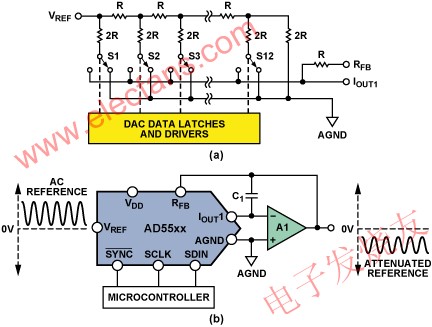

电阻(R-2R)梯用于运算放大器反馈电路,提供数字控制电流,电流经 RFB转换成输出电压。放大器以低阻抗提供此输出。基准电压输入具有恒定的对地电阻R。图 2 显示了该工作原理。图 2a中,源电流VREF/R转换成输出电压。放大器以低阻抗提供此输出。基准电压输入具有恒定的对地电阻R。图 2 显示了该工作原理。图 2a中,源电流IOUT1或导引至地(一般称IOUT2)。同理,剩余电流的一半由开关S2 导引……如此类推。如果开关由一个数字字D(S1 是MSB)激活,则流经RFB (=R)的IOUT1端电流之和为 D × 2–n × VREF/R。此配置的重要优势包括:可最大程度地降低瞬态,因为开关在地和虚地之间切换;RFB与梯形电阻片内匹配,具备出色的温度跟踪性能。

图 2. a) R-2R梯原理;b) 乘法DAC,VOUT = 0 to −VREF.

数字字D给出的数值范围取决于所用的器件。ADI公司的部分AD545x/AD554x系列乘法DAC的D值范围(第一象限)如下:欢迎转载,本文来自电子发烧友网(http://www.elecfans.com )

| 8位 AD5450 | 0 至 255 |

| 10位 AD5451 | 0 至 1,023 |

| 12位 AD5452 | 0 至 4,095 |

| 14位 AD5453 | 0 至 16,383 |

| 16位 AD5543 | 0 至 65,535 |

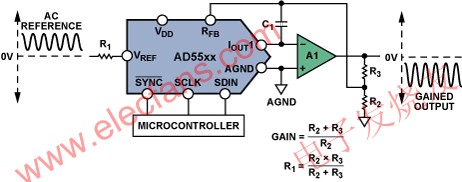

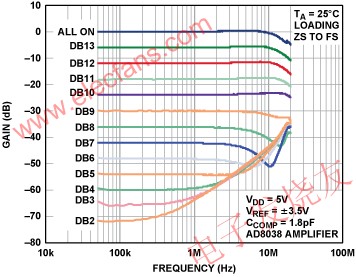

提高增益 图 3. 提高乘法 DAC 的增益 正输出 如果要求差分输出,则需要两个额外的运算放大器。Circuits from the Lab® CN-0143 查看完整的详细信息。 图 4. 乘法DAC, VOUT = 0 to VREF。AD5415、AD5405、AD5546/AD5556、AD5547/AD5557 内置此处所示的非专用电阻 图 5. 单端-差分 稳定性问题 其中GBW是运算放大器的最小信号单位增益带宽乘积,CO是 DAC的输出电容。 信号调理的关键 M-DAC规格 图 6. 乘法带宽 模拟总谐波失真(THD):乘法波形信号中谐波成分的数学表达。它近似等于DAC输出的前四个谐波(V2, V3, V4,和V5)之均方根和与基波值V1(如图7所示)的对数比,计算公式如下: 图 7. 谐波失真分量 乘法馈通误差:DAC的数字输入全部为0时,由基准电压输入至DAC输出的容性馈通所致的误差。理想情况下,一直到最低有效位DB0,每下降一位,增益便降低6 dB(图 8)。不过,对于较低的位,容性馈通影响增益的频率更高。这一点从较低位尾部上翘的平坦曲线可以看出。例如,14位DAC的DB2处,所有频率的理想增益应为–72 dB,但由于馈通效应,1MHz时的实际增益为–66 dB。 图 8. 乘法馈通误差 选择正确的运算放大器 对于基准电压输入为较高速信号的应用,需要一个带宽较宽、压摆率较高的运算放大器,以免削弱信号。一个运算放大器电路的增益-带宽受反馈网络的阻抗水平和增益配置限制。要确定所需的GBW,一种可行的方式是选择–3 dB带宽(10 倍于基准信号频率)的运算放大器。 必须考虑运算放大器的压摆率规格,以限制高频大信号的失真。对于AD54xx和AD55xx系列,压摆率为100 V/µs的运算放大器一般就够了。 表 1 列出了可供乘法应用选择的运算放大器。 表 1. 适用的 ADI 公司高速运算放大器 结论

对于输出电压必须大于VIN的应用,可通过在DAC级后面增加外部放大器来提高增益;或者只需通过衰减反馈电压在单级中实现,如图 3 所示。所示近似值对R2||R3<

要产生正电压输出,可以使用一个外部反相运算放大器电路来另外反转输入或输出。 一些乘法DAC内置非专用匹配电阻(具有跟踪温度系数),因此只需额外连接一个运算放大器(图 4 中的 A2)即可获得正输出,这个额外的运算放大器可以是一个双通道器件内的配套运算放大器。

图 2 和图 3 中显示的一个重要元件是补偿电容(C1)。电阻梯的输出电容加上放大器的输入电容及任何杂散电容,会在开环响应中产生极点——这会在环路闭合时引起振铃或不稳定。为了补偿这一点,通常与DAC的内部RFB并联连接一个外部反馈电容C1。如果C1值过小,会在输出端产生过冲或振铃,而值过大则会过分降低系统带宽。DAC的内部输出电容随码而变化,因此C1很难确定精确值。根据以下等式可计算出其最佳近似值:

乘法带宽:增益为–3 dB时的基准电压输入频率。对于给定器件,它与幅度和选择的补偿电容呈函数关系。图 6 所示为可以使最高12 MHz的信号相乘的电流输出DAC AD5544、AD5554或AD545x的乘法带宽坐标图。配套的低功耗运算放大器 AD8038具备350 MHz带宽, 可确保该运算放大器在此范围内不会引起明显的动态误差。

乘法DAC电路性能非常依赖于所选运算放大器的能力,从而在电阻梯输出端保持零电压,并实现电流电压转换。要实现最佳的直流精度,重要的是要选择具有低失调电压和偏置电流的运算放大器,以保持误差与DAC的分辨率相当。详细的运算放大器技术规格参见器件数据手册。

产品型号

(V)

(MHz)

(V/µs)

(µV)

(nA)封装

AD8065

SOIC-8, SOT-23-5

AD8066

SOIC-8, MSOP-8

AD8021

SOIC-8, MSOP-8

AD8038

SOIC-8, SC70-5

ADA4899

LFCSP-8, SOIC-8

AD8057

SOT-23-5, SOIC-8

AD8058

SOIC-8, MSOP-8

AD8061

SOT-23-5, SOIC-8

AD8062

SOIC-8, MSOP-8

AD9631

SOIC-8, PDIP-8

自首款CMOS M-DAC问世以来的近40年间,相关器件不断更新换代,许多新的功能特性层出不穷,性能持续提升,成本和尺寸则大幅缩减。我们的高分辨率、14位/16位电流输出DAC产品系列AD55xx的最新性能改进包括:欢迎转载,本文来自电子发烧友网(http://www.elecfans.com )

-

投影机的最高分辨率的定义2009-11-17 0

-

用高分辨率示波器测量微小信号2018-03-21 0

-

如何设计高速高分辨率ADC电路?2021-04-23 0

-

如何实现DCP的高分辨率控制?2021-04-27 0

-

如何实现连续脉冲信号的高分辨率延迟?2021-04-30 0

-

超高分辨率图像实时显示系统设计2009-07-09 595

-

采用高分辨率乘法DAC处理交流信号2010-11-27 699

-

如何优化高分辨率DAC的DC测量2011-01-09 769

-

凌华科技高分辨率动态信号采集模块PCI-95272011-03-07 3254

-

基于FPGA的高分辨率全景图像处理平台2015-11-04 637

-

垂直分辨率与使用高分辨率示波器测量微小信号的介绍2017-09-29 1503

-

高分辨率信号空调系统的浅析2017-11-23 990

-

新型电阻梯乘法DAC应用于交流信号处理2019-04-09 4502

-

什么是高分辨率示波器?它有哪些优势?2024-08-08 974

-

使用MSP430高分辨率定时器的PWM DAC2024-09-20 123

全部0条评论

快来发表一下你的评论吧 !

赚取积分