HUB控制芯片VL817S与其他型号的区别及改动

HUB控制芯片VL817S与其他型号的区别及改动

描述

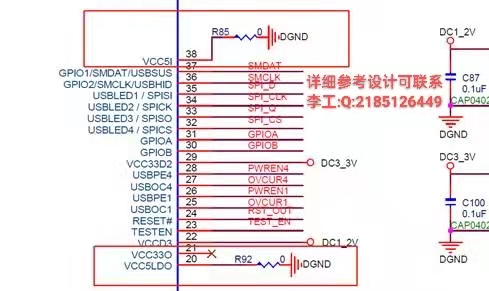

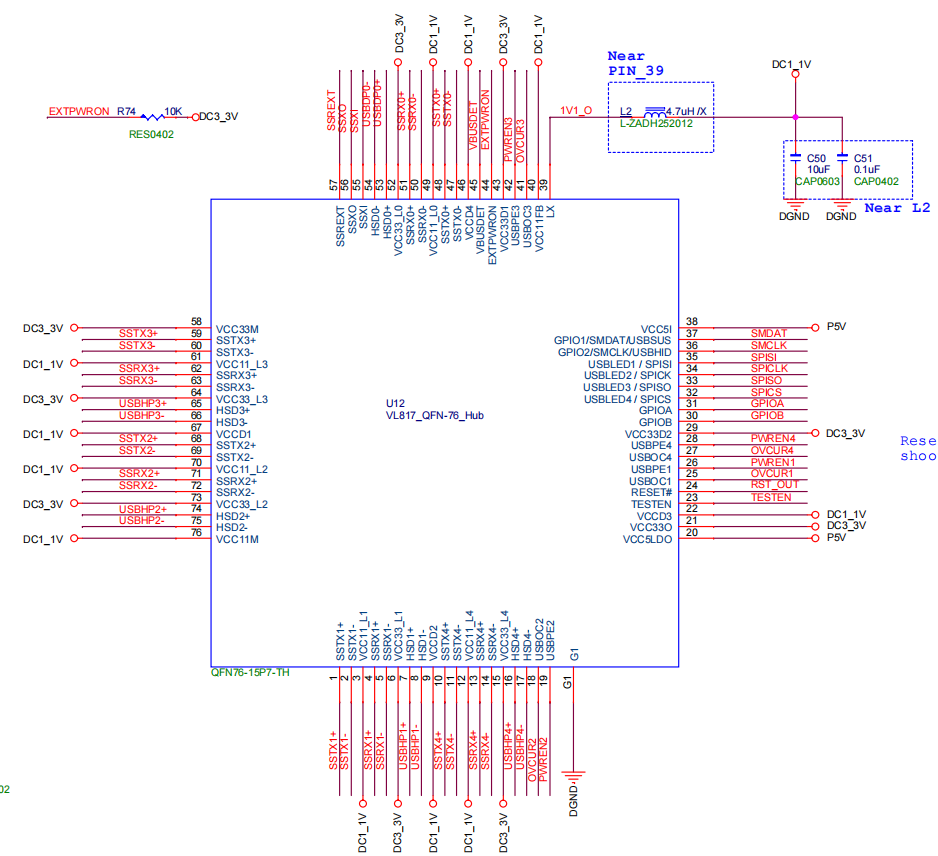

相对于VL817C0以及VL817B0来说,VL817S使用外部供电不需要接入5V,HUB 5V 请参考参考设计接地。内部3.3 LDO输出请悬空。1。2V LX和FB请悬空。如下所示,详见参考设计。

1、3.3V和1.2V之间的时序要求是怎么样的?

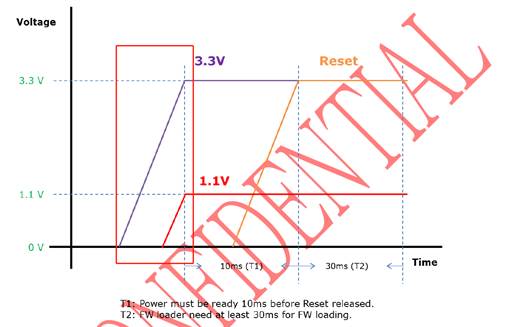

下图是VL817(S) 上电时序。参考线路中有增加不上件0。1uF调整时序。

2,各电源的纹波要求是怎么样的?

没有特别要求。DC-DC基本都可以满足纹波要求

3、817B0/C0和817S这三款芯片的对比测试数据以及产品替换,可根据你们

的数据来评估重点测试内容及注意事项

内部测试目前来说OK,可进行PIN TO PIN D迭代代替

4、需要提供LAYOUT指导说明文件或者参考的PCB文件

请对比VL817B0/C0规格书以及相关原理图,结合以上更改参数进行对照修改。

VL817相关原理图:

VL817 Power On Sequence上电时序:

1.1V 和3.3V 理论上需要同时起来,误差需保证两个电压上电间隔超过1mS

以上即是VL817S与其他型号相同之处,但是总的来说:

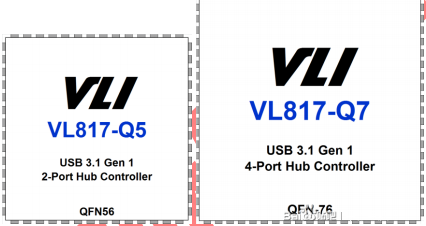

1. VL817 C0/B0 与VL817S pin to pin 的产品

2. VL817 C0/B0与 VL817S均为独立FW

3. VL817 S为VL817C0//B0的进阶版本

4. VL817S采用外置LDO供电,

并且VL817-Q7S(A1)性价比更高。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

USB3.0 HUB芯片《VL817-Q7S》威锋HUB芯片2025-02-15 2965

-

VL813/VL817/VL820 HUB USB3.0集线器HUB拓展坞芯片对比及应用2024-05-09 4456

-

国产首款USB3.0HUB芯片成功进入商用可兼容RTS5411、VL817、GL35102023-03-15 9486

-

VL817以及迭代型号VL817S原理图规格书示例2023-02-17 4703

-

国产USB 3.0 HUB一扩四,可替换VL817/GL3510/RTS54112022-10-10 6875

-

细说VL817S与VL817-Q7的区别2022-09-20 5414

-

VL822- GEN2简述及运用(USB3.1 10Gbps HUB芯片)2022-09-13 30248

-

VL817是一款USB 3.1 Gen 1 Hub控制器2022-06-22 3394

-

基于VL813芯片的USB3.0 HUB方案2022-05-27 6317

-

分享一个不错的基于VL817-Q7的USB3.0 HUB方案2021-06-15 3612

-

VL813 HUB USB3.0集线器芯片2020-06-20 3766

-

USB3.0 HUB方案之VL817-Q72020-03-13 21435

-

Linux与其他操作系统的区别2009-01-18 1919

全部0条评论

快来发表一下你的评论吧 !