基于HyperLynx仿真的高速PECL时钟电路设计

测试测量实验

描述

引言

随着电子技术的不断发展,数据的传输速度越来越快,高速时钟的应用日益广泛,如何保证时钟在高速跳变过程中的信号完整性、抖动、功耗等问题,已逐渐成为关注的问题。传统的时钟设计方法大多依靠经验和理论计算,但是随着时钟频率越来越高,时钟的电磁环境日趋复杂,时钟的传输线效应、过冲/欠冲、反射、振铃效应、趋肤效应都成为影响时钟设计的关键因素,只有使用现代科技手段,利用计算机的强大计算能力进行仿真才能够保证时钟电路设计成功。 HyperLynx是Mentor(GraphICS开发的一款板级信号完整性的仿真工具。它可以进行损耗传输线的精确仿真,支持IBIS模型和HSPICE模型,可以使用过孔模型,允许多种激励源,可以分析信号的眼图、抖动以及EMC(电磁兼容性)辐射,用户界面简单直观。

在目前的高速时钟的电平标准中,PECL(正电压射极耦合逻辑)是应用较广泛的一种,绝大多数高速ADC(A/D转换器)、DAC(D/A转换器)器件都支持这一时钟电平。本文叙述。PECL的原理和常见端接方式,结合在ADc系统中的应用,使用HyperLynx工具对设计后的电路进行仿真以验证设计思想。

l PECL工作原理

PECL由EcL(射极耦合逻辑)标准发展而来,在PECL电路中省去了负电源,较EcL电路更便于使用。PECL信号的摆幅相对EcL要小,欲了解更多信息请登录电子发烧友网(http://www.elecfans.com),这使得该逻辑更适合于高速数据的串行或并行连接。

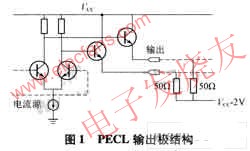

一个标准的PECL输出极如图1所示。

差分对管的射极通过电流源连接到地,差分对管驱动一对射随器以提供正、负输出。输出射随器工作在正电源范围内,其电流始终存在,这样有利于提高开关速度。LVPECL(低电压。PECL)输出极的标准输出负载是接50 Ω电阻至 Vcc一2 V的电平,在这种负载条件下,由于射随器的基极一射极有0.7 V压降,故输出+与输出一的静态电平典型值为Vcc一1.3 V,0.7 V压降加在50 Ω终端电阻上的电流为14 mA,可知输出+与输出一电流为14 mA。PECL结构的输出阻抗典型值为4 Ω~5 Ω,表明它有很强的驱动能力。

2时钟电路设计

下面根据具体应用进行设计。首先从时钟的发送端(输出)和接收端(输入)各自的特性着手进行设计。

2.1时钟输出结构

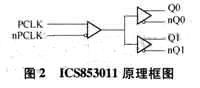

时钟输出端由时钟扇出芯片ICS853011的一对输出引脚担任。ICS853011是一款将任意差分时钟扇出为两路PEcL电平的时钟扇出芯片,其原理见图2。

当其供电电压为3.3 V时,其输出电气特性如表l所示,输出高电平在2.295 V左右,输出低电平在1.52 V左右,输出峰峰值约为800 mV。

2.2时钟输入结构

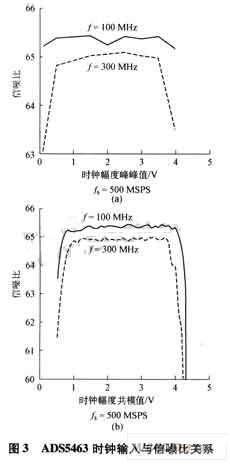

ADS5463的时钟输入特性如图3所示。

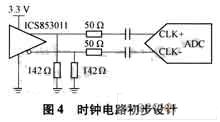

由图3可看出时钟的输入幅度和共模电压与ADC信噪比的关系,当输入时钟为300 MHz时,只有峰峰值大于O.5 V、小于3.5 V,共模电压大于1 V、小于3.5 V才有最佳的信噪比指标,LVPECL电平的共模电压为Vcc一1.3 V="3".3 V-1.3 V="2" V,典型峰峰值700 mV,刚好满足ADS5463对时钟的要求。ADS5463在时钟输入端由内部电阻将时钟输人共模电压偏置到2.4 V,这与发送端的共模电压不同,故采用交流耦合是最好的方式。时钟电路初步设计见图4。

如图4所示,在ICS8530ll的每个输出端都并联了一个142 Ω的电阻到地,这个电阻的作用是:由于输出共模电压固定在Vcc一1.3 V="2" V,为了使输出电流维持在14 mA,故直流偏置电阻值选择2 V/14 mA="142" Ω,实际选取时可选择140~200 Ω。此时双端传输线特性阻抗为50 Ω。

3电路仿真

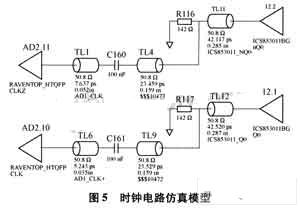

下面打开HyperLynx,将上述电路导入其中的LineSim工具下,该工具是HyperLynx的一个子工具,主要用来进行传输线的拓扑结构的仿真,可以对不同端接方式下的信号完整性进行分析。LineSim中的传输线模型构筑如图5所示。

图5中的传输线模型由发送端、线阻抗、路径上的相关器件与接收端组成。发送端和接收端的仿真模型是一种IBIS仿真文件。IBIS是对输入输出端口的电气特性快速准确建模的方法,是反映芯片驱动和接收电气特性的一种国际标准,它提供一种标准的文件格式来记录如驱动源输出阻抗、上升/下降时间及输入负载等参数,非常适合用于振荡和串扰等高频效应的计算与仿真。这里选择发送端为ICS85301l的模型,而接收端为ADS5463的模型,图中线路阻抗选择50 Ω,两个输出端并联到地的电阻为142 Ω,线路上的隔直电容为100 nF。

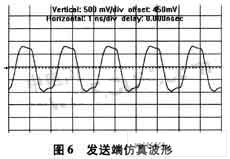

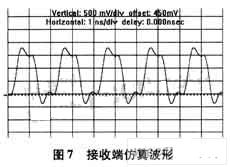

输入激励设置为.500 MHz、占空比为50的时钟源,在LineSim的数字示波器的仿真结果窗口中显示的波形如图6和图7所示。

图6和图7显示的是信号的差分值。可以看出,信号在发送端的失真还可以接受,但是在接收端的波形出现了较严重的振铃现象,其原因可能是:传输线阻抗和负载阻抗不匹配,导致信号发生反射,引起振铃现象;端接的拓扑结构不对,采用了错误的端接方式。 传输线理论中对于振铃现象原因的分析是:当传输线阻抗大于信号源阻抗时,信号源段反射系数为负值,这时将产生振铃现象。结合本电路分析,由于信号源阻抗是ICS853011内部的输出射随器的输出阻抗,约为4 Ω,而此时的传输线阻抗为50 Ω,过强的驱动能力导致负载端出现振铃现象。

消除振铃现象的方法有降低系统时钟频率、缩短传输线长度、采用正确的端接方式3种。由于本系统的时钟频率是固定的,而传输线长度又由PCB(印制电路板)的物理布局所限定,故只有采用正确的端接方式最为经济灵活。常见的端接方式有源匹配和负载匹配,下面介绍这两种方法的原理。

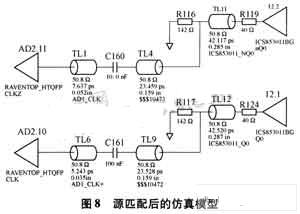

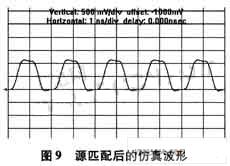

源匹配要求为输出端串联一个电阻,使源阻抗R。等于线路阻抗Z。,串联后,源反射系数等于0,从而消除了负载上的反射信号。换言之,串联的电阻吸收了发射的信号。本电路改进后如图8所示,在输出端串联了一个的电阻Rs,Rs=z0一R0=50-4=46 Ω,串联后的接收端波形见图9。从图9可看出,串联一个电阻后,接收端的波形得到了很大改善。但是这种方式稍微减小了接收波形的幅度值。但总的来说,信号还在ADC的接受范围内,不会对ADC性能有较大影响。

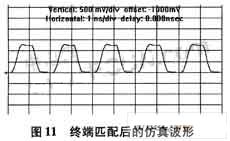

为了不衰减时钟信号的幅度,另一种较好的匹配方式是终端匹配。终端匹配的原理是在走线路径终端并联一个电阻RL在接收端负载上,使总的负载ZL=Z0,从而使反射系数,以消除反射,在这里采用交流负载匹配,即由一个电阻RL串联一个电容CL然后并联到原接收端负载上,这样相比单接一个电阻最大的好处是可以降低直流功耗。改进的电路如图10所示。

图11所示为由HyperLynx的仿真波形,可见这种方式也改善了接收端波形,同时减少了直流功耗。

在实际的时钟电路设计中,不仅需要考虑端接方式和器件值大小,还需要考虑器件的摆放,如端接电阻和必须尽可能靠近接收端、源电阻必须尽可能靠近发送端、器件与走线方向一致等;同时,布线必须严格按照差分规则,保证两差分线之间间距相等、两线线长相等,与周围高速数字线保持2倍以上的线间距,只有这样才能最终实现高性能的时钟设计。

4结束语

在高速时钟电路的设计中,信号完整性问题一直是困扰设计人员的问题,本文提出的PECIL高速时钟设计是在ADC设计中成功与否的关键因素。通过HyperLynx仿真,可以在最大程度上避免设计中的信号完整性问题。本时钟设计已在PcB实物上得到验证,取得了与仿真一致的效果,证明使用 HyperLynx辅助设计人员进行关键时钟路径的设计是可行的。欲了解更多信息请登录电子发烧友网(http://www.elecfans.com)

-

zhangh236

2013-12-12

0 回复 举报信号完整性的问题都归结到沿时间的减少 收起回复

zhangh236

2013-12-12

0 回复 举报信号完整性的问题都归结到沿时间的减少 收起回复

-

zhangh236

2013-12-12

0 回复 举报减少振铃通过降低信号频率是没有用的,要降低沿时间 收起回复

zhangh236

2013-12-12

0 回复 举报减少振铃通过降低信号频率是没有用的,要降低沿时间 收起回复

- 相关推荐

- 热点推荐

- HyperLynx

-

HyperLynx 2409新增功能和改进功能2024-11-04 2224

-

时序仿真与功能仿真的区别在于2023-09-08 7395

-

模拟电子:电路仿真的作用2023-02-17 6513

-

AN4803 在STM32微控制器上使用IBIS高速SI仿真和使用HyperLynx-SI进行板级仿真2022-11-21 645

-

高速电路设计交流2022-03-31 706

-

基于高速CMOS时钟的数据恢复电路设计与仿真2018-04-09 1376

-

Hyperlynx对PCB信号完整性仿真2016-06-15 5087

-

华为Hyperlynx仿真教程2016-05-17 1347

-

HyperLynx仿真与PCB设计!高速PCB热仿真2015-05-17 15218

-

请问各位高手,有用PADS设计高速pcb,然后永用hyperlynx仿真2014-10-28 5618

-

基于LabVIEW的数字电路设计和仿真2010-03-30 1286

-

高速数字电路的仿真2009-03-20 1705

-

HYPERLYNX 仿真工具使用指南2008-08-05 17855

-

阻抗匹配中的Hyperlynx应用2008-07-17 6156

全部0条评论

快来发表一下你的评论吧 !