MyHDL“用python设计电路”

电子说

1.4w人已加入

描述

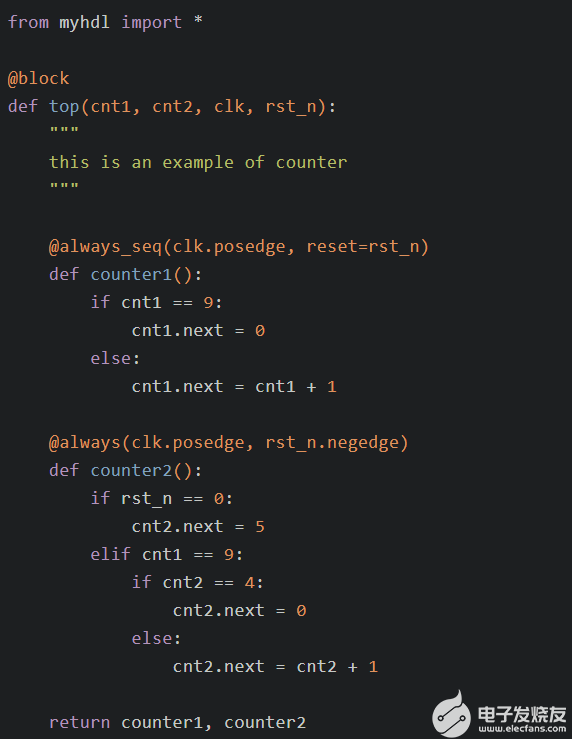

写代码:

下面的myhdl代码写了一个模块top,里面有两个计数器:cnt1从0计到9,当cnt1=9时,cnt2从0计到4。

从上面的代码可以看到其实与verilog非常接近,只是复位和时钟在python装饰器always和always_seq里实现了。另一个特殊点是,给一个信号赋值需要用xxx.next,这样就描述了DFF的功能,赋的值下一个时钟生效。

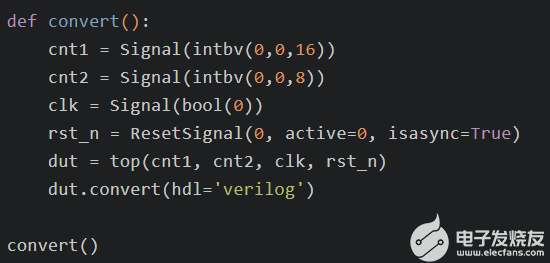

转Verilog:

我们用下面的方法来把myhdl转成verilog:

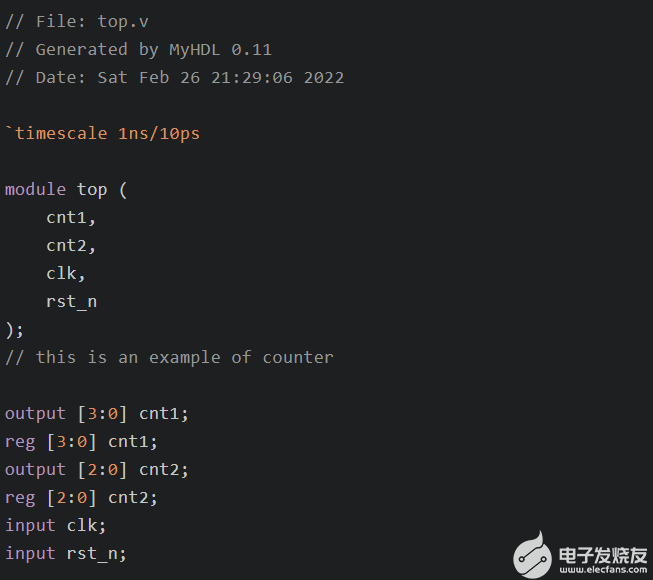

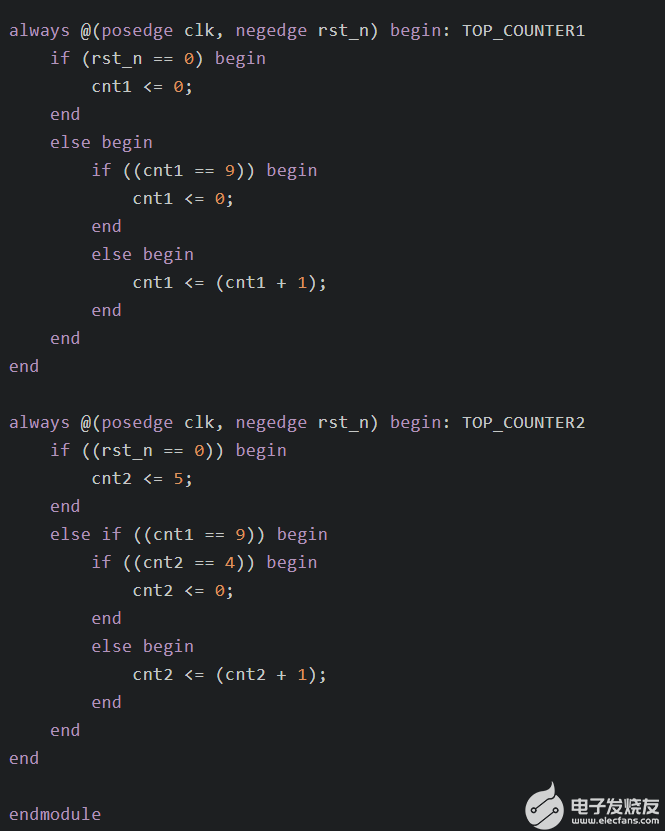

直接上效果,不解释了,大家自己看:

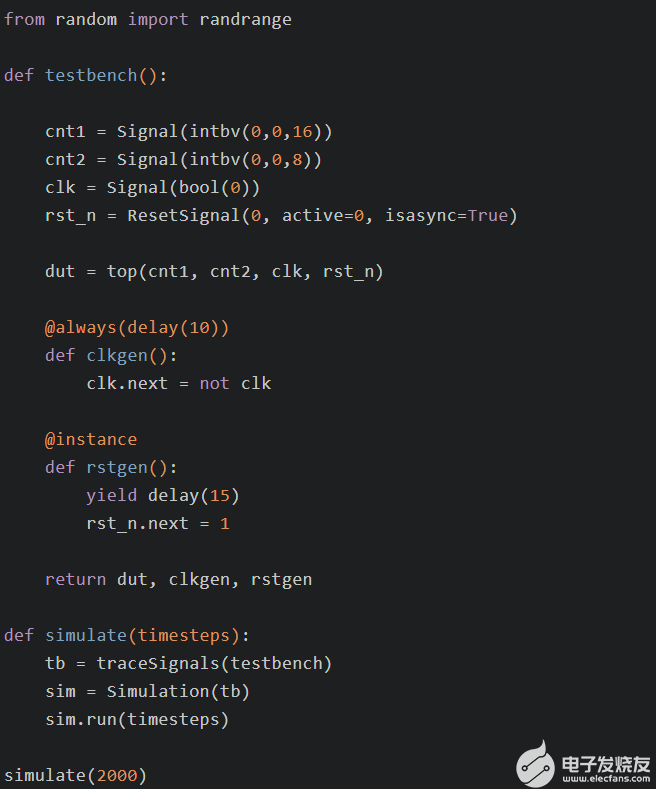

写验证环境,仿真:

与Verilog的验证环境没有太大区别,实例化、编写时钟、复位等激励,设置dump波形,仿真时间等。

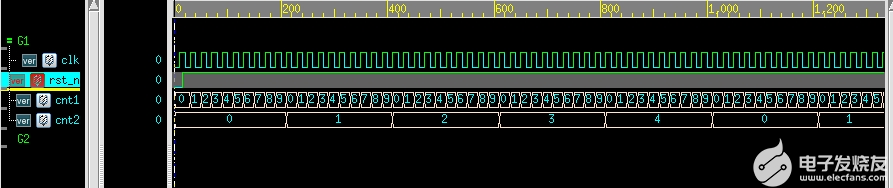

看波形:

运行后目录下产生testbench.vcd。用Verdi打开如下图:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

使用Python MyHDL有哪些注意事项?2021-06-23 12111

-

Python硬件验证——摘要2022-11-03 29593

-

详细用Python写网络爬虫2017-09-07 938

-

python用什么编译器2017-11-20 28539

-

基于Python软硬件协同设计方法,仿真和校验的流程介绍2018-11-23 3930

-

python基础教程之Python的MyHDL详细说明和使用手册免费下载2018-09-18 2555

-

用Python写网络爬虫2021-06-01 947

-

开源工具SkiDL - 用Python来描述电路2021-10-30 4678

-

自学python单片机编程-用Python语言控制单片机2021-11-13 2300

-

用Python学习科学编程2022-03-09 831

-

用Python语言演示Arduino Uno的功能2022-11-04 982

-

用Python写个小工具网页2023-03-03 2487

-

python有什么用 如何用python创建数据库2023-08-28 2075

-

用python写验证环境cocotb2024-07-24 1906

-

使用Python/MyHDL创建自定义FPGA IP2026-04-09 252

全部0条评论

快来发表一下你的评论吧 !