基于DSP芯片实现雷达回波信号采集和处理系统的设计

电子说

描述

1引言

反应速度更快、精度更高、目标的自动录取、使操作员能够同时处理多批目标,是现代雷达所追求的技术指标。雷达视频信号的数字采集和检测是达成这样目标的前提条件。众所周知,雷达对目标位置的测量,主要是依据目标回波相对于发射电波的延迟时间以及雷达天线的方向来决定的。电波的传播速度极快,传播l海里的时间大约只有12.35μs,雷达发射电波的间隔一般在ms数量级。在此间隔时间内,理论上最多会有成百上千个目标的回波。要在如此短的时间之内,对这么多的目标回波信号进行数字采集和处理,快速的采集器件及高速计算机处理器必不可少。DSP(DigitalSignalProcessor)芯片,即数字信号处理器,就是这样一种特别适用于进行这种实时信号处理的微处理器。本文以某雷达的技术参数为参考,用TMS320VC5402作为信号处理器,以AD9223为A/D变换器,采用双端口存储芯片IDT7203作数据暂存存储器,介绍一种实现雷达回波信号的数字采集和处理方法。

2主要器件特性

TMS320VC54x是TI公司开发的低功耗、高性能数字信号处理芯片,主要应用于无线通信系统及雷达信号处理系统等。本文所采用的TMS320VC5402芯片是此系列的一个典型产品。该芯片的主要特点有:速度快,指令周期10ns,运算能力为100MIPS;强大的寻址能力,最大可寻址外部存储器1M×16位,内置16K×16位的RAM,4K×16位的ROM;40位的算术逻辑运算单元(ALU),包括2个独立的40位累加器和1个40位的桶形移位寄存器;1个17位×17位的硬件乘法器和1个40位的专用加法器,乘法器/加法器单元可在一个流水线状态周期内完成一次乘法累加运算(MA)。

AD9223是一种采用高速CMOS处理和新颖的4级流水线结构的高性能、低噪声、单电源、12位模/数变换器。适用于航海、通信、雷达、医疗等领域的数据采集系统。其主要特点有:高速度、高分辨力,采样时钟频率可达3Msps,分辨力为12位;单时钟输入,采用单时钟输入控制内部所有的转换周期;模拟信号输入灵活,真正的差分输入结构允许模拟信号以单端或差分两种分式输入;灵活的参考电压,适应不同应用的精度及温度漂移的要求,参考电压可选择内部或外部(1V或2.5V);采用4级流水线结构及宽带取样保持放大器(SHA),使器件在每个时钟周期都可捕获输入的采样信号,数据的输出延时为3个时钟周期。

IDT7203是一种双端口先进先出(FIFO)9位存储缓冲器,存储容量为2KB。输入和输出具有各自的地址指针,每一个读或写操作,对应的输出及输入地址指针自动加1。复位信号可将两个地址指针全部清除。对外提供数据区空(empty)、半满(half-full)及满(full)信号,用来指示器件的状态。最快读写速度为12ns。

3二级门限判决的工作原理

雷达的视频信号中始终包含有目标信号和噪声信号,即x(t)=s(t)+n(t)。雷达信号处理的根本目的就是,从接收到的视频信号x(t)中提取出有用的目标信号s(t),滤除无用的杂波或干扰信号n(t)。在进行雷达信号处理时,预先并不知道目标在一定条件下出现的概率,也很难确定一次漏警所造成的损失,故常采用奈曼一皮尔逊准则,即在允许一定虚警概率的条件下,使漏警概率达到最小。二级门限判决方法,是一种有效而实用的雷达信号处理方法。

3.1二级门限判决原理

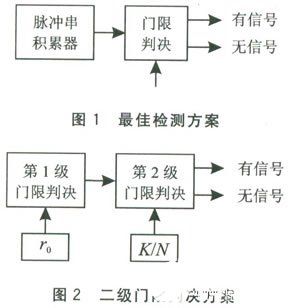

由最佳检测理论知道,对于非相参高频脉冲串,采用检波后的积累(视频积累)来改善雷达检测性能是一种最佳方案,其原理如图1所示。这种方案若采用模拟电路处理,比较复杂,实现起来也相当困难;若采用数字化处理,直观的办法是将雷达接收机的视频信号按距离(时间)和幅度进行量化处理变为数字信号,然后存储N个重复周期。对每一个重复周期按距离单元对每一个单元的信号幅度值设定一个门限值(r0),称为第一门限。对每一个重复周期所量化的所有距离单元的视频信号值x(TI),与其相对应的门限值roi进行幅度值的比较。如果视频信号值超出它的门限值,认为是“可能目标”信号;否则,认为无信号。这个过程称为第一级门限判决。对应于每一个重复周期内每一个距离单元所建立的第一门限值(roi)是各不相同的,而且,每一个重复周期所建立的也各不相同。这里将每一个重复周期所建立的第一门限值的集合称为杂波均值估值表或叫杂波图。对于“可能目标”信号,并不能肯定它一定是目标信号。因为有时突发的杂乱干扰信号或随机噪声信号,各次扫描的取样是不相关的。它们可能会偶然一二次超过第一门限值,但连续多次超过第一门限值的可能性很小;而对于目标来说,相邻各次扫描均应有回波信号,在N个取样中连续超过第一门限值的概率较大。因此,需要按距离单元将超过各自第一门限值的量化脉冲进行计数,如果在N个重复周期中有K个以上的量化脉冲超过各自的第一门限值,则判决为有信号。这个过程称为第二级门限判决(K/N判决),而K/N称为第二门限值,工作原王单如图2所示

3.2杂波均值估值表的建立

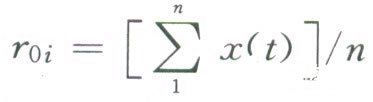

杂波均值估值表(杂波图),是根据每个重复周期雷达视频信号的量化值所建立起来的每个距离单元的杂波信号的平均值表。建立的方法为邻近单元平均估值法。具体是,设某个距离单元TI上的视频信号为x(TI),以ti单元为中心,前后共取n个参考距离单元,对这n个参考单元的视频信号数值求平均值

作为这个距离单元的杂波平均估值。也叫作这个距离单元的第一门限值roi值的大小由雷达探测区域的杂波环境所决定。n值愈小,由于参考单元太少,会引起杂波平均估值的起伏变化愈大,将引起虚警概率的增加;而n值愈大时,杂波的平均估值起伏愈小,即第一门限值愈平稳,可得到恒虚警效果,但会使得资源开销增大,增加实现的难度。对于气象和海浪杂波来说,它们通常是连接成片的区域,比较适合采用邻近单元平均估值法建立杂波均值表。这里n取16。由于以52.5m为一个距离单元,相当于对检测点前后各420m的距离范围取杂波的平均估值。

3.3第二级门限值K/N的计算

为保证符合奈曼一皮尔逊准则,N值的选择应取决于天线波束扫过目标的时间内目标的回波脉冲数,是由雷达的工作参数决定的。对于某船用雷达来说,其部分工作参数为:重复频率1200Hz,触发脉冲宽度O.7μs,天线转速20r/min,天线波束宽度O.7°,作用距离40海里。N的取值为N=O.7×1200/(20×6)=7。根据经验,K的取值为1.5√N。这里K=4,即K/N=4/7。

4硬件电路设计

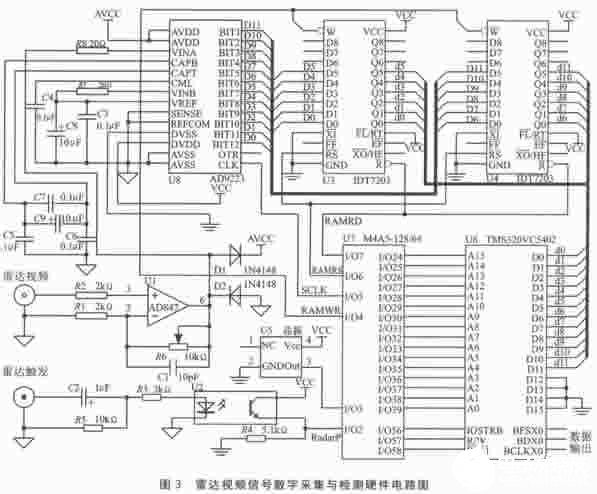

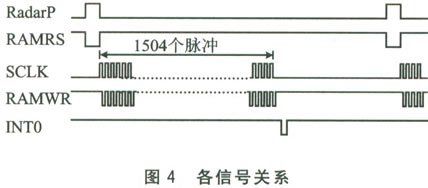

硬件电路工作原理如图3所示。根据雷达的主要技术参数,得知雷达的距离分辨力为150×0.7=105m,在不降低原雷达性能的前提下,这里选择2.857142857MHz的采样频率(相当于以52.5m作为一个采样距离单元)。存储器以同样的速率采集数据(大约每52.5m采集一个雷达视频信号的数值)。这样的话,40海里的最大测距量程,对应于雷达的每一次发射,电路应当采集1412个距离单元的视频信号量化值(这里取1500个距离单元),因此,双端口RAM容量选用2KB即可。由于访问速度要快,选用了IDT7203。对于信号的量化位数,即A/D转换位数的选择,考虑到量化噪声的影响,所取的位数愈多影响愈小。为照顾DSP的处理能力以及A/D转换器件的转换速度,采用12位。

A/D转换器AD9223的设置:采用片内2.5V作为参考电压;VINB接参考电压值,这样VINA的输入值最大可到5V,最小为OV;运算放大器U3提供的视频信号应当符合这个要求。

DSP对中断信号响应后,执行数据接收的中断服务程序。该程序以极快的速度把双端口RAM中的数据提取到自己的内部存储器中,这时DSP再运行滤波和目标提取程序,最后将完全处理好的数据通过串行接口传送出去。

双端口RAM的读信号RAMRD在执行读OFF00H地址的指令时,由DSP产生的地址信号(OFF00H)、WR信号以及10STRB信号的共同作用而产生。

5软件设计

软件的主要任务是处理已经被数字化了的视频信号。为了实现快速处理,程序采用汇编语言编写,保证在一个重复周期内将数据处理完毕。程序运行的区域安排在TMS320VC5402片内RAM的0000H~03FFH的1KB内存中。数据输入区在0400H~09FFH,占1.5KB内存。杂波均值估值表(杂波图)位于OA00H~OFFFH,占1.5KB内存。输出数据区(处理结果)位于1000H~15FFH,占1.5KB内存。从1600H开始至3FFFH的10.5KB存储区,被平均分为7个数据区,作为7个重复周期的数据积累区。对于存储雷达视频信号量化数据的每一个存储区,其每一个地址单元的地址代表一个距离单元,其内存储的数据代表该距离单元处视频信号的幅度量化值。程序响应中断后,工作过程为:数据的采集→建立杂波均值估值表(杂波图)→第一门限判决→第二门限判决→数据输出。方位信号的采集以及处理以后数据的输出,此处不作讨论。

5.1数据的采集

由于TMS320VC5402运行的速度极快,单指令周期为10ns,而双端口RAM的最快访问速度为12ns。为了保证数据的可靠读取,把I/0操作设置为延迟2个执行周期。DSP对于外部中断0(INTO)响应后进人中断服务,把双端口RAM中的数据读到DSP的内置存储器以0408H起始的1500个单元中。程序初始化时,将0400H起始的8个单元设置为0。这完全是为了计算杂波均值估值表(杂波图)时的编程方便,其程序如下:

GETDATA:STM#0408H,AR6;初始地址

RPT#(1500—1);重复次数

PORTROFF00H,*AR6+;读数

据

RETE ;中断返回

5.2建立杂波均值估值表

根据3.2杂波均值估值表的建立方法,对每一个距离单元,前取8个,后取7个,共16个作参考单元,计算平均值,作该单元的杂波均值估值。总共计算1500个距离单元的杂波均值估值,放置于OA00H~OFFFH的存储区域。具体实现时,须先计算出第一个单元的杂波平均值估值,其后的逐个计算。程序代码如下:

STM#O4ooH,AR5;读入数据的首址

STM#OA00H,AR7;均值估值首址

RPTZA,(16—1);循环16次

ADD*AR5+,A;求和

STLA,一4,*AR7+;除以16,放入估值表

STM#0400H,AR6;计算余下的1499个

STM#(1500—2),BRC

RPTBZBEND一1

SUB*AR6+,A

ADD*AR5+,A

STLA,一4,*AR7+

ZBEND:RET

5.3第一级门限判决

将读入的雷达视频信号值以距离单元为单位,逐个与杂波均值估值表中对应距离单元的数值作比较:如果某单元雷达视频信号的数值较其对应的杂波均值估值大,认为此单元为“可能目标”的回波信号,将它放置到数据积累区中(1600H起始)相应的单元,同时也放置到输出数据块中(1000H起始);否则,这两个单元都被清零。程序中用AR3作数据积累区的地址指针,其初值为1600H,由初始化程序设置。程序代码如下:

STM#0408H,AR7;输入数据区首址

STM#oA00H,AR6;均值估值表首址

STM#1000H,AR5;输出数据区首址

STM#(1500—1),BRC:;距离单元总数

RPTBPJlE一1;重复

LD*AR6+,A;取杂波均值估值

STM*AR7,T;取输入的数据

ST#0,*AR3;积累区先清零

ST#O,*AR5;输出区先清零

SUB*AR7+,A;比较

STRCD*AR3+,ALT;数据大,分别放置

STRCD*AR5+,ALT;到积累区和输出区

PJlE:LDAR3,B;调整积累区指针

ADD#100H,B

AND#OFF00H,B

SUB#4000H,B

BCPJlEND,BLT

SUB#2A00H,B

PJIEND:ADD#4000H,B

STMLB,AR3;调整积累区指针结束

RET

5.4第二级门限判决

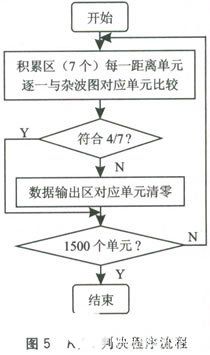

第二门限判决就是在第一门限判决的基础上,滤除那些偶然超过第一门限,但是又是在多次扫描中,孤立的、互不相关的杂波噪声信号,就是对那些“可能目标”的信号作进一步的处理,进一步降低检测目标的虚警概率。根据2.3节的讨论,第二门限值(K/N)的取值为4/7。由于在第一门限判决处理时已经建立了7次扫描的累积数据和初步的输出数据,它们分别位于数据累积区和数据输出区。因此,在程序的具体实现时,就是根据最新的积累数据,对量程范围内的每个距离单元逐个进行K/N判决,符合K/N判决准则的,输出数据区的数值不变,而不符合准则的将该距离单元所在数据输出区的数值清零。由于程序代码较长,用图5所示流程表示。

6结语

本文介绍的基于DSP的雷达视频信号的数字采集和处理系统的设计,作为一种雷达视频信号处理的方法,适用于多种雷达的信号处理,对于不同型号的雷达,由于其用途的不同,其技术参数也不相同。只要选择合适的工作参数,此设计对其他种类雷达的视频信号仍然适用。

-

雷达回波系统的应用研究2016-07-01 3505

-

基于DSP+FPGA的雷达信号模拟器系统设计2019-07-15 2117

-

怎么实现基于DSP的阵列声波信号采集与处理系统的设计?2021-05-31 1228

-

基于FPGA和DSP的光纤信号实时处理系统2009-06-19 927

-

基于高速定点DSP的雷达信号处理实验系统2009-09-04 507

-

导航雷达回波信号的实时采集与回放2009-12-31 1015

-

基于DSP和DSP/BIOS的实时雷达信号采集与处理系统2010-01-16 678

-

基于ADSP-TS101S的多芯片数字信号处理系统的实现方案2006-03-11 1308

-

基于DSP的图象采集与处理系统的设计2009-04-22 1740

-

基于FPGA的雷达信号处理系统设计2015-10-30 1126

-

基于DSP_FPGA的LFMCW雷达测距信号处理系统设计_陈林军2017-03-19 924

-

基于DSP的数字信号采集处理系统设计2017-10-19 1047

-

DSP和USB的高速数据采集与处理系统设计方案2017-11-06 1319

-

基于数字信号处理器实现雷达信号处理系统的设计2020-12-31 3454

-

基于DSP芯片TMS320VC5402实现雷达回波信号采集和处理系统的设计2021-01-20 2929

全部0条评论

快来发表一下你的评论吧 !