原边方案FB引脚电阻如何计算,一个案例带你了解

原边方案FB引脚电阻如何计算,一个案例带你了解

描述

很多新入门的工程师对副边方案电压的计算很清楚,但是对原边方案电压计算的了解微乎其微。在原边方案中,已知输出电压、变压器次级及VCC匝比的情况下,如何计算所需要的FB引脚电阻?本文将为你揭晓。

以启臣微CR624X计算为列

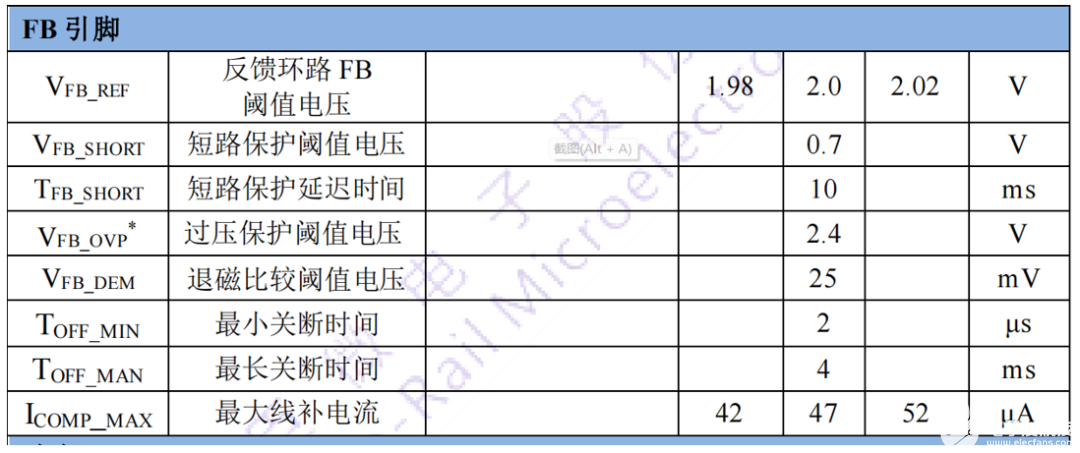

先查看CR624X规格书得知,FB反馈环路阀值电压为2.0V。

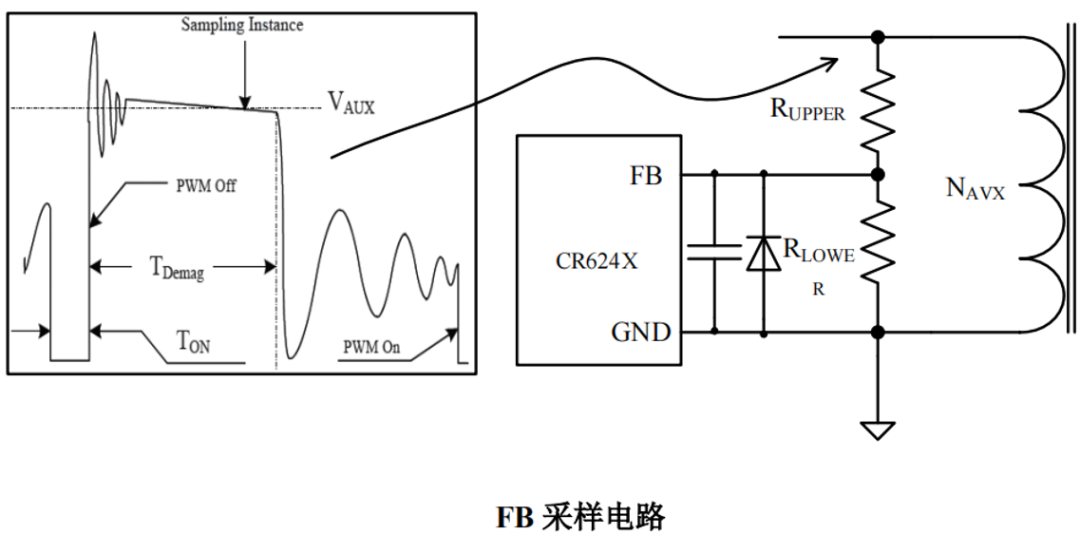

FB采样电路如图:

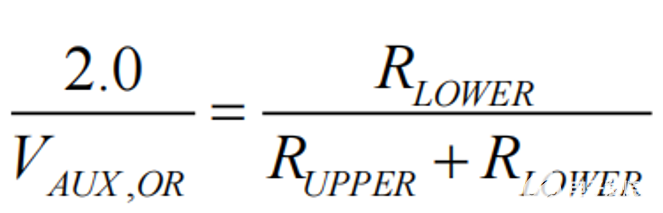

CR624X 通过电阻RUPPER和 RLOWER分压器采样辅助绕组去磁时间 2/3 处的电压,并保持到下一个采样周期。采样电压被送到 FB 脚与基准电压 2.0V 比较,误差被放大,误差放大器的输出脚电压反映了负载情况,通过控制 PWM 频率来调节输出电压,达到恒压目的。

当采样电压低于2.5V 最大时,开关频率被采样电压控制,通过输出电压去控制输出电流,达到恒流目的。

为了达到良好的负载调整率,CR624X 内部集成了线损补偿功能。

FB 端的采样电压由两部分组成:

1、输出电压通过变压器绕组反馈到 FB 端的电压;

2、芯片内部线损补偿电流流过分压电阻所产生的电压,这个电流与开关管关断时间成正比,与负载电流成反比,所以使得由于输出负载电流变化而导致的输出电压变化能够得到有效补偿。

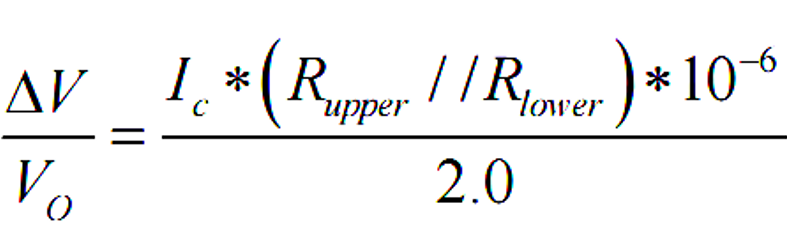

最大补偿百分比为:

其中,ΔV为负载补偿电压,“Vo”为输出电压,IC 典型值为 45uA。

注意:

1)RUPPER 和 RLOWER 采用精度为 1%的标准电阻。

2)FB 脚到 IC 的 GND 最好加一个几十 pF的电容(一定要控制在 100pF 内),该电容作用在于平滑 FB 端采样电压平台波形,使采样电压更精确,以增加输出稳定性,且该电容靠近 FB端为宜。

3)若辅助绕组端负压过大,建议在FB脚对地加 1N4148,箝制MOS 导通时FB 脚上的负压,以减小此负压对芯片内部电路损伤的风险。

关于思睿达微电子

思睿达是专注于ADC、DAC、PoE和DC / DC 芯片级解决方案的高科技企业,目前同步推广启臣微全系列产品,希望将启臣15年在电源行业这份积淀,这份坚持发扬光大。思睿达同时也可以提供芯片级定制服务。

审核编辑:符乾江

-

如何优化DC/DC变换器中FB分压电阻的FB布线2023-08-17 3177

-

什么是FB功能块?为什么要使用FB功能块?如何制作一个FB功能块?2023-11-09 7408

-

求助,关于ada4817 fb引脚使用疑问求解2024-12-19 3509

-

工程师必知|原边方案中FB引脚电阻如何计算?一个案例带你了解 #产品方案 #芯片思睿达小妹妹 2022-04-03

-

BP3319MB LED驱动方案设计 原边反馈单级有源PFC2016-02-16 7626

-

BP3318外置驱动原边反馈方案2016-05-06 10080

-

请问TPS61500空载时候FB引脚的电压是多少?2019-06-28 2807

-

一篇文章带你了解原型制作化技术2021-04-26 2464

-

L4960开关稳压器是否有一个公式可以计算连接到引脚5的开关频率2022-12-01 727

-

十个问题带你了解和掌握java HashMap2018-03-12 844

-

一文带你了解PLC中FB和FC块的区别2018-04-18 40485

-

通过一个案例教你玩转MCU代码生成工具(基于STM32)2021-11-18 900

-

带你深入了解示波器2022-02-07 1098

-

物联网是什么,一文带你了解物联网2022-03-23 5401

-

带你了解电阻封装2024-05-15 5309

全部0条评论

快来发表一下你的评论吧 !