Verilog实现计数器在某个区间内循环计数,递增递减

Verilog实现计数器在某个区间内循环计数,递增递减

电子说

1.4w人已加入

描述

有时候在复杂系统设计的时候会用遇到让“计数器在某个区间内来回不停递增递减”的问题。

话不多说,我们直接上代码。

以0-10的循环计数为例。

工具:Modelsim, VScode

1.准备工作

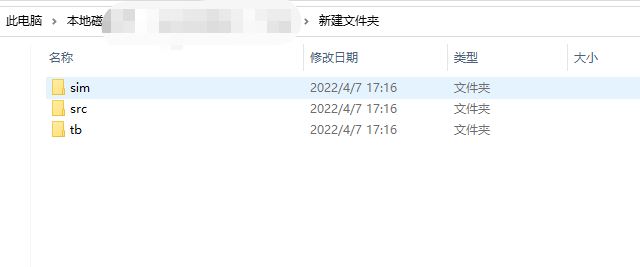

首先在电脑上新建三个文件夹,SRC、TB以及SIM,用来放置源代码、仿真文件以及仿真工程文件。

一定不要怕麻烦,特别是新手一定要注意代码的分类工作!良好的分类能够大大的提高工作效率。

刚接触代码量小,几十行代码一个文件就搞定了。但是随着从业时间的增加,工作复杂度的提升,代码的难度也会随之提升,如果不做好分类管理,面对几十个源代码,十几个仿真文件……崩溃是必然的。

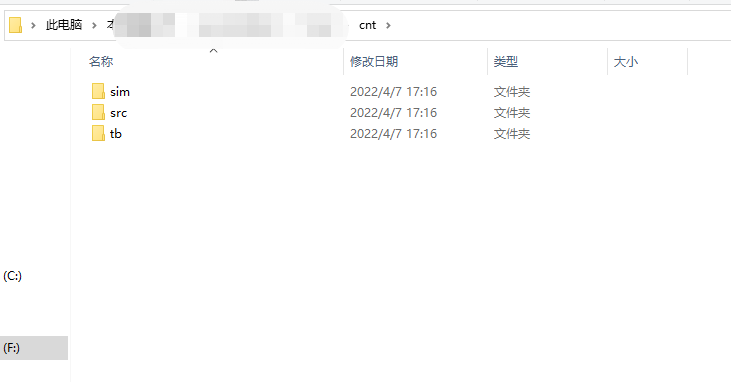

请注意:一定不能有中文路径!!

这样是错误的

这样是错误的

应该这样修改

应该这样修改2.工程建立

- 在src文件中添加一个.v文件,名字自拟,最好能够体现出文件的特性。

module test (

input sys_clk,

input rst_n,

);

reg flag;

reg [7:0] adc_data;

always @(posedge sys_clk or negedge rst_n) begin

if (~rst_n)

flag <= 1'd0;

else

case (flag)

1'd0:

if (adc_data == 8'd9) // -1

flag <= 1'd1;

else

flag <= 1'd0;

1'd1:

if (adc_data == 8'd1) // +1

flag <= 1'd0;

else

flag <= 1'd1;

default: flag <= flag;

endcase

end

always @(posedge sys_clk or negedge rst_n) begin

if (~rst_n) begin

adc_data <= 8'd0;

end

else if (flag == 1'd0)

adc_data <= adc_data + 8'd1;

else if (flag == 1'd1)

adc_data <= adc_data - 8'd1;

else

adc_data <= adc_data;

end

endmodule

- 在tb文件夹中新建文件,给出仿真所需要的激励。我们此次所需的只有时钟和复位。时钟设置为50Mhz,复位1000ns。

`timescale 1 ns /1 ps

module tb_test;

reg sys_clk;

reg rst_n;

test u_tb_test(

.sys_clk (sys_clk),

.rst_n (rst_n)

);

initial begin

sys_clk = 0;

rst_n = 0;

#1000;

rst_n = 1;

#20000;

end

always #10 sys_clk = ~ sys_clk;

endmodule

- 在sim文件夹中新建一个Modelsim仿真工程,添加src,tb中的文件,此过程不再展示。

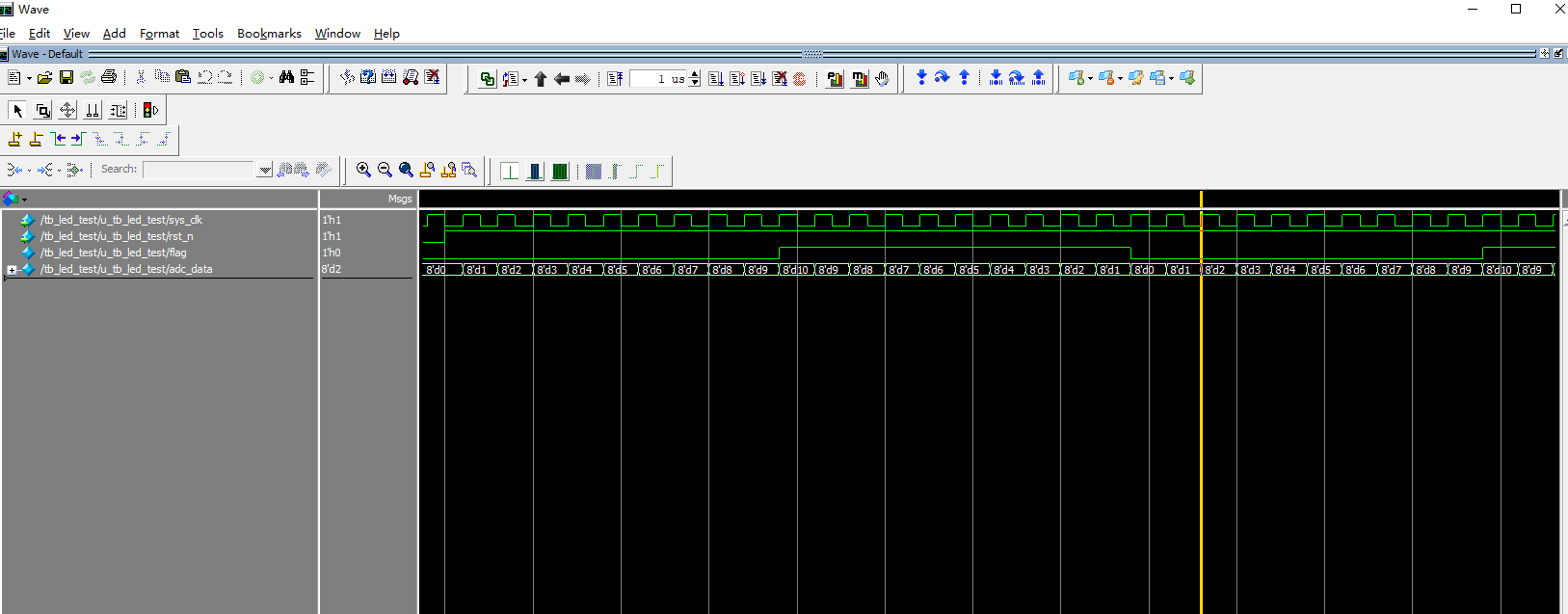

3.仿真验证

仿真1us,观察波形。实现了0-10直接的循环计数,设计成功。

审核编辑:符乾江

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

SN74HC193-Q1 4位同步递增/递减计数器数据表2024-06-04 618

-

8位同步二进制递减计数器-74HC401032023-03-03 1203

-

SCL语言之加计数-计数器函数S_CU2023-01-03 2993

-

使用分配参数并加计数指令递增计数器值2022-08-03 2676

-

双BCD递增计数器CD74HC4520数据手册2022-07-10 935

-

计数器函数S_CU的操作步骤2020-09-03 10565

-

MOD计数器和时序图2019-06-23 17032

-

一个连环无敌面试题--计数器2018-05-16 6995

-

集成计数器实现N进制计数2016-06-08 1367

-

基于可编程计数器74LS161的循环码计数器设计2012-02-29 4768

-

30秒递减计数器电路2011-07-01 2689

-

环形计数器和扭环形计数器2010-01-12 10406

-

8421码同步十进制递增计数器2009-09-24 7013

-

格雷码计数器的Verilog描述2009-08-03 804

全部0条评论

快来发表一下你的评论吧 !