详解提升MOS管驱动电路抗干扰性能的方法

详解提升MOS管驱动电路抗干扰性能的方法

描述

一.前言

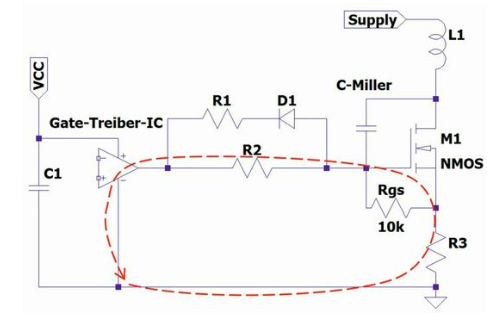

不管什么电路,抗干扰能力都是它的一个重要指标,对于MOS管驱动电路更是如此。因为MOS管不是工作在一个理想的没有任何电磁干扰的环境,在一些电磁环境恶劣的条件下,如果我们的驱动电路设计的不尽合理,可能会出现MOS管误打开或者非受控关断,轻则影响性能,重则会对用户造成伤害。对于MOS管驱动电路而言,这种情况的发生一般是由于gate-source寄生米勒电容的非正常充放电导致的,而影响因素主要是gate极等效串联电阻,寄生电感,寄生电容等因素,所以我们主要针对这三方面进行针对性电路设计来提升电路的抗干扰能力。

二.提升抗干扰的针对措施

1.栅极串联电阻降低源极寄生电感导致的振荡

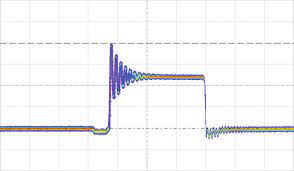

我们在实际调试MOS管驱动电路时,如果大家用示波器测一下MOS管gate极的波形,就会发现MOS管每次打开时,其栅极波形会出现类似于正弦波的阻尼振荡,这不仅使得MOS开关不稳定,降低其抗干扰能力,也会增大开关损耗,那么为什么会出现?如何解决呢?

MOS开/关振荡

MOS开/关振荡

实际的MOS模型大家可以参考下图,理想的MOS没有Rgt,Lgt,以及Cgs等,但是现实的MOS这些都有,此时你会发现,Rgt+Lgt+Cgs那不就成了典型的RLC振荡电路么,没错就是这样,所以当我们给高电平想开启MOS的时候,就会出现振铃波,同样我们给低电平想关闭MOS时也是一样,都是电容电感的充放电在作妖。

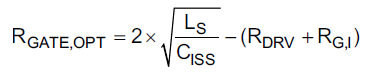

理解了原因,那么如何解决这一问题呢?解决问题的关键就是Rgt电阻,因为对于RLC振荡电路而言,Rgt是耗能器件,每一次振荡,它都会消耗能量,从而减弱下一次的振荡幅值,这也是实际的波形峰值越来越低的原因,当然Rgt是MOS内部的寄生电阻,其阻值很小,所以我们一般需要外部在串联一个电阻,串联电阻的阻值计算公式如下,其中Rdv是外部PCB网络走线寄生电阻,电阻大了能缓解电压过冲的问题,但是也不是越大越好,因为太大了又会导致MOS开启速度过慢,所以需要综合考虑。

2.栅源并联电阻提升抗dv/dt干扰能力

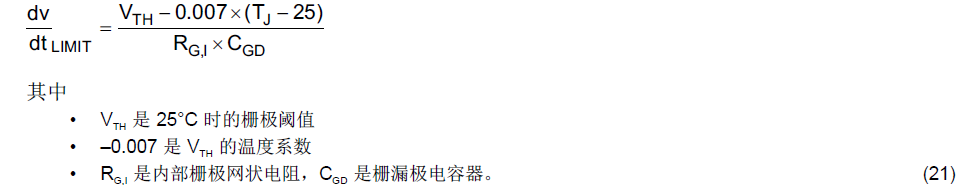

当dv/dt过大时,可以会使得MOS误打开,这是由于流过Cgd电容的电流在G极形成正压,从而引起MOS误打开,通常通过在器件的栅极和源极端子间加入一个电阻器来提供保护,电阻的计算公式参考下面,根据公式可以看出来,要想计算我们需要多大的并联电阻,还需要清楚我们的电路最差的dv/dt是多少,这个就需要实际测试了。

三.总结

今天我们主要讲解了提升MOS管驱动电路抗干扰能力的方法以及计算方式,欢迎关注,有疑问可以留言哦。

-

OPA1622易受机内WIFI干扰,如何提升抗干扰性?2024-10-25 679

-

解决数字电路抗干扰的方法2011-02-12 6970

-

幅相误差对卫星导航抗干扰性能影响2012-08-06 2317

-

提高敏感器件的抗干扰性能 的常用措施2015-05-07 3512

-

如何提高敏感器件的抗干扰性能2021-02-19 1887

-

形成干扰的基本要素,提高敏感器件抗干扰性能的常用措施有哪些?2021-03-17 1366

-

形成干扰的基本要素有哪些?如何提高敏感器件的抗干扰性能?2021-04-06 1865

-

具有抗干扰性能的声光控制器电路图2009-06-12 937

-

超宽带通信抗干扰性能分析2017-02-07 800

-

怎么样才能提高敏感器件的抗干扰性能2020-05-05 3648

-

如何实现PCB电路抗干扰性的设计2020-08-04 1622

-

数字信号和光信号的抗干扰性详解2023-09-07 5000

-

A-D量化位数对抗干扰性能影响2023-10-23 604

-

如何提高 SG-8200CG 可编程晶振的抗干扰性能?2024-11-19 990

全部0条评论

快来发表一下你的评论吧 !