所谓的芯片堆叠技术究竟是什么?

描述

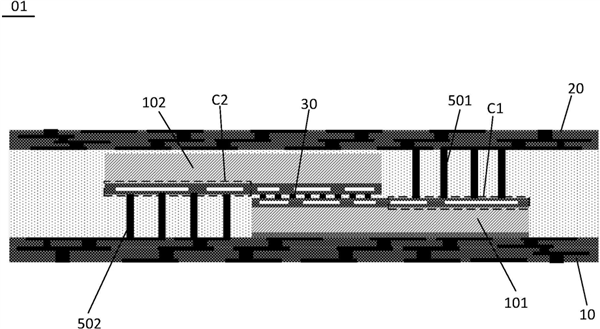

近日,国家知识产权局官网公开的信息显示,华为技术有限公司公开了“一种芯片堆叠封装及终端设备”专利。

据摘要显示,本公开涉及半导体技术领域,其能够在保证供电需求的同时,解决因采用硅通孔技术而导致的成本高的问题。

所谓的芯片堆叠技术,究竟是什么?

“芯片堆叠”这个词最近经常听到,在前段时间苹果举行线上发布会时推出了号称“史上最强”的 Apple M1 ultra,就是一种采用堆叠思路设计的芯片。

M1 ultra 将两枚 M1 Max 中隐藏的芯片间互连模块(die-to-die connector)通过技术手段整合在一起,苹果将其称之为“Ultra Fusion”架构,拥有 1 万多个信号点,互连带宽高达 2.5TB/s,而且延迟、功耗都非常低。

通过这种方式组合而成的 M1 Ultra,规格基本上是 M1 Max 的翻倍。同样是采用了 5nm 制造工艺,但 M1 Ultra 的晶体管数量却高达 1140 亿个,统一内存最高达到 128GB,总带宽 800GB/s。

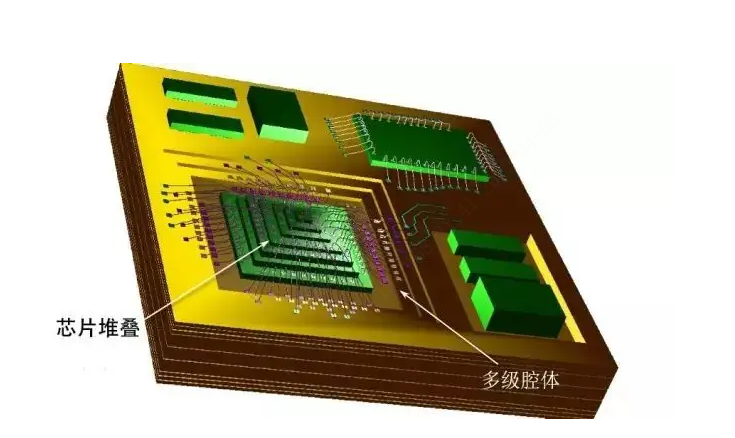

据了解,堆叠技术也可以叫做 3D 堆叠技术,是利用堆叠技术或通过互连和其他微加工技术在芯片或结构的 Z 轴方向上形成三维集成,信号连接以及晶圆级,芯片级和硅盖封装具有不同的功能,针对包装和可靠性技术的三维堆叠处理技术。

该技术用于微系统集成,是在片上系统(SOC)和多芯片模块(MCM)之后开发的先进的系统级封装制造技术。

在传统的 SiP 封装系统中,任何芯片堆栈都可以称为 3D,因为在 Z 轴上功能和信号都有扩展,无论堆栈位于 IC 内部还是外部。

目前,3D 芯片技术的类别包括:基于芯片堆叠的 3D 技术,基于有源 TSV 的 3D 技术,基于无源 TSV 的 3D 技术,以及基于芯片制造的 3D 技术。

值得一提的是,去年华为就曾被曝出“双芯叠加”专利,这种方式可以让 14nm 芯片经过优化后比肩 7nm 性能。但当时曝光的这种通过堆叠的方式与苹果的“Ultra Fusion”架构还是有所不同。

也许有很多人理解双芯片堆叠是指将两颗独立芯片进行物理堆叠的方式去实现性能突破,其实这是非常严重的错误,如果单单依靠物理堆叠,那么会有非常多的弊端无法解决。

例如兼容性,稳定性,发热控制这些都是没法通过物理堆叠来解决问题的,在设计思路上面就会走上歧路,得不偿失也毫无意义。

双芯叠加层级运用于设计和生产初期,也就是说在设计过程中将原来的一颗芯片设计成双层芯片然后利用自己独特的技术,来将这两层芯片封装在一颗芯片中,通过同步信号方式与一些其他方法就可以激活双层芯片共同发力,从而实现芯片性能突破。

所以说一个物理层堆叠,一个设计之初就开始改变设计思路,这是完全不同的两个方式。

因此,虽然同样是指双芯片组合成单个主芯片,但苹果与华为可以说是两种截然不同的方式。无论如何,双芯片组合带来的结果必然是 1+1>1,但不一定等于 2。

当然,无论是华为的双芯叠加技术还是苹果的 Ultra Fusion 架构,在当前芯片工艺水平发展接近极限的情况下,“双芯堆叠”设计的方式不失为一种好的选择。

从理论上来说,两颗芯片可以将任务分工处理,形成更强的运行效率,而其中重点所需要解决的,无非就是功耗、信号同步、数据流协同处理等方面的问题。

在前不久举办的华为 2021 年业绩发布会上,华为轮值董事长郭平表态称,未来华为可能会采用多核结构的芯片设计方案,以提升性能。

同时,采用面积换性能,用堆叠换性能,使得不那么先进的工艺也能持续让华为在未来的产品里面,能够具有竞争力。

在去年 12 月,华为公司还投资 6 亿元成立了一家电子制造的全资子——华为精密制造有限公司,经营范围为光通信设备制造,光电子器件制造,电子元器件制造和半导体分立器件制造。

当时就有内部人士称,该公司具备一定规模的量产和小批量试制(能力),但主要用于满足自有产品的系统集成需求。

“不生产芯片,主要是部分核心器件、模组、部件的精密制造。”同时,经营范围中提及的“半导体分立器件”主要是分立器件的封装、测试。如此来看,华为对于芯片堆叠路线早有清晰的规划,或许已经投入制造环节。

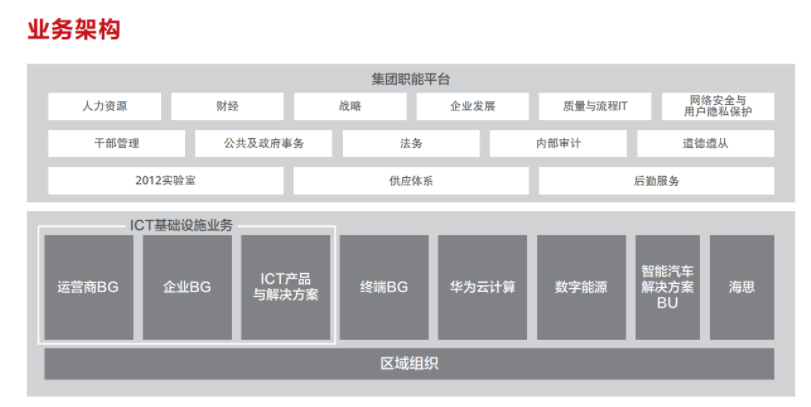

此外,从华为将海思列为了一级部门的重大业务架构调整来看,这预示着其战略重心的重新配置。

在过去相当长的一段时间里,海思只是华为 2012 实验室下面的一个部门,最高端的产品也都是自用。

现在,华为将海思列为一级业务部门,在很大程度上预示着,未来华为的芯片产品,将从“部分商用”调整为“全面商用”,华为也将继续加大在芯片领域的人才投入和技术投入。

审核编辑 :李倩

-

串口究竟是什么呢?2023-04-12 24009

-

增量式编码器倍频技术的M法究竟是怎样测速的2021-11-09 8945

-

retain,copy与assign究竟是有什么区别呢2021-09-30 1648

-

无片外电容LDO究竟是什么?2021-06-22 3351

-

spec究竟是什么?有谁可以分享一下吗2021-06-21 2384

-

一文读懂eMMC究竟是啥?2021-06-18 4028

-

分贝究竟是什么?如何去理解它?2021-05-31 2287

-

真正软件定义无线电究竟是怎样的?2021-05-14 1729

-

电感饱和究竟是什么2021-03-11 2913

-

我们仿真DDR究竟是仿真什么2021-03-04 2377

-

S参数究竟是什么?2021-03-01 2778

-

图解:IGBT究竟是什么?2020-08-10 2741

-

FSMC和LCD的控制究竟是什么关系?2020-05-14 3091

全部0条评论

快来发表一下你的评论吧 !