IIC总线协议介绍

描述

总线信号 :

SDA :串行数据线

SCL :串行时钟

总线空闲状态 :

SDA :高电平

SCL :高电平

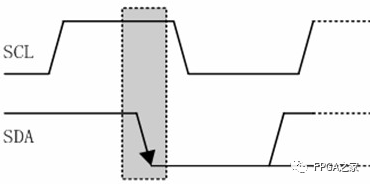

起始位:SCL为高电平期间 SDA出现下降沿

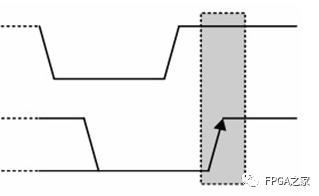

终止位:SCL为高电平期间 SDA出现上升沿

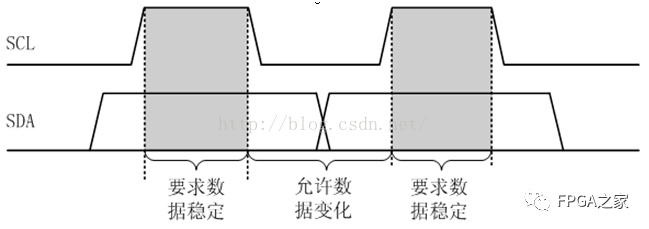

数据传输 :SDA的数据在SCL高电平期间被写入从机。所以SDA的数据变化要发生在SCL低电平期间。

IIC时钟频率:不高于400K

应答:当IIC主机(不一定是发送端还是接受端)将8位数据或命令传出后,会将SDA信号设置为输入,等待从机应答(等待SDA由高电平拉为低电平)

若从机正确应答,表明数据或者命令传输成功,否则传输失败,注意,应答信号是数据接收方发送给数据发送方的。

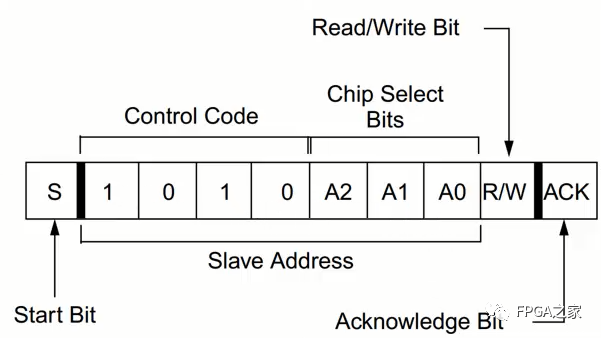

IIC器件地址:每一个IIC器件都有一个器件地址,有的器件地址在出厂时地址就设定好了,用户不可以更改,比如OV7670的

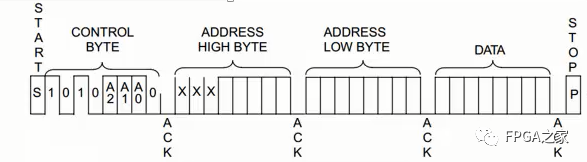

地址为0x42。有的器件例如EEPROM,前四个地址已经确定为1010,后三个地址是由硬件链接确定的,所以一

个IIC总线最多能连8个EEPROM芯片。

图上开始信号之后,七位地址代表器件地址,第八位代表读或者写,0为写,1代表读,然后跟着响应位。

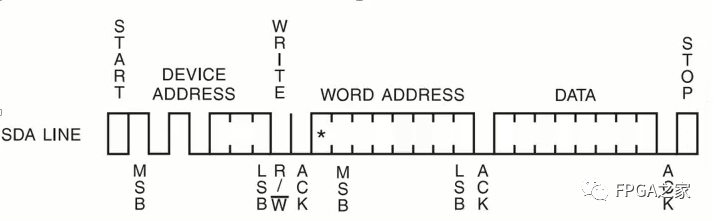

IIC器件单字节写时序:

IIC器件多字节地址写时序:多字节地址比单字节地址在时序上就多了一块写地址

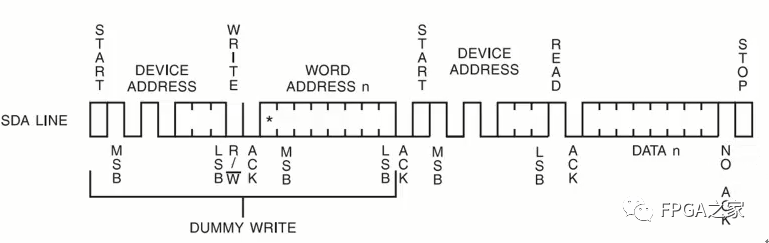

单字节器件读时序:注意最后产生无应答信号,另外多字节地址读时序跟单字节类似,只不过是多了几个地址字节而已。

三大串行总线:uart、spi、iic

同步 :spi 异步 : iic,uart

同步和异步区别:采集数据是否用的是时钟的沿,如果是时钟沿采数据,同步传输,如果电平采集数据是异步

串口接受数据其实就是一个串转并的过程

原文标题:IIC协议

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

IIC总线协议时序介绍 IIC总线程序设计2023-07-23 29274

-

介绍IIC总线仲裁电子电器 2023-02-07

-

IIC总线协议的相关资料下载2021-11-30 1300

-

IIC总线协议及应用2021-11-20 895

-

基于FPGA来介绍并设计标准的SPI总线协议2021-11-10 1144

-

IIC协议总线特点简介2021-08-20 1269

-

IIC总线介绍2021-08-18 1585

-

一文解读IIC总线的FPGA实现原理及过程2018-05-31 7331

-

IIC总线协议中文版2016-08-09 1544

-

IIC总线协议与SCCB协议的区别2016-08-07 11183

-

IIC总线协议2016-07-26 1214

-

LESSON8_IIC总线协议2016-06-17 1069

-

LESSON8_IIC总线工作原理2016-02-18 855

-

iic总线的详细说明2015-11-16 1172

全部0条评论

快来发表一下你的评论吧 !