在RTL设计中如何做到低功耗设计

描述

做芯片第一应该关注的是芯片的PPA(Performance, Power, Area),本篇浅显的部分讨论,第二个 P,Power功耗,在RTL设计中如何做到低功耗设计,对于移动设备续航的十分重要,不要让你的芯片徒增功耗。

数据通路寄存器打拍

数据寄存器打拍带上vld,不加复位逻辑,这样会省去寄存器复位电路的布线面积,而且工具还会给寄存器自动插时钟门控,还达到了降低功耗的效果。至于寄存器不复位,一些刚学习的朋友可能会感觉有些刷新认知,寄存器怎么能不复位,不复位不就是x态了,系统不就紊乱了。是的,寄存器不复位是会产生x态,不过这里说的是数据通路,控制通路的所有信号都是必须带复位逻辑。数据通路因为这里是带着vld进行打拍,只需要保证在你使用的时候,它不是x态就行了。控制通路的信号控制系统的运行,出现x态,必然挂死。而数据通路只要保证在vld的有效,也就是我踩这个数据的时候它是正确的就行了,不管它是x态还是其他无效的数据。当然如果数据有作为判断逻辑用于控制,那这个数据一定要进行复位。代码示例,时序逻辑可以省略else,寄存器默认保持,组合逻辑必须写else。vld是一个脉冲将这个数据踹一脚直接踹进这个寄存器存储,在下一脚来临之前,这个寄存器都将保持这个数据。always @(posedge clk)begin if(data_vld) dout[63:0] <= din;end

手动插入时钟门控

手动插入时钟门控,根据控制场景的不同自动关掉部分模块的时钟,留有软件的控制通道,由软件关闭。可以有效的减少动态功耗。举例,比如一块运算电路配置全开的时候需要四个相同的计算模块同时工作,最少的情况只需要一个模块工作,这时根据配置的不同可以将其他三个模块的时钟关掉,减少动态功耗。整个Top模块掉电

整个二级Top模块掉电休眠,掉电后将所有需要保存的数据写到memory中,等下一次模块唤醒上电启动时再重新写回到硬件中。ASIC中的RAM可以自己生成是否需要掉电保存数据的功能,不需要的专门存储的RAM也一起掉电。需要使用和保存的数据寄存器较少,可以从模块伸出接口到顶层,让软件读走,等下一次模块唤醒上电启动时再通过软件配置寄存器配置回模块。这就是低功耗模式。静态功耗和动态功耗

静态功耗只要电路供电就有,除非掉电休眠,否则无法避免,动态功耗只要存在高低电平切换就有。在rtl设计时,良好的代码风格也可以降低动态功耗,乘法器、加法器等运算单元,通过减少组合逻辑的翻转,从而达到降低动态功耗的效果。

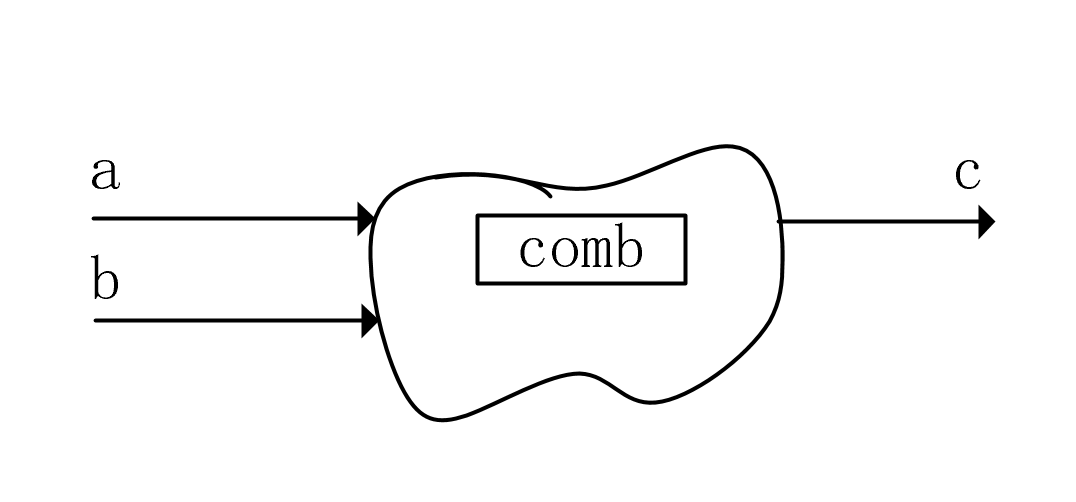

输入到输出,组合逻辑的a、b端值不变,没有电平翻转,所以不会有动态功耗,只存在静态功耗。在设计中考虑组合逻辑无效翻转问题,某段时间这部分数据无效,通过使能信号选择这部分逻辑保持,得到避免动态功耗的效果。

原文标题:Verilog如何实现低功耗设计?

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

MCU芯片想实现低功耗如何做到?2025-12-01 122

-

MATLAB中如何做到去列平均值2018-04-02 4281

-

如何做到进入低功耗PM2模式和定时器中断唤醒交替循环?2019-10-15 1715

-

新手求助UPF低功耗设计能否在RTL仿真中实现呢?2021-06-18 2359

-

请问STM8L低功耗如何做串口接收2s一次的数据?2023-11-06 548

-

Bus/总线布线时如何做到等长2009-09-28 1909

-

RTL功耗优化2017-09-11 1056

-

最美布线, 别人是如何做到的2020-02-28 3072

-

芯片RTL设计中如何做到低功耗设计2021-08-26 4885

-

RTL设计中如何做到低功耗设计2022-08-15 2046

-

UWB技术是如何做到室内精准定位的?2022-10-18 1472

-

低功耗蓝牙模块的工作原理是怎样的2022-12-26 2493

-

RF模组sleep状态下如何做到最低功耗?2024-01-06 1285

-

工程行业中如何做到低碳甚至零碳2024-10-14 1576

-

RTL8762CMF/RTL8752CMF:蓝牙低功耗SOC的卓越之选2026-04-11 655

全部0条评论

快来发表一下你的评论吧 !