FPGA知识汇集-ASIC向FPGA的移植

电子说

描述

ASIC原型验证是整个验证环节中非常重要的步骤之一,也是将ASIC的代码移植到FPGA平台上最重要的原因,本文章的意义在于:

对于系统构架师,将帮助他们在选择商用模拟器还是自行设计方案之间做出更好的选择;

对于逻辑工程师,他们能够更好的将ASIC设计移植到FPGA原型验证平台中;

对于验证工程师,其价值在于如何将现有的测试平台移植到新的验证环境中。

将ASIC设计移植到FPGA芯片中,对于大部分设计团队来讲都是巨大的挑战。主要体现在:ASIC的设计一般都非常大,往往需要做多FPGA芯片划分;需要支持足够的处理性能;需要保证其功能的正确性;需要保证移植前后的功能具有等价性。

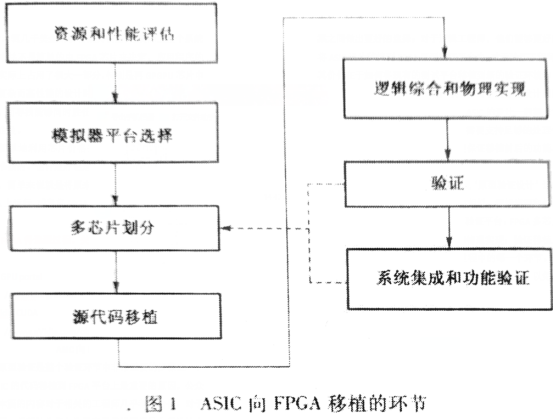

当时ASIC设计的移植还没有出现‘原型验证设计’这样的方法学,但是整个移植的任务大致相似:逻辑资源和处理性能评估:选择硬件模拟器或者原型验证平台;FPGA多芯片划分;RTL源代码修改;逻辑综合和物理实现;验证移植后的整个设计。图1说明了整个验证过程中的每一个环节。

移植过程的总体原则是尽量少地修改原始设计,以免产生新的问题。

资源评估

从任何一个角度来看,精确的资源评估都是ASIC移植工作的重点。首先它的结果将直接影响到硬件模拟器或者原型验证平台的选型,其次对于整个设计的多芯片划分和成本都有直接的影响。资源估计过少,那么ASIC设计就不能完整的移植到FPGA中;而资源估计过多,则会导致毫无必要的成本开销。

对于ASIC资源评估的不同方法。

性能评估

性能评估的结果,会直接影响验证方案的选择,对于大部分的设计来说,不可能期望ASIC设计在FPGA平台上拥有相同的性能指标。除了FPGA内核本身带来的性能降低之外,芯片与芯片之间的通信延迟也降低了整体的性能。如果一个平台的性能指标能够达到ASIC设计的几分之一,那么这个方案就具有了可行性。但是如果只有原始性能的几十分之一,很多验证任务就无法完成。

在多核处理器的SOC芯片中,某些嵌入式操作系统的启动时间甚至会高达5分钟左右。如果验证平台的性能只有十分之一,那么就要耗费接近1小时,某些程度上还能接受。但是如果性能只有一百分之一,那么基本上要耗费半天来启动这个操作系统。对于绝大部分的嵌入式系统的验证来讲,该方案将变的毫无可行性。

关于性能评估的内容。

硬件模拟器与原型验证平台

选择硬件模拟器还是原型验证平台,对于验证团队来讲一直都是长期而艰巨的任务。最终的选择需要满足所有的需求,例如资源容量、整体性能、系统成本、验证范围及能够支持的工具等

FPGA多芯片划分

ASIC设计所占用的资源一般非常大,常常需要划分到多颗FPGA芯片中才能实现。简单来说就是将ASIC设计的不同部分(一般是以功能模块为划分边界)映射到不同的FPGA芯片中。划分及优化的过程较为复杂,需要考虑到整个方案的系统成本、整体性能、资源容量、FPGA芯片之间如何互联、划分的复杂度等指标。

源代码移植

虽然ASIC和FPGA都是使用相同的RTL编码方式,但是将适合ASIC芯片的RTL源代码移植到FPGA芯片中时,需要进行相当多的重编码和优化工作。特别是ASIC设计中的时钟树结构,需要正确的分配到FPGA芯片的各种时钟资源上,这将是一项非常大的挑战。

同时,ASIC设计中的某些资源,例如晶体管、传输门、双向信号甚至是模拟电路,在FPGA芯片内根本无法找到对应的结构,因此需要找到其他方式进行模拟(替代)。

几乎所有的ASIC设计都会使用到各式各样的IP核:从Synopsys Design Ware库中的简单功能模块(大部分模块都可以使用FPGA结构实现)复到复杂的存储器控制器,PCIE,USB等总线子系统,以及CPU内核等。像Xilinx这样的FPGA供应商能够提供许多可替代的对应IP核,但并不是所有都可替代。

关于时钟、锁存器、存储器、三态门、组合逻辑及不可综合电路的移植。

逻辑综合和物理实现

完成了代码移植后,剩下的工作主要就是逻辑综合和物理实现。其中包括解决由于ASIC和FPGA综合工具的差异引起额问题,添加时序、资源、引脚约束、优化工具的参数设置,最终达到时序收敛。

虽然最新的FPGA工具和设计流程和ASIC很相似,但是一些根本性的差异所造成的问题还是需要工程师解决。通常,ASIC综合工具所支持的Verilog语法要比FPGA综合工具更加宽松,而且由于设计优化的目标不同,ASIC和FPGA综合工具所支持的引导语句和工具选项也不尽相同。另外,无论是资源占用还是布线密度,ASIC工具需要处理的工作远远比FPGA复杂的多。在某些复杂的情况下,FPGA工具甚至会无法布局布线。因此某些情况下必须要修改RTL源代码,甚至是重新规划多芯片划分方案。

验证移植后的设计

验证移植后的代码是整个过程的最终环节,其目标就是保证移植前后的设计在功能上保持一致,并且符合原始的设计规范。验证的方法有基于软件的功能仿真,基于硬件的模拟器或者原型验证平台,以及基于纯数字推导的等价性验证。

系统集成和功能验证

ASIC流片之后,需要进行系统集成和功能测试,其主要目的就是保证芯片的功能在整个系统中能够正确的运行。首先芯片被安置于特殊设计的PCB上,测试程序负责向芯片注入激励向量,芯片的输出和预期结果进行比较,以判断其功能是否正确。整个硅片的测试基本都是自动化的测试过程,并且通常会在不同的条件下同时测试硅片。激励向量的产生有多种方式:预先定义的激励向量,使用多输入移位寄存器产生随机序列等。当其中某项测试失败时,可以通过硬件模拟器进行相同的测试来定位问题的根本原因。

审核编辑 :李倩

-

FPGA与ASIC的区别 FPGA性能优化技巧2024-12-02 2214

-

FPGA和ASIC的区别与联系2023-08-14 4798

-

什么是FPGA原型验证?如何用FPGA对ASIC进行原型验证2023-04-10 2860

-

FPGA、ASIC技术对比2023-03-31 2822

-

FPGA vs ASIC2022-11-28 2837

-

FPGA_ASIC-MAC在FPGA中的高效实现2021-08-04 911

-

FPGA_ASIC-DSP和FPGA共用FLASH进行配置的方法2021-07-30 1148

-

探析FPGA和ASIC的原理和区别2018-12-15 6458

-

如何设计利用PMBus电源向ASIC、FPGA及DDR电压轨供电?2018-08-06 5558

-

ASIC和FPGA设计优势和流程比较2017-11-25 4947

-

cogoask讲解fpga和ASIC是什么意思2012-02-27 2534

-

ASIC和FPGA的优势与劣势2011-03-31 6056

-

ASIC设计转FPGA时的注意事项2010-09-10 1273

-

fpga是什么意思 ASIC是什么意思2007-12-20 5717

全部0条评论

快来发表一下你的评论吧 !