浅谈SoC引起的封装和PCB问题

描述

在这里,我们通过研究影响 SoC 开发成功的封装和 PCB 问题,开始认真扩展芯片设计团队的领域。

包装注意事项

电容耦合是 SoC 设计中众所周知的问题领域,可以在芯片级处理,但仅此已不够,因为它也体现在封装中。还可以观察到信号走线之间的耦合——无论两者是否都处于活动状态——甚至可以来自电源总线。

射频、模拟和数字电路的不同电压和电流水平是罪魁祸首。一个经常观察到的问题是模拟/RF 电路成为数字模块的 EMI 源,导致在低频和高频处与频率求和和谐波发生互调。在模拟/RF 和数字模块之间共享封装接地层和电源层会使模拟电路暴露于数字开关噪声、主要电流尖峰以及通过实施不佳的返回路径耦合。将模拟和数字接地引脚连接在一起同样危险,因为它有可能形成一个既会吸引又会产生噪声的环形天线。

并非所有这些困难的补救措施都需要异乎寻常的方法。过去的合理设计实践仍然可以很好地工作,例如通过简单地记住保持源和返回路径物理上接近来避免电流环路。但是封装工程师必须非常有创意地寻找其他 SoC 引起的问题的解决方案。

除了提供嵌入式去耦电容器外,一些封装还包括原生电感器作为去耦组件以节省空间。

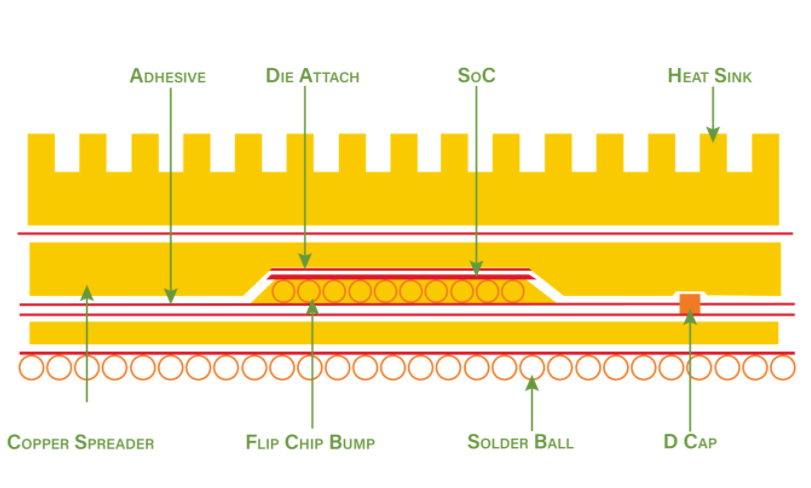

图 1显示横截面倒装芯片 BGA 封装的示意图。资料来源:P2F 半

然而,当今封装领域最前沿的工作是多芯片车辆的日益普及:系统级封装 (SiP)、晶圆级集成,尤其是 2.5D/3D IC。无需将所有功能集成在单个芯片上,裸片可以专门用作模拟、数字或内存模块,然后与硅通孔 (TSV) 堆叠,提供金属堆叠和中介层之间的连接,并聚合信号和接地引脚以与封装接口球和PCB。借助针对 TSV 距离和信号/接地分布的适当设计规则,2.5/3D IC 在解决超深亚微米 SoC 的许多信号完整性 (SI) 和电源完整性 (PI) 问题方面大有帮助。

2.5/3D IC 仍然只占整个半导体市场的一小部分,大概是 2% 到 3%。然而,这是一个正在蓬勃发展的细分市场,在未来五到六年内规模可能会增加两倍。尽管如此,多芯片方法显然并不适合所有芯片,因为工程工作量、测试负担以及整体设计和制造成本对于半导体市场的高单位体积部分来说仍然令人生畏。这项技术仍在积极发展中,还不能被认为是成熟的。

PCB问题

SoC 引起的封装和 PCB 问题之间有许多相似之处。但是,尽管芯片和电路板之间的物理距离以及与芯片或其封装相比电路板的尺寸要大得多,但问题集在某些方面却相当糟糕。

PCB 中的基本电气问题可能更为明显——介电损耗、耗散因数和集肤效应等。后两者尤其受到数字电路频率上升的不利影响。这些高 F max模块会产生与封装中类似的接地平面调制问题,因为大量电流突降会破坏模拟电路的接地参考。与高频齐头并进,许多千兆位通道中的数据速率也产生了更严重的串扰和符号间干扰 (ISI) 问题。

模拟/射频和数字模块的不同 V dd也会导致两种电路的 EMI 问题——再次与在封装级别观察到的各种问题并行。甚至时钟信号也因其频率和边沿速率而成为 EMI 的来源。

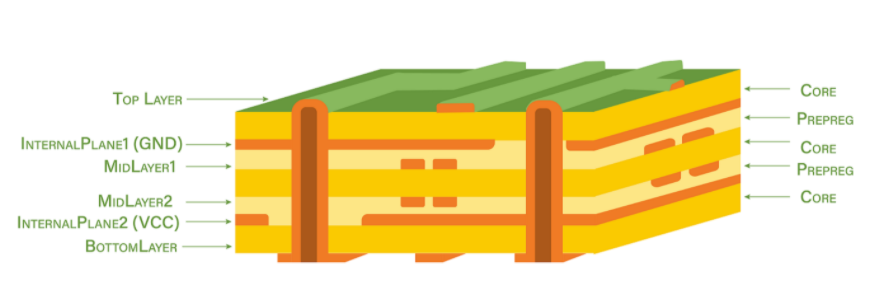

图 2多层 PCB 的横截面强调了与封装相比的尺寸和深度优势。资料来源:P2F 半

与封装相比,为了利用分层 PCB 可实现的更大尺寸和深度,一些设计团队尝试实施单独的模拟和数字接地层,以避免两种类型电路之间基于电流的 EMI 问题。不幸的是,这被证明具有在板上创建偶极天线的恼人趋势。将单独的接地平面与迹线连接以改善此类问题通常会导致生成另一个天线。

然而,频率和带宽并不是 EMI 的唯一来源,通过这些术语判断芯片或电路的 EMI 潜力并不总是足以评估它们成为噪声源的风险。例如,高精度 ADC 更准确地评估 EMI 不是通过它们的 F max,而是通过它们的采样率。

电路板设计人员长期以来的做法是将电路板上的模拟和数字组件分开,只允许 DAC 或 ADC 跨越它们之间的边界。此外,数字和模拟信号迹线被隔离到各自的区域——刻意避免通过另一个区域。最后,必须考虑不要将模拟或数字迹线越过另一个。

然而,有时无法避免将一种信号迹线穿过另一种域或交叉模拟和数字信号迹线的必要性。在这种情况下,有经验的 PCB 设计人员会确保违反设计规则的行为发生在接地平面参考之上。不这样做是通过感应诱发串扰的邀请。

然而,目前几乎不可能在 PCB 上的模拟和数字信号域之间进行清晰的划分。SoC 器件在数量上同时包含模拟/RF 和数字电路,并且很少像 ADC 和 DAC 那样放置在电路板上跨越域边界。即使在功能上看起来完全数字化的芯片也可以有一个小而重要的嵌入式模拟组件,例如带有内部 PLL 的 DSP。

通常,PCB 设计人员将混合信号设备接地到与纯模拟组件相同的接地平面。然而,对于具有相对较小模拟组件的芯片,它可能会变得更加棘手。通常,芯片供应商会提供单独的模拟和数字接地引脚,并指示电路板工程师将两个引脚都连接到数字接地参考平面。不过,请准备好在模拟接地引脚上放置一个去耦帽。另一方面,如果设备供应商指示电路板工程师将模拟和接地引脚连接在一起,则该走线应该以尽可能短的距离连接到模拟接地。

与芯片和封装相比,PCB 的一个巨大优势是能够部署大而厚的铜接地层。这样的平面在很宽的频率范围内提供了一致的阻抗,减少了 R 和 L 分量,并有助于提高导热性。

为了防止大的瞬态电流从高频数字开关活动中穿过这样的接地层,并导致连接到同一参考层的模拟设备出现 EMI 问题,电路板设计人员经常被迫将平面切割成数字和模拟部分。这些单独的平面可以使用肖特基二极管或类似的高阻抗方法连接,以防止在平面之间建立瞬态电压,同时阻止电流尖峰在它们之间交叉。

需要注意的是,上述规则和解决方案并非圣经。情况各不相同,因此需要灵活性和适应性。EDA 和 PCB 公司可以提供额外的专业知识,并且不断努力为电路板层开发改进的介电材料,这些材料是优质的绝缘体,同时仍然具有成本效益和可制造性。

整体 SoC 设计

到目前为止,在本系列中,我们已经将芯片、封装和 PCB 问题作为独立的实体进行了讨论。然而,在 SoC 设计期间连续和单独处理它们将是一个严重的错误,因为它不可避免地会导致迭代设计周期、大量返工、破坏进度和令人震惊的成本超支。我们需要的是一种更全面的方法,可以跨多个层次集成设计需求,我们将在下一部分中讨论这个主题。

Kedar Patankar 是 P2F Semi 的首席技术官 (CTO),是一位在设计、开发和客户关系方面拥有 23 年经验的半导体行业资深人士。

-

浅谈PCB设计七大流程2010-04-16 2924

-

PCB封装,一体成型电感PCB封装3D模型jf_97106930 2022-08-27

-

PCB封装,Foot Print 绘制经验分享#pcb设计学习电子知识 2022-09-26

-

altium pcb教程-IPC封装创建PCB封装学习电子知识 2023-08-14

-

浅谈PCB的制作流程2009-10-20 7124

-

PCB经验浅谈2012-08-04 9093

-

浅谈原理图和PCB图的常见错误2012-08-12 13237

-

表面安装pcb设计工艺浅谈2012-08-20 2839

-

浅谈SOC系统知识2016-08-05 7495

-

PCB设计与制造封装文章TOP 62018-09-18 1905

-

浅谈射频PCB设计2019-03-20 14836

-

浅谈电子三防漆对PCB板的作用有哪些?2023-04-14 1131

-

SOC封装主要优势是什么?2023-11-02 491

-

PCB优化设计浅谈2016-12-16 712

-

浅谈LED封装PCB和DPC陶瓷PCB2020-11-06 5568

全部0条评论

快来发表一下你的评论吧 !