Xilinx FPGA中设计层次的各个定义

描述

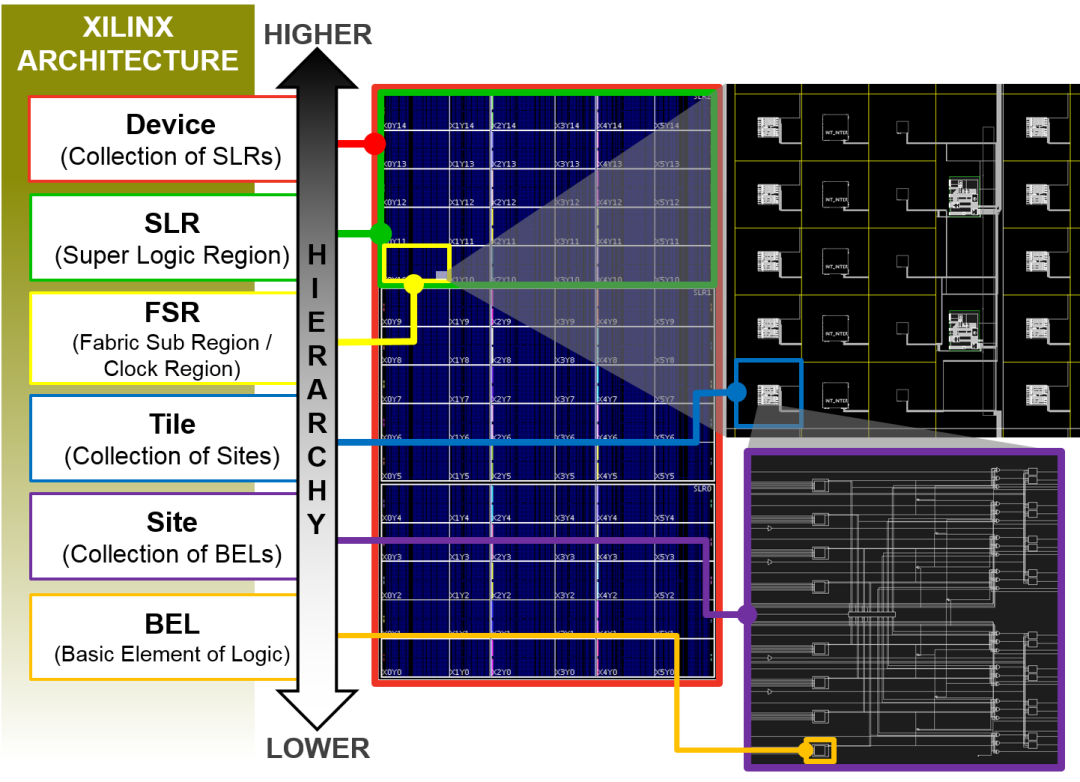

在Xilinx FPGA中,从底层到整个设备可以划分为6个层次:

BEL

Site

Tile

FSR

SLR

Device

下面我们从下到上依次来看一下各个定义。

BEL(Basic Element of Logic)

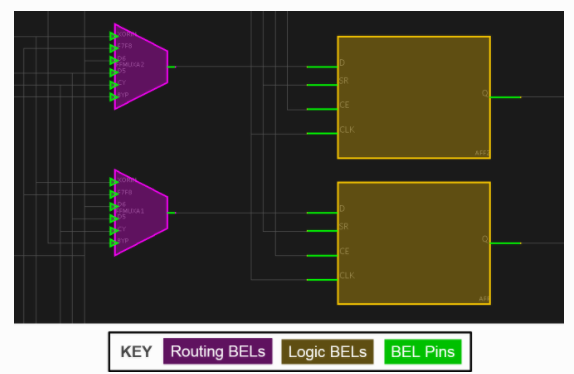

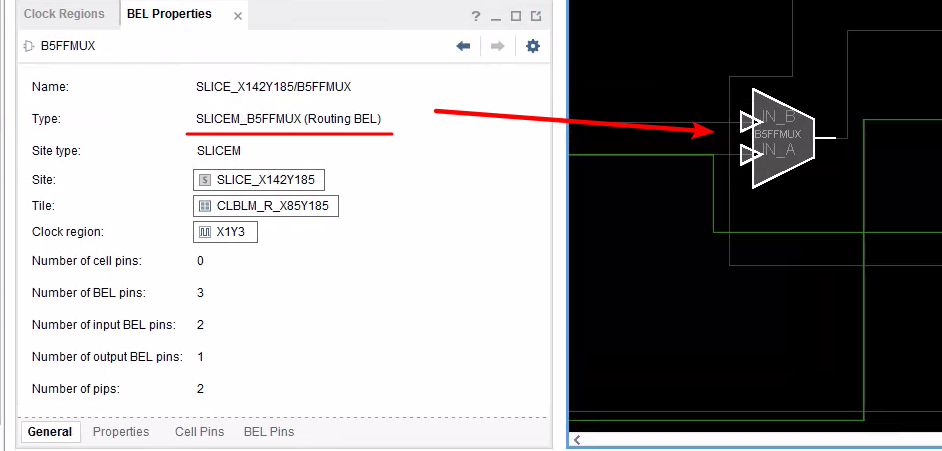

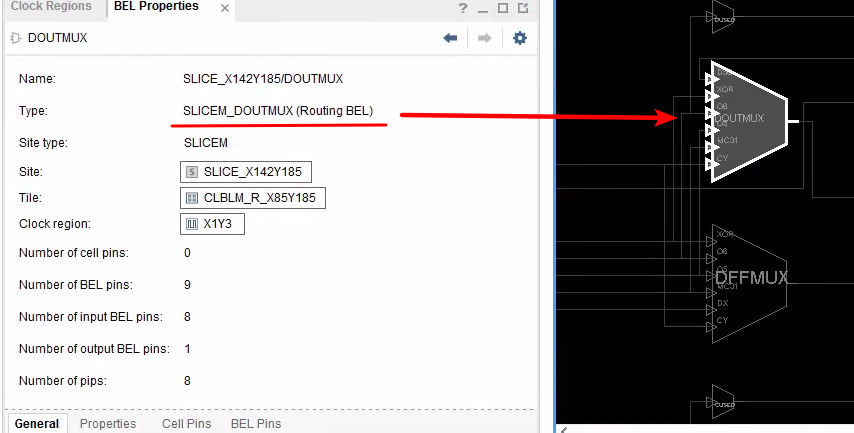

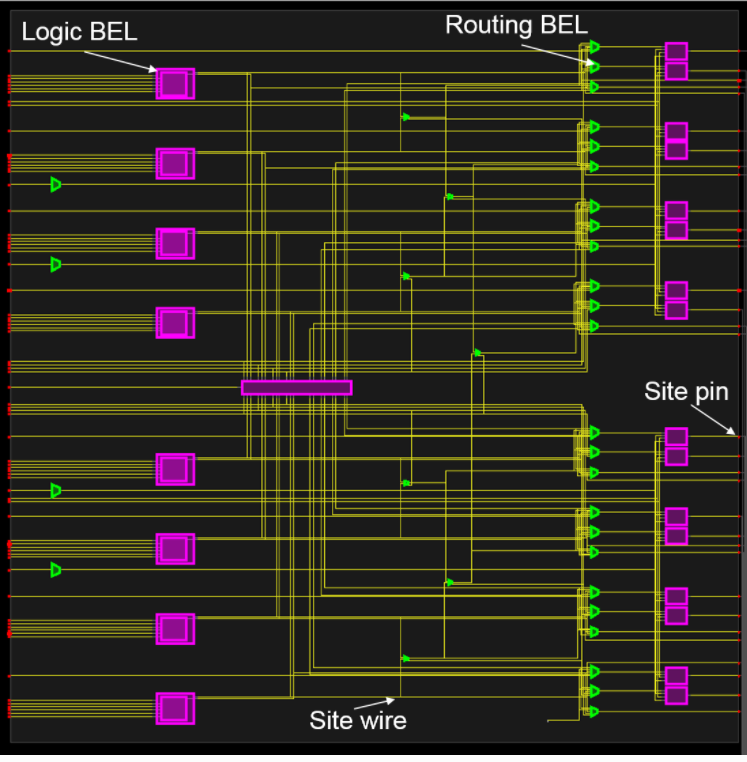

BEL是最底层的基本元素,也可以叫atomic unit(原子单位),BEL是FPGA中最小、不可分割的组件。BEL有两种:Logic BEL和Routing BEL。像我们常说的LUT、FF、CARRY都属于Logic BEL,Routing BEL我们平时不常说,很多工程师可能也没太听过,像FFMUX和DOUTMUX都属于Routing BEL,它们分别长下面这样:

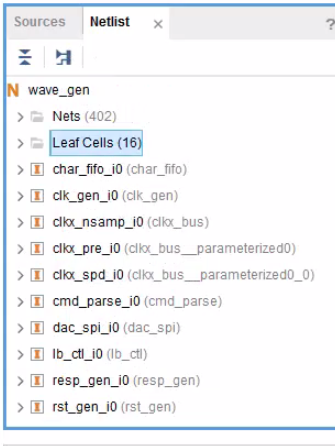

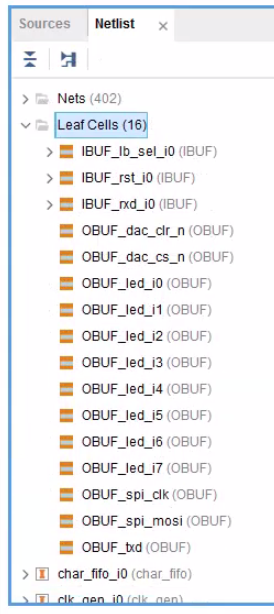

在Vivado综合或实现的Design中,可以看到会在每一个模块下都会有Nets和Leaf Cells。

Leaf Cells就是FPGA中一个个真实存在的硬件模块,Vivado中place_design做的工作就是把这些Leaf Cells放到合适的BEL上。

Site

一系列相关的元素与它们的连线组成了Site,Site中主要包含下面三种:

BEL

Site的输入输出管脚

Site内部的连线

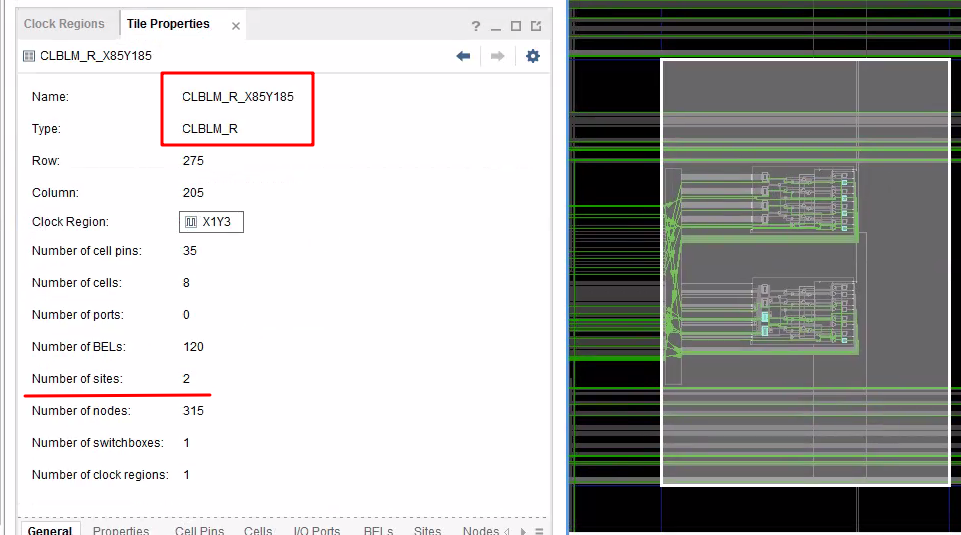

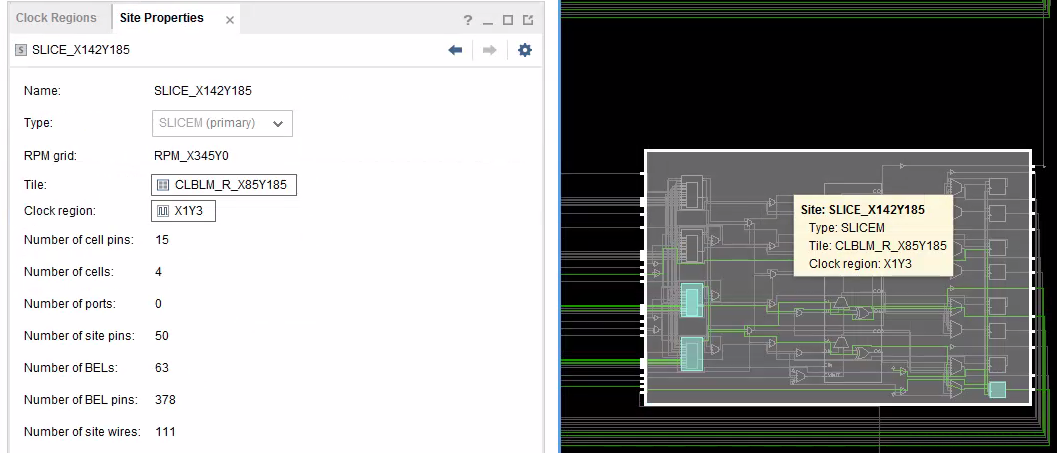

Site一般都是跟Slice、DSP48、BRAM等是对应的,我们以Slice为例,在7系列的FPGA中,一个CLB有两个Slice,下图的白色框是一个CLB,从左边的Properties中可以看出,包含了两个site,其实就是包含了两个Slice。每个Slice都有独立的site,所以这个CLB中就有两个sites。

Xilinx FPGA中很多元素的位置都是以_X_Y结尾来表示该元素在坐标中的位置,下图中的这个Slice的位置是X142Y185。

Tile

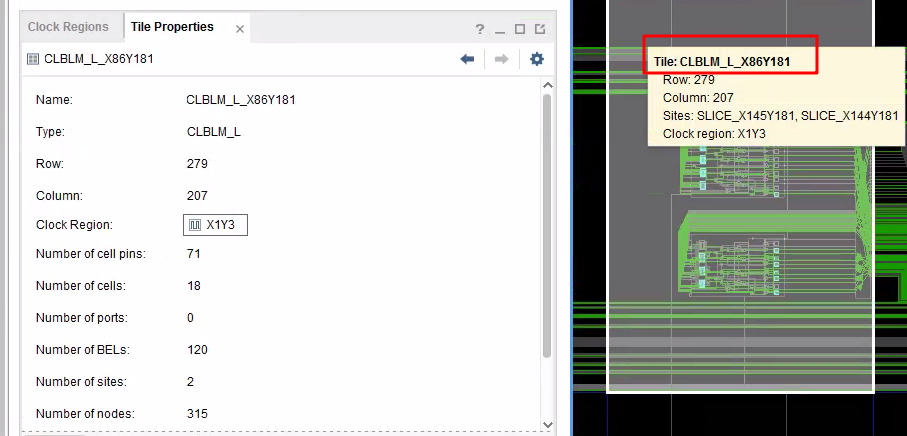

Tile是比Site更高一级的概念,一个Tile里面包含多个Site,Tile没有pin的概念,比如下面这个Tile,其实就是一个CLB。

FSR

FSR就是Fabric Sub Region or Clock Region,是由一片Tile组成的,在UltraScale的FPGA中,所有的FSR的高度都有60个CLB,但宽度不尽相同。

时钟routing和distribution的粒度与FSR相同,在UltraScale的FPGA中,有24个水平的routing track,24个垂直的routing track,24个水平的distribution track和24个垂直的distribution track,相邻的FSR就靠这些track互连。

SLR

SLR就是Super Logic Region,这个概念仅针对SSIT的FPGA,也就是包含多个die的芯片,这样每个die就被称为一个SLR。

Device

这个概念就无需过多介绍,就是指整个FPGA;如果是单个die的片子,那么多个FSR就组成了Device,如果是多个die的片子,那么多个SLR组成了Device。

原文标题:FPGA中BEL Site Tile FSR SLR分别指什么?

文章出处:【微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

-

Xilinx FPGA中的基础逻辑单元2022-12-27 3626

-

Xilinx 7系列FPGA芯片管脚定义与封装2021-07-08 12221

-

Xilinx 7系列FPGA管脚是如何定义的?2021-05-01 12044

-

Xilinx 7系列FPGA管脚是如何定义与Pinout文件下载2021-04-27 9363

-

Xilinx 7 系列FPGA中的Serdes总结2020-12-31 1890

-

基于Xilinx FPGA用于ASIC前端验证的问题总结2018-12-22 2286

-

Xilinx FPGA的Maxim参考设计2017-10-31 1149

-

(Xilinx)FPGA中LVDS差分高速传输的实现2017-03-01 1514

-

EDK中PS2自定义IP2016-06-07 1052

-

Xilinx_FPGA系列入门教程(一)—如何搭建Xilinx2016-01-18 899

-

xilinx的FPGA中MUXCY是什么?2015-07-20 9897

-

成为Xilinx FPGA设计专家(基础篇)2014-11-03 3378

-

xilinx同步设计技术2009-06-14 478

全部0条评论

快来发表一下你的评论吧 !