G-NAVP TM控制拓扑的设计方法和PCB布局规则

描述

在设计过程中,元器件设计和PCB布局对电源性能有很大影响。仔细的 PCB 布局对于实现低开关损耗和干净、稳定的运行至关重要。选择合适的组件使电源轻松通过 Intel 和 AMD 的规格。本应用笔记将介绍 G-NAVP TM控制拓扑的设计方法,包括导通时间设置、开关频率设置、负载线设置和 DCR 电流传感网络设置。之后,将显示推荐的 PCB 布局规则,以避免噪声干扰,使控制器更加稳健。

1.设计方法和元件选择

以下设计方法将以 RT8884B 为例,其设计符合 Intel VR12.5 规范。RT8884B 有三个主要的设计程序。第一步是开启时间和开关频率的初始设置。第二步是 DCR 电流感应网络设计。最后,我们要完成负载线设计。

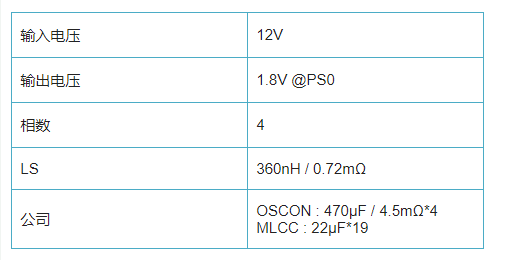

参考 Shark Bay VRTB 供电指南,推荐的输出滤波器如下:

输出电感:360nH / 0.72mΩ

输出大容量电容:560µF / 2.5V / 5mΩ (max) 4 to 5pcs

输出陶瓷电容:22µF / 0805(顶部最多 18 个站点)

1.1.开启时间和开关频率的初始设置

一般来说,更高的开关频率可以实现更快的瞬态响应,更小的稳态输出纹波,并减小功率元件的尺寸和PCB空间。然而,较高的开关频率会导致较低的转换效率、较差的抗噪性和热问题。因此,需要将最大开关频率限制在一个合理的范围内,以权衡利弊。确定最大开关频率后,根据占空比与开关频率的关系,即可得到最大导通时间。

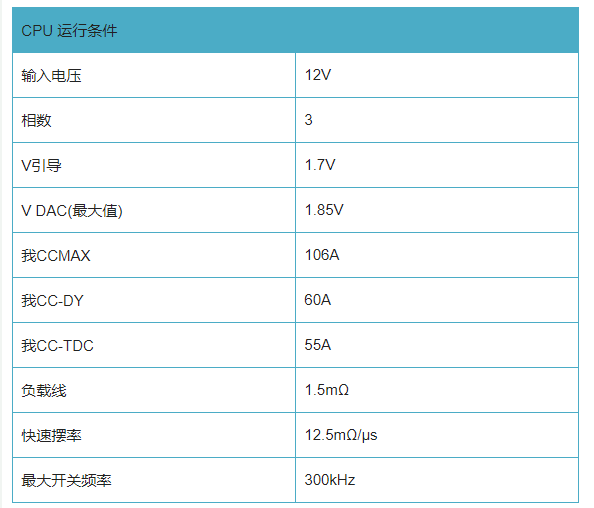

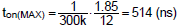

其中V DAC是参考电压,f sw,max是最大开关,V IN(MAX)是最大输入电压。下面是 RT8884B 的设计实例。

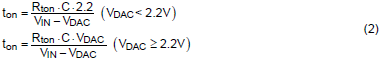

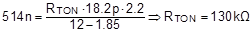

由于 RT8884B 是一种恒定导通时间控制,其专利的 CCRCOT(Constant Current Ripple COT)技术可以通过输入电压和 VID 代码生成自适应导通时间,从而获得恒定电流纹波。从而在不同的输入和输出电压工作范围内,输出电压纹波几乎可以控制为一个常数。在输入电压端和 TONSET 引脚之间连接一个电阻器 R TON以设置导通时间宽度。

其中 C = 18.2pF

其中 V IN是最大输入电压,V DAC是参考电压,t on是导通时间,由上式确定。下面是 RT8884B 的设计实例。

1.2.DCR电流感应网络设计

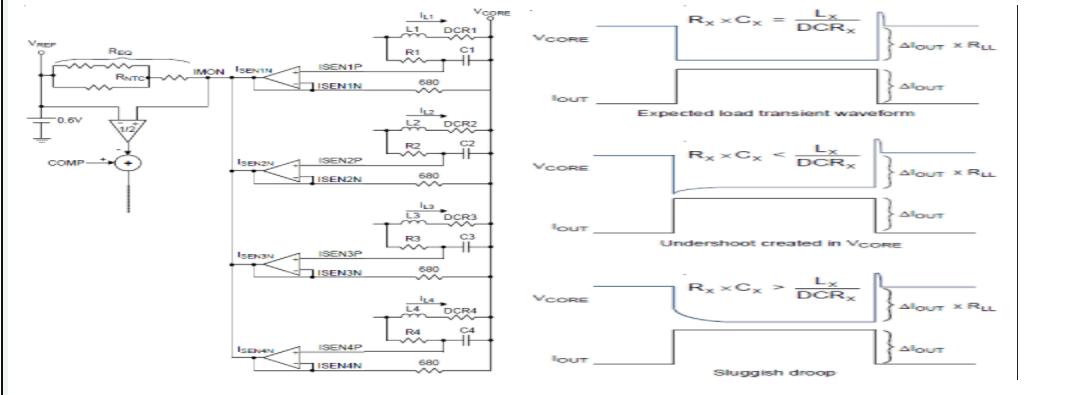

图 1. RT8884B 的整个电流回路结构。

图 2. 不同 τ Cx和 τ Lx时间常数对应的输出波形。

图 1 显示了 RT8884B 的整个电流回路结构。DCR 电流传感网络的设计对 ACLL 性能和 DCLL 精度都起着重要作用。对于不同的时间常数设计,ACLL 行为可以分为以下三个条件。此外,图 2 显示了具有不同 τ Cx和 τ Lx时间常数的相应输出波形。

• 如果τ Cx与τ Lx匹配,则可以设计预期的负载瞬态波形。

• 如果τ Cx大于τ Lx,则输出电压随着负载的增加而缓慢下降。

• 如果τ Cx小于τ Lx,输出电压将下降以减小下冲规范的裕度。

其中 DCR x是电感的等效电阻,L x是电感的电感量,R x和 C x是 DCR 电流检测网络参数。

通常,τ Cx时间常数将被设计为等于或略大于 τ Lx时间常数,以防止过冲和下冲有更多余量以通过规范。请注意,C x可能会因偏置电压、温度或频率等因素而衰减。在设计 DCR 电流传感网络时,需要考虑对 C x的衰减影响。

由于电感的铜线具有正温度系数,DCR值随着负载电流的增加而线性增加。因此,为了获得更好的 DCLL 性能,需要一个带有 NTC 热敏电阻 (R EQ ) 的热补偿网络来补偿电感 DCR 的正温度系数。详细的热补偿可以参考具体产品的设计工具。

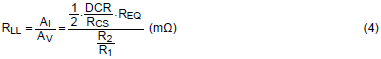

1.3.负载线设计

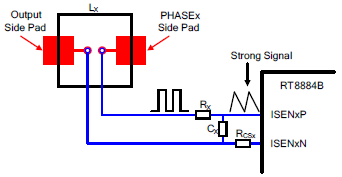

在 G-NAVP TM拓扑中,负载线设计取决于电流环路增益和电压环路增益的比率。详细的负载线方程将显示在相应的 IC 数据表中。下面以 RT8884B 为例。

其中 DCR (25°C) = 0.72m Ω,R CS = 680 Ω是电流感应电阻器,R EQ (25°C) 用于热补偿,R 2 / R 1是补偿器 A V增益. 通过这个方程,负载线可以简单地通过调整补偿器 A V增益来改变。遵循 Intel VR12.5 规范,需要 1.5 (mW) 负载线;因此,可以确定R 2 / R 1 A V增益。RT8884B 的设计实例如下图所示。

2.布局考虑

仔细的 PC 板布局对于实现低开关损耗和干净、稳定的运行至关重要。开关功率级需要特别注意。如果可能,将所有电源组件安装在电路板的顶部,使其接地端子彼此齐平。请遵循以下指南以获得最佳 PC 板布局:

2.1. 功率级布局指南

• 保持高电流路径短,特别是在接地端子处。

• 保持电源走线和负载连接短。这对于高效率至关重要。

• 在电感器的充电路径和放电路径之间进行权衡时,最好让电感器的充电路径比放电路径长。

2.2.IC Sensing Pad 和 RGND 布局指南

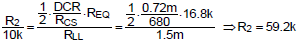

• 将电流感应元件(C X、R CSX、R X)靠近控制器放置,以避免电流感应信号被噪声耦合。

图 3. 电流感应元件的放置。

• 用于电流限制和电压定位的 ISENxP 和 ISENxN 连接必须使用开尔文检测连接来保证电流检测精度。电感器的走线直接从电感器焊盘而不是从电感器的连接平面延伸。

图 4. 电流感应走线的电感垫。

• 来自电感检测节点的PCB 走线应并联回控制器。通常,这些走线位于 PCB 底层的电感器下方。如果这些走线在内层上运行,则电流检测走线上方必须有一个接地层,作为顶层的屏蔽。

• 将高速开关节点(PWM、UG、LG、相位等)远离敏感模拟区域(COMP、FB、ISENxP、ISENxN 等)。

• 用户需要通过低阻抗路径将裸露焊盘连接到接地层。建议使用至少 5 个过孔连接到 PCB 内部层中的接地层。

三、实验结果与结论

3.1.实验结果

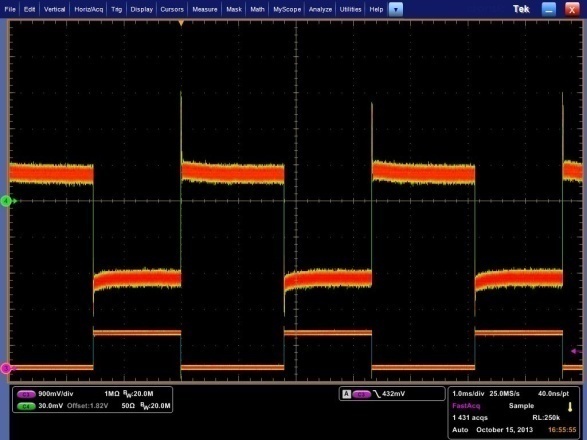

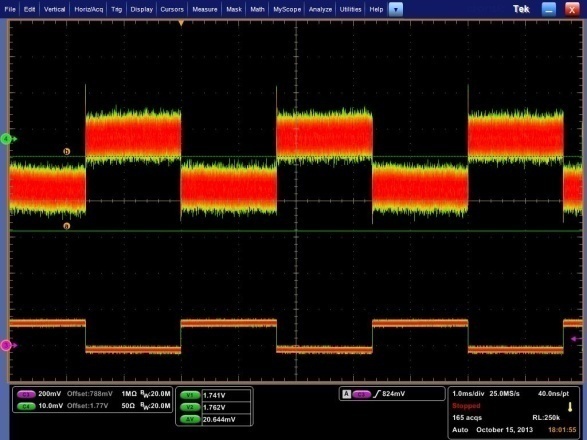

图 5 为 RT8884B EVB 样例,应用于 VR12.5 应用,支持 4/3/2/1 相位。实测负载线曲线和效率如图 6 所示。从实测结果来看,G-NAVP TM拓扑可以提供准确的负载线,并且仍然保持较高的效率。图 7 显示了一个大阶跃和一个小阶跃负载瞬态波形,这表明了快速稳定的瞬态性能和适当的 AVP 控制。

图 5. RT8884B 的 EVB 示例。

表 1. EVB 测试条件

图 6. RT8884B 测得的负载线和效率。

(CH3: 负载电流 (900mv/Div) ; CH4: 输出电压 (30mV/Div))

(a) 大步进 (1A-61A) ACLL @300Hz (b) 小步进 (50A-60A) ACLL @300Hz

图 7. RT8884B 测得的 ACLL 结果

3.2.结论

系统组件的设计通常需要在许多限制之间进行折衷,以在效率和性能上获得最大收益。此外,特殊的布局技巧用于最大限度地减少寄生元件的影响,避免高速开关噪声耦合。本应用笔记展示了 G-NAVP TM控制拓扑的一般设计方法和 PCB 布局规则。遵循上述规则,用户可以毫无不便地使用立锜的控制器IC。

-

PCB元器件布局布线基本规则2023-11-13 1222

-

PCB布局、布线、规则设计的高级技巧2023-09-09 5903

-

PCB设计元器件布局布线基本规则是什么2023-05-24 2558

-

PCB设计布局规则及技巧2023-05-04 3745

-

PCB布局布线的规则2022-10-28 3518

-

PCB的布局布线规则2021-11-11 10132

-

PCB设计中布局布线实际技巧以及相关规则2021-11-06 1329

-

PCB电路板元件布局布线基本规则下载2021-04-24 2780

-

pcb板的布局规则分享!2019-08-20 3885

-

PCB元器件布局检查规则pdf下载2017-12-22 1178

-

EMI相关PCB布局布线规则2016-07-26 1614

-

PCB布局布线规则2013-08-06 5694

-

PCB板基础知识、布局原则、布线技巧、设计规则2012-07-26 51454

全部0条评论

快来发表一下你的评论吧 !