一文详解PCIe的知识点

描述

全球对数据的需求没有减弱的迹象,并继续对服务提供商施加压力,要求他们更快地处理更多比特。这种压力在大型数据中心中感受到了强烈的压力,这些数据中心正在应对越来越需要带宽的趋势。这些趋势包括对娱乐流媒体、物联网应用、与联网汽车和自动驾驶相关的服务以及具有密集分析的企业数字化转型的需求增长。

数据中心推动接口演进

迫切需要在整个基础设施中实现更快的数据传输协议,包括处理通过大量通道到达的不断增加的数据量、存储和维护数据、检索和处理数据以及返回结果 - 具有附加值 -给客户。

负责当今网络和接口协议的各个机构正在加紧工作,以从他们的标准中获得下一个性能提升。但是,网络中不同点之间的过度速度不匹配可能会导致瓶颈。进步的速度需要保持领先,但不同的协议应该以相似的速度向前发展也很重要。

在领先数据中心运营商的需求推动下,PCIexpress® (PCIe®) 的发展大致与不断发展的多千兆以太网规范保持同步。运营商正在从 100Gbit 以太网转向在其整个场所采用最新的 400Gbit 连接。为了最大限度地提高所获得的收益,需要更新更快的 PCIe 代来将数据中心的服务器与本地外围设备(例如存储和 AI 加速器卡)连接起来。PCIe 4.0 规范于 2017 年公布,带宽是上一代的两倍。随后在 2019 年发布了 PCIe 5.0,将传输速度提高到 32GT/s,从而为 x16 链路提供 128GB/s 的总带宽。

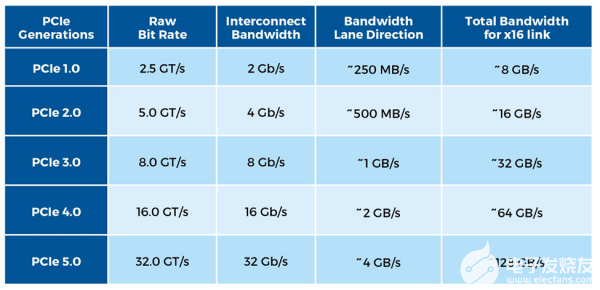

图 1 总结了各代 PCIe 的总速度。PCI-SIG 已经在开发 PCIe 6.0,预计将在 2021 年完成新规范。PCIe 很可能会继续成为需要性能的外围通信的首选协议。

图 1. PCIe 标准的发展速度与多千兆以太网类似。

PCIe 规范的独特寿命

PCIe 5.0 产品现已进入市场。但是,旧规格没有到期日期。向后兼容性是 PCIe 的一个关键优势,它允许早期规范为个人计算、游戏以及一些企业计算和网络应用程序等机会提供经过验证的高性能解决方案。

除了按照最新规范设计的设备外,设计人员还需要高度集成的现成 PCIe 芯片,以支持前几代产品,以利用这些既定且广泛接受的标准。然后,设计人员可以从几代 PCIe 中选择最合适的选项,以实现具有出色性能的实用且价格合理的解决方案。芯片制造商可以继续利用他们的设计 IP 和对与每一代 PCIe 标准相关的客户支持技术的投资。

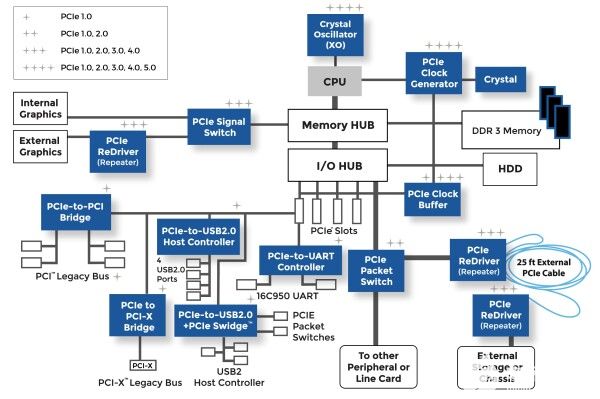

Diodes 有大量标准 IC 可供选择,为 PCIe 2.0、3.0、4.0 和 5.0 代提供支持(如图 2 所示)。设计人员可以从中选择任何一种,为各种应用实现高性能接口。

图 2. Diodes 产品组合为 PCIe 1.0、2.0、3.0、4.0 和 5.0 提供了全面的选择。

使用 Diodes 的 PCIe IC 进行灵活设计

如图 2 所示,桥接器和交换机是 PCIe 架构中的关键组件,用于连接各种类型的主机和端点设备。包桥通常在 OSI 参考模型中的两个层之间或两个协议之间提供接口。桥接器还可用于连接 PCIe 和传统 PCI 标准(包括 PCI-X),或连接到 USB 端口或 UART 总线接口。分组交换机是多端口/多通道设备,通常用于将单个根联合体扩展到多个端口。提供了额外的通道来访问其他对等系统,例如外围设备或线卡。Diodes 提供具有各种端口配置和转换功能的数据包桥接器和交换机。

此外,Diodes 结合了 PCIe 封包开关和 PCIe 至 USB2.0 桥接器的功能,以创建 PI7C9X442SL PCI Express 至 USB 2.0 PCIe Swidge™。这种创新设备可以从一个 PCIe x1 上游端口扇出到两个 x1 下游端口和四个 USB 2.0 端口,允许从系统主机处理器访问多个 PCIe 和 USB 设备。

为了提高高速系统中的信号完整性,或者需要通过更长的连接(例如外部显卡或外部存储)驱动信号的任何地方,用于 PCIe 2.0、PCIe 3.0 和 PCIe 4.0 的 PCIe ReDriver™ 可以使用,如图 2 所示。ReDriver 使用均衡和预加重等技术补偿传输线损耗,并包含引入最小延迟的输出驱动器。其效果是恢复信号余量并最小化抖动,有效地保持接收器的低误码率。与重定时器相比,ReDriver 实施起来更容易、更经济,重定时器集成了包括时钟和数据恢复在内的附加功能。

此外,Diodes 还拥有一系列无源双向 PCIe 2.0、PCIe 3.0 和 PCIe 4.0 信号多路复用器/解复用器。这些可用于将单个 PCIe 通道连接到多个通道,例如用于图形或计算的带宽扩展,或将系统连接到多协议接口。

Diodes 还具有适用于所有 PCIe 代的时序 IC,由图中所示的晶体振荡器、时钟发生器和时钟缓冲器功能指示。Diodes 的 PCIe 时钟发生器可以产生特定的时钟信号频率,输出抖动极低,适用于 PCIe 应用和其他需要类似性能的系统时钟。时钟缓冲器采用时钟发生器参考信号并产生多个输出以分布在 PCB 上。有多种配置可供选择,利用 Diodes 的专有 PLL 设计,最大限度地减少抖动以满足适用的 PCIe 规范。在可用的设备中,Diodes 的 1.8V PI6CG18xxx 时钟发生器和 1.5V PI6CG15xxx 缓冲器是具有 2、4 和 8 通道配置的 PCIe 4.0 IC。它们的集成功能为每个输出节省了四个外部电阻,

结论

PCIe 标准处于开发的最前沿,可实现领先的超大规模数据中心所需的高带宽互连。除了与最快的多千兆位以太网规范紧密匹配的最新一代的高速之外,旧标准的寿命和确保各代之间的向后兼容性使设计人员能够创建实用、负担得起和高性能的解决方案消费、桌面和工业用途。支持涵盖多代标准的广泛 PCIe 芯片组合(例如 Diodes PCIe 时序芯片、驱动器、ReDrivers、开关和桥接器组合)是成功的重要因素。

-

Linux文件系统知识点详解2023-11-02 1515

-

C语言链表知识点(2)2023-08-22 677

-

STM32 RTOS知识点2023-08-01 778

-

滚珠螺杆的基本知识点2023-07-07 2568

-

数字电路知识点总结2023-05-30 7115

-

详解射频微波基础知识点2023-01-29 3531

-

电力基础知识点合集2022-03-14 1342

-

Synopsy的Host和DPHY的知识点详解,错过后悔2022-03-08 1482

-

嵌入式知识点总结2021-07-30 1965

-

PWM知识点详解2017-03-16 1920

-

关于红外通信的一些问题知识点2016-05-05 1074

-

高一数学知识点总结2016-02-23 1526

-

计算机组成原理考研知识点归纳2010-04-13 2031

-

硅控制开关(SCS)必需知识点详解2009-07-25 1948

全部0条评论

快来发表一下你的评论吧 !