为转换器时钟应用选择最佳器件

描述

为 ADC 生成采样时钟是对干净(低抖动)时钟生成要求最苛刻的应用之一。使用嘈杂的时钟会直接影响数据转换器准确转换其接收信号的能力。信噪比 (SNR) 是模数转换器的一项重要规格,用于量化 ADC 工作的准确程度。以下是将 SNR 与抖动联系起来的公式:

信噪比 = -20*log(2π*F IN *t J ); 其中 t J是 RMS 时间抖动,F IN是模拟带宽。t J (RMS) 是通过在编码带宽上对相位噪声进行积分而获得的。

我不会重新讨论公式的推导,因为它可以在网络上的其他地方找到。

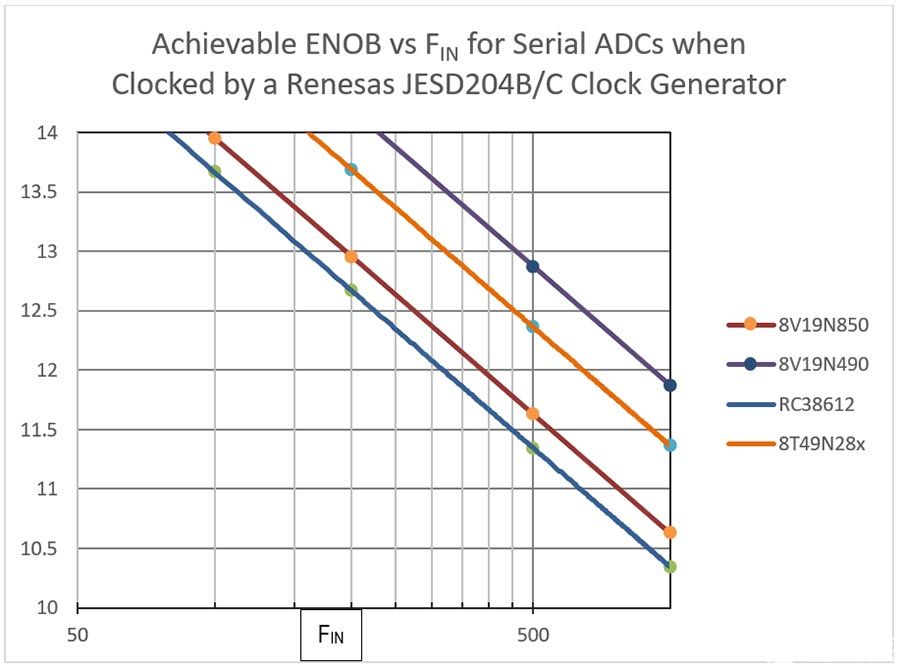

瑞萨的计时产品组合是业内最大的。为了帮助您找到最适合您需求的部分,瑞萨电子提供了以下图表。以下是如何使用图表来确定满足您需求的正确部分:在 XY 网格上找到与您的用例相对应的点,然后向右移动和/或向上移动到图表上的下一个实线对角线。您遇到的第一条实线表示瑞萨推荐您首先考虑的设备。为并行和串行输出 ADC 提供了单独的图表。现代串行输出 ADC 通常需要具有 JESD204x 同步功能,因此对于该图表,仅填充了支持 JESD204B/C 的时钟器件(图 1)。

要探索此处推荐的设备的替代方案,请使用先前提供的公式 [t J = (10^(SNR/-20))/ (2π*F IN ),但求解 t J ] 来确定您需要的抖动性能。将t J (作为最大抖动)插入到我们的时钟发生器产品组合或JESD204B/C 时钟抖动衰减器产品组合的参数搜索表中。

图 1. 当由 Renesas JESD204B/C 时钟发生器提供时钟时,串行 ADC 的 ENOB 与 FIN

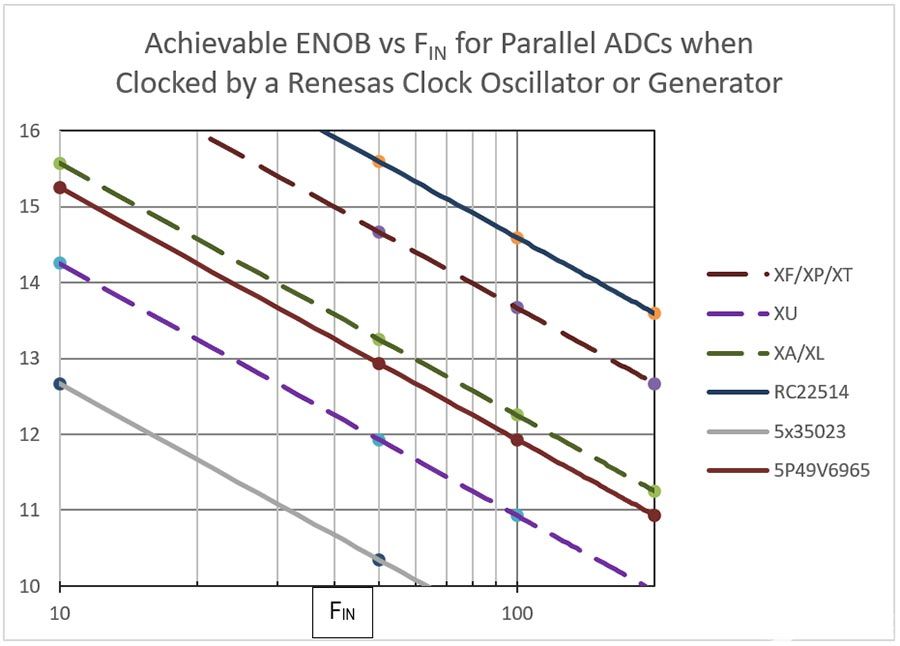

如果您的系统中只有一个转换器需要时钟,您最好从下表(图 2)中选择一个振荡器(见虚线),但如果您需要多个时钟用于附加转换器(或其他组件) ),选择时钟发生器(实线)可能会为您提供更好的服务。

图 2. 当由 Renesas JESD204B/C 时钟发生器或振荡器提供时钟时,并行 ADC 的 ENOB 与 FIN

审核编辑:郭婷

-

为您的应用选择最佳的bq2416x器件2024-10-09 273

-

逻辑器件多路转换器是什么?2024-04-28 3677

-

为给定噪声预算选择最佳数据转换器2023-02-28 1447

-

为高速数据转换器设计低抖动时钟2023-02-25 4419

-

为您的救生医疗应用选择最佳DC-DC转换器2022-07-29 2035

-

选择A/D转换器件需要考虑哪些因素呢2022-01-13 1187

-

如何为DC/DC直流电源转换器选择最佳的开关频率呢2021-11-01 2032

-

如何选择合适的时钟发生器2020-11-22 3920

-

时钟发生器的相位噪声和抖动性能为什么会影响到数据转换器?2019-07-30 3105

-

选择最佳的DC/DC转换器的五大秘诀2019-03-25 3552

-

DC/DC 转换器拓扑结构的“最佳”选择2018-12-07 9538

-

时钟发生器性能对数据转换器的影响2018-10-18 2450

-

数据转换器中时钟发生器件对系统性能的影响2017-11-17 1316

-

为降压型转换器选择电感器2009-04-27 768

全部0条评论

快来发表一下你的评论吧 !