如何寻找时序路径的起点与终点

描述

今天看《集成电路时序分析与建模》中看到这么一个知识点,觉得有点意思,就记录下来,与大家一起分享。

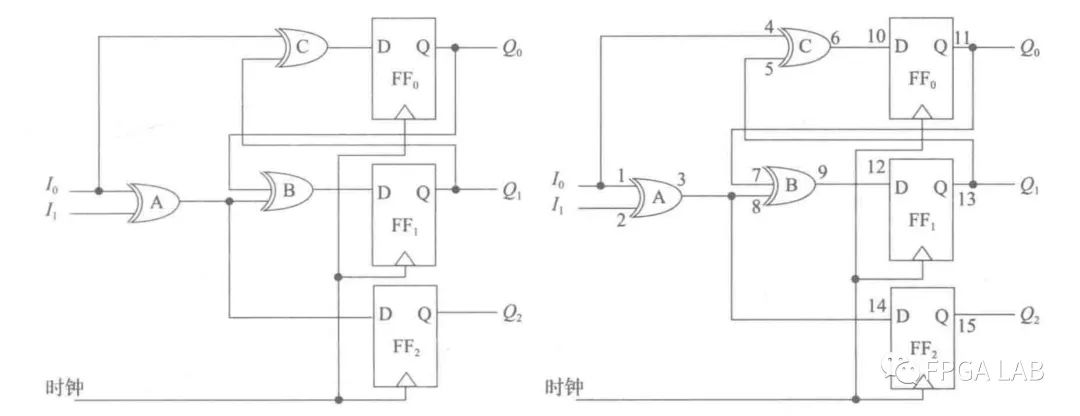

先看 如下电路图:

左边的电路图是需要分析的电路,我们的目的是要对此电路进行时序分析,那首先要找到该电路需要分析的时序路径,既然找路径,那找到时序分析的起点与终点即可。

寻找时序路径的起点和终点的原则如下:

起点:

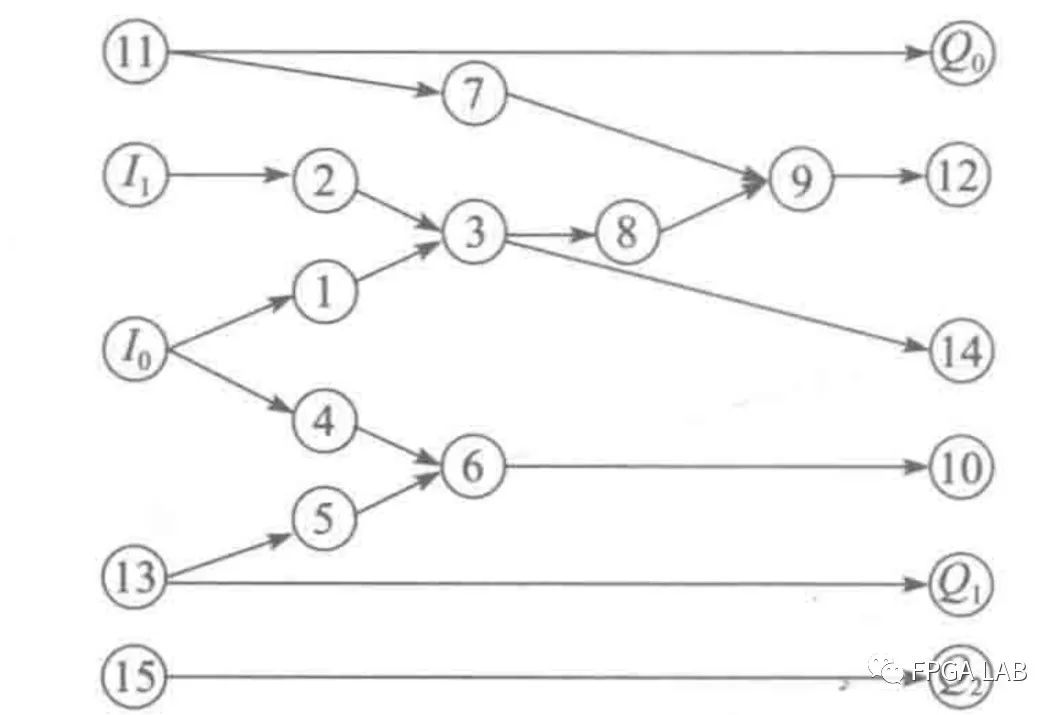

设计边界的数据输入端口或信号输入端口;如上图右边的I0,I1;

时序元件(一般指DFF)的输出,例如上图右边的11,13,15;

存储单元的数据输出,其实这和第2条一致,时序单元也是存储单元,例如DFF,但这里的存储单元一般指存储器,例如RAM等;

终点:

时序单元的数据输入,例如上图右边的10,12,14;

存储单元的数据输入,类似于时序单元,但更多指存储器等,例如RAM等;

设计边界的输出Q0,Q1,Q2;

根据上述原则即可得到,时序分析的起点(最左边)和终点(最右边):

时序路径

中间经过的节点都可认为是延迟单元。

实际进行时序分析时,可不必每次都这么转换,但是不得不说,这种理论化的方式可以让你的分析更具理论支撑,见多了熟悉了之后便可更快速的识别时序路径。这是分析的第一步,祝入门快乐。

审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

起点,经过点,终点,三点xyz,画三维圆弧。2024-07-17 5624

-

请问知道圆弧的起点和终点坐标和半径,labview,画弧,2023-11-01 3813

-

FPGA时序约束之时序路径和时序模型2023-08-14 1518

-

什么是时序路径timing path呢?2023-07-05 3156

-

FPGA时序约束理论篇之时序路径与时序模型2023-06-26 1137

-

什么是时序路径和关键路径?2021-09-28 2305

-

Vivado下显示指定路径时序报告的流程2021-01-15 3498

-

FPGA案例之时序路径与时序模型解析2020-11-17 3679

-

FPGA时序约束基本理论之时序路径和时序模型2020-01-27 3223

-

什么是起点抓路?2019-09-11 1976

-

基于CCI寄生参数提取的版图时序分析2018-06-22 8490

-

XDC路径的鉴别、分析和约束方法2017-11-18 6986

-

基于时序路径的FPGA时序分析技术研究2017-01-03 911

-

已知起点终点坐标和半径怎么画圆弧2013-03-21 13632

全部0条评论

快来发表一下你的评论吧 !