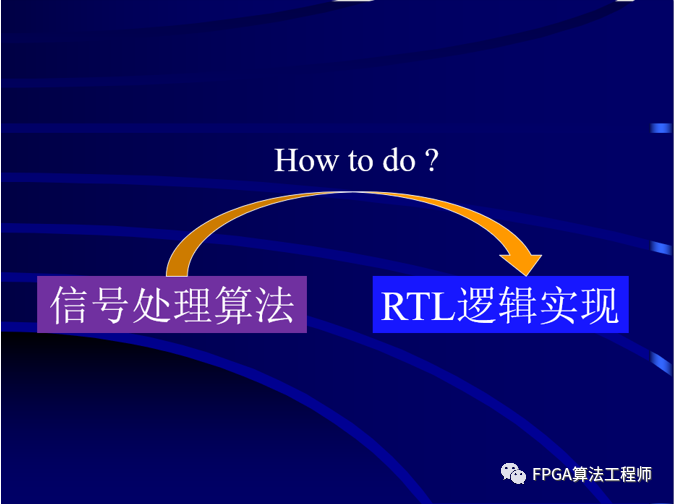

把一个算法用RTL实现,有哪些比较科学的步骤?

描述

针对近日技术交流群里讨论的算法与RTL实现问题,写篇文章,做一次总结。

新手遇到的是新问题,对于有相关经验的工程师而言,可能都遇到过。

作为算法、FPGA和IC等集中交流的平台,群贤毕至,集思广益,解决大家对相关知识和技术上的困惑,让问题变得更简单。

群友们提到一个很多人都会遇到的现实问题:

“把一个算法用RTL实现,有哪些比较科学的步骤?第一步干什么?第二步干什么?第三步干什么……?”

这个问题,对于FPGA、ASIC等逻辑电路设计人员来讲,是非常重要的问题。

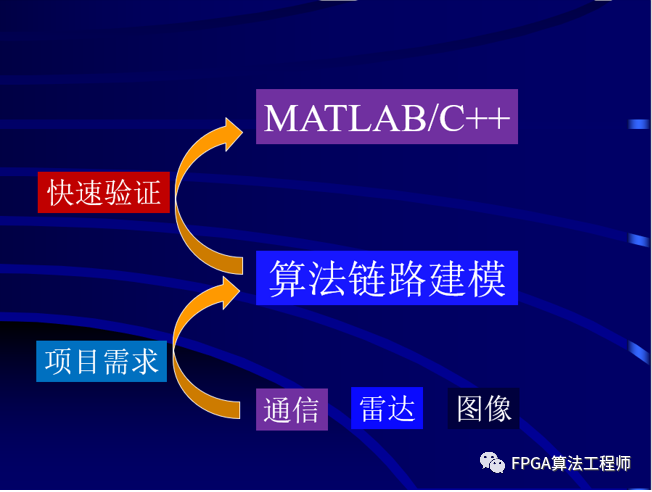

通常来讲,我们做算法实现,需要有对标的算法模型,作为验证硬件逻辑设计是否正确的参考依据。

我们首先要根据实际需求,针对某方面的信号处理问题,做一个链路级或模块级快速仿真验证设计。最常见的比如通过MATLAB/C/C++等软件环境进行设计和验证。

软件环境可以快速搭建仿真模型,并且进行验证,为硬件RTL实现提供参考依据。在具体算法设计时,必须考虑数据流的处理过程:数据从哪里来,数据需要经过哪些步骤处理,处理之后送到哪里。

接下来,我们需要将MATLAB、C++等算法模型由浮点转为定点,这个工作可以做好之后再去做逻辑设计,也可以省略,但一定要清楚是如何定点的。

做好算法设计后,需要进行性能评估,看是否符合预期要求,不符合则进一步优化,或者换一种设计方法。

在做逻辑实现之前,还有一个重要工作,就是对算法处理步骤进行一步一步分解,解决如何从a到b再到c的过程,落实到加减乘除。

当算法实际满足要求后,则考虑逻辑实现的问题。

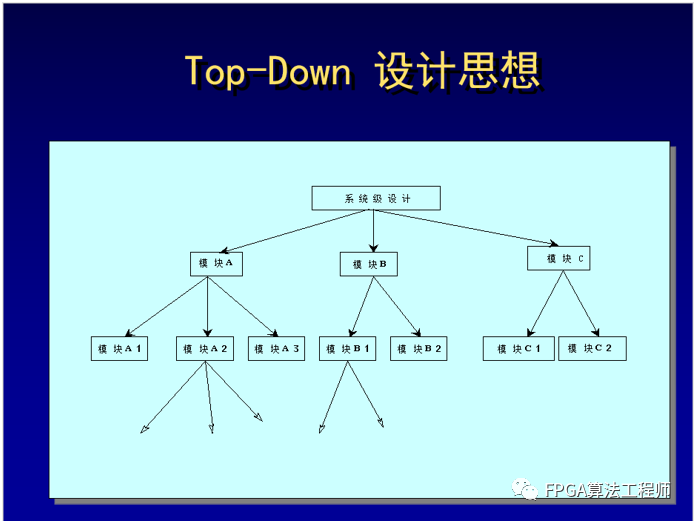

首先,建议采用自顶向下的设计思想,进行系统架构设计,明确整个处理过程,需要执行哪些功能,涉及哪些接口。

接下来,选芯片器件,评估资源占用情况,评估需要用多少乘法器,除法器,DSP,BRAM,GT等。

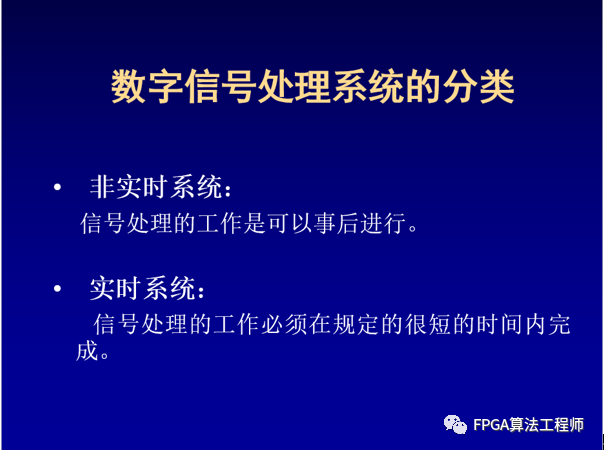

其次,评估处理时间要求,是否需要实时性处理,给予多少时间来处理,进而评估所需时钟频率,以及是否需要存在多个时钟域处理。

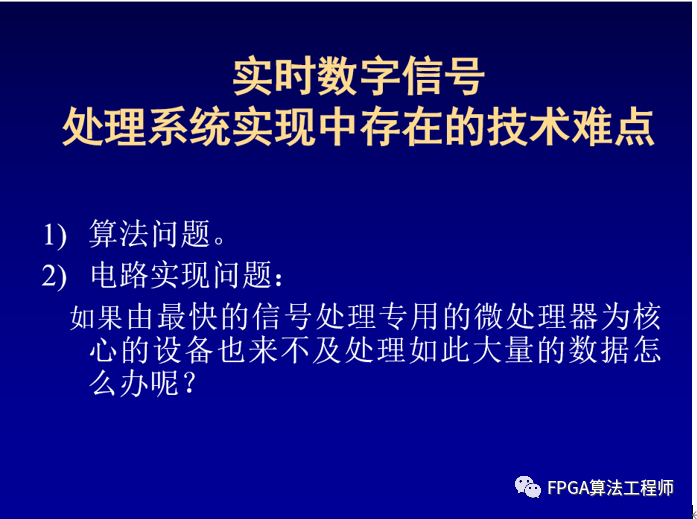

对于信号处理系统,有的需要实时处理,有的则不需要实时处理。最具挑战的无疑是实时性要求高的通信、雷达和图像等领域的信号处理问题。

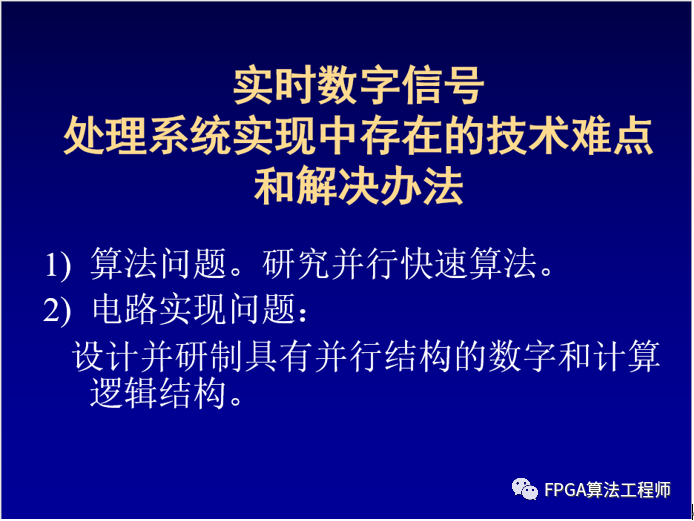

首先解决信号处理中的算法问题,为实现某一处理过程,需要分哪些步骤,最终得到什么样的结果。

为了实现实时处理,逻辑电路该怎么去设计?

于是,算法问题既要研究如何处理数据流的问题,也要研究如何快速处理的问题。

电路实现时,则需要考虑资源消耗、并行处理结构,流水处理和控制逻辑。

如果有处理速率要求,则需考虑并行+流水的处理方式,并考虑单时钟下的数据位宽。

同时,务必明确数据流向,前后级接口,功能模块内部RTL逻辑处理,细化到每个时钟应该怎么处理,step by step。

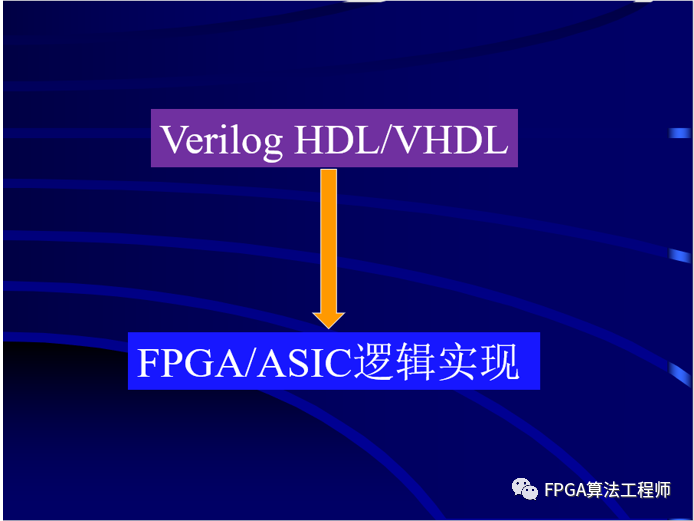

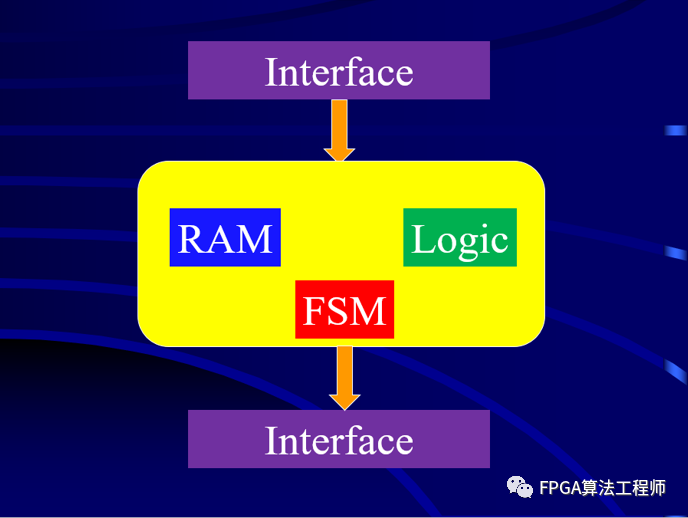

以上都比较明确后,可以着手进行RTL设计。RTL设计的核心,便是寄存器、RAM和FSM的灵活使用。其中,FSM占据了大部分功能。通常情况下,我们不只是操作纯数据流,而是在各种控制信号和参数下进行设计,此时涉及各种FSM和选择器设计,并注意是否需要进行流控。

RTL代码设计完成之后,进行TestBench平台搭建和仿真验证是必要的,特别是对于复杂功能模块或系统设计而言。经验再丰富的工程师,也不敢保证,不经过仿真验证直接上板一定没问题。

验证也是一门重要的技术,这也是为什么存在IC验证岗位,目的就是为芯片成功流片严格把关,一旦流片失败,损失重大,影响深远。

FPGA的开发设计,同样需要进行仿真验证。通常,我们可以通过算法链路产生所需激励源,通过TestBench对功能模块进行验证,并进行结果对比分析。重点解决两个问题:

一是验证逻辑时序是否存在问题,比如信号是否对齐,有无接口处理不当导致数据丢失等。

二是信号处理过程是否得当,数据位宽、精度等是否符合算法要求。

解决功能性问题后,就需要考虑性能问题。定点是否合适,与浮点算法性能的差异有多大,或者软件中的定点处理与逻辑电路定点处理,误差有多大。在不断验证过程中,优化算法设计和逻辑电路设计。

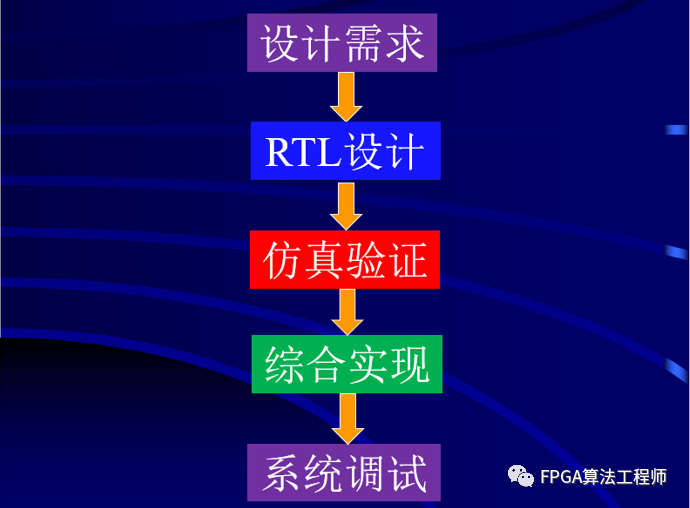

剩下的逻辑综合、实现、比特流生成和调试等环节,属于常规操作,但对于逻辑综合、实现中的时序约束和相关策略设置,也是十分重要的。

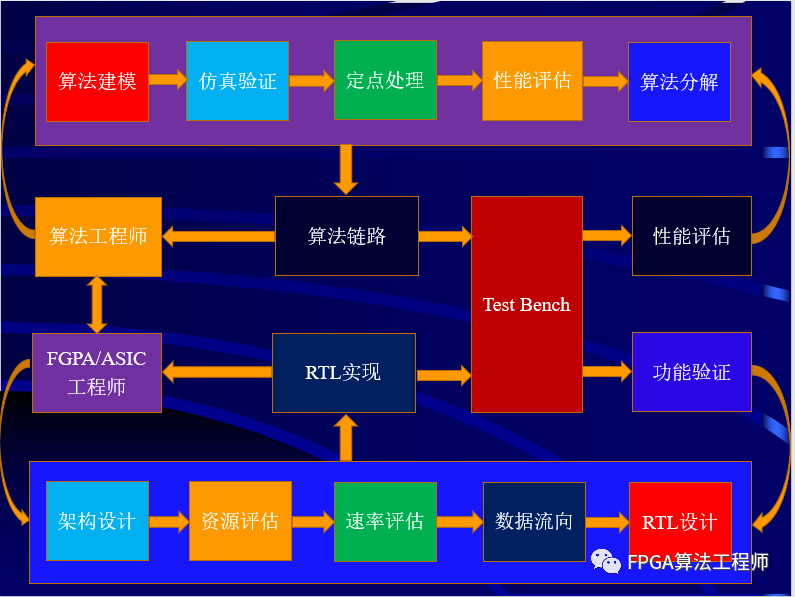

最后,用一张图总结如何从算法到RTL实现。

本文只是粗略地分析了算法到RTL代码实现之间的逻辑关系,以及从实现角度,我们应该怎么去着手。

具体到某个信号处理算法实现时,必须清楚整个信号处理过程,对算法一步一步分解,再对信号流、定点和接口进行设计。

做任何事情之前,先谋划布局,磨刀不误砍柴工,扎扎实实做好每一步,功到自然成。

审核编辑 :李倩

-

EEMD方法的原理与算法实现步骤2023-10-23 707

-

把算法用RTL实现该怎么做?2023-06-02 1782

-

把一个算法用RTL实现,有哪些比较科学的步骤?2023-03-22 2271

-

从算法到RTL实现课程预览 - 1皮特派 2022-08-01

-

Zynq 7020 FPGA做一个RTL引脚规划2020-04-10 3280

-

请问IMU和AHRS算法用stm32如何实现?2019-04-19 3105

-

请问能不能用CORDIC算法代替ROM表,用FPGA实现CORDIC算法来控制AD9910?2018-12-01 2912

-

科学的PLC编程的9个步骤2018-09-28 4015

-

硬件实现EMD算法用那种架构比较好?2018-04-25 4693

-

想用FPGA实现双边滤波算法,有懂得能说一下具体的实现步骤吗2017-03-21 8800

-

如何用数字IC/FPGA实现算法2015-09-18 6307

-

求教一个关于算法到硬件实现的问题2013-05-15 3268

-

用51单片机控制RTL8029实现以太网通信2010-09-19 714

-

OPB总线仲裁器的RTL设计与FPGA实现2010-07-17 1102

全部0条评论

快来发表一下你的评论吧 !