如何使用GreenPAK实现二进制奇偶校验生成器和检查器

描述

本应用笔记实现了一个二进制奇偶校验生成器和校验器,具有两个数据输入变体、一个并行数据输入和一个串行数据输入。它描述了实现的逻辑、GreenPAKs 的实现以及获得的结果。

二进制串行传输是使用有线或无线传输在设备之间共享信息的最广泛使用的技术之一。在这些传输中,数据错误是必须分析以获得可靠通信系统的最重要问题之一。

奇偶校验生成/校验方法是数据传输中使用最广泛的错误检测技术之一。将奇偶校验位附加到传输的数据中,以使二进制数据的 1 之和为偶数或奇数。该位用于检测二进制数据传输过程中的错误。

包含数据位以及奇偶校验位的消息从发送器节点传输到接收器节点。在接收方节点中,计算消息中的高位位数。如果这个数字与传输的奇偶校验位不匹配,则意味着接收到的数据有错误。

有几种不同品牌的商业 IC(CD40101、74HC/HCT280)可以实现奇偶校验生成器/检查器。补充 Dialog GreenPAK 设计可以对设计的可负担性、尺寸和模块化产生积极影响。例如,无论预期的 I/O 是高电平有效、低电平有效还是混合,都可以使用相同的通用 GreenPAK 设计。

在本应用笔记中,实现了由控制信号管理的集成奇偶校验发生器/校验器所需的数字逻辑。为此,应用笔记实现了奇偶校验的两种变体。第一种变体具有并行输入,以便同时加载要验证的数据位。第二个变体实现了一个串行输入,通过异步串行数据传输加载数据。为此,在 GreenPAK 中实现了串并转换。

为了实现并行输入二进制奇偶校验生成器和检查器,使用了 SLG46536V。为了实现串行输入变体,使用了 SLG46620V。

数字通信和奇偶校验位

在数字通信中,奇偶校验位是添加到二进制流中的位,以确保 1 值位的总数是偶数或奇数。这种技术是一种简单且广泛使用的错误检测方法。有两种校验位方法,称为偶校验位和奇校验位。

奇校验位系统包括对数据流中值为 1 的位的出现次数进行计数。如果数字是偶数,则奇偶校验位值设置为 1,因此包括奇偶校验位在内的整个流中高位出现的总计数为奇数。如果高位计数为奇数,则奇偶校验位值为 0。示例如图 1 所示。

图 1. 奇校验二进制系统

偶校验位方法采用逆逻辑。如果数据流中值为 1 的位计数为偶数,则奇偶校验位值设置为 0,使包括奇偶校验在内的整个流中的高位总计数为偶数。如果值为 1 的位计数为奇数,则奇偶校验位设置为 1,因此整个流具有偶数个高位。

图 2.系统图

为了检测错误,接收器必须计算接收到的二进制数据流的奇偶校验位,并将其与接收到的奇偶校验位进行比较。如果奇偶校验位相同,则不会检测到错误。如果它们不同,则检测到错误。

奇偶校验位仅用于检测错误。它无法纠正任何错误,因为无法确定流中哪个位不正确。如果接收到有错误的二进制流,接收者必须丢弃它。

这使得奇偶校验位错误方法不适用于高信噪比介质,因为成功传输可能需要很长时间。这种方法的优点是只需要一个比特来检测错误,这样可以增加一个周期内的传输次数。

例如,奇校验位发送器发送先前分析的流。如果流中的某个位发生了变化,则接收方如果将其与发送的校验位进行比较,则会获得不同的奇偶校验位。这种效果如图 3 所示。

图 3.错误流的奇偶校验

奇偶校验位用于需要简单的错误检测器并且如果发生错误可以重复传输的应用。最重要的应用是串行数据传输。它基于 7 或 8 个数据位、一个偶校验位和一个或两个停止位的通用格式。

奇偶校验位的其他应用是 SCSI 总线、PCI 总线和许多微处理器指令高速缓存。因为 L-cache 数据只是主存的一个副本,所以如果发现它被损坏,可以忽略它并重新获取它。

逻辑实现

用于错误检测的奇偶校验位的主要优点之一是其计算简单。为了获得偶校验,只需要对二进制流中的数据位进行模 2 和或 XOR 即可获得奇偶校验位。

一旦获得偶校验,奇校验可以作为偶校验的倒数获得。

如前所述,本应用笔记实现了二进制奇偶校验生成器和校验器的两种变体。两者都有一个偶数输出位和一个奇数输出位,如果检测到相应的奇偶校验,则将其设置为高电平。此外,它们有一个启用输入。如果使能高,则计算奇偶校验。否则,两个奇偶校验输出都设置为低电平。

在并行变体中,生成器或检查器获取 9 长度二进制流的奇偶校验位。有了这个长度,它可以被生成器用作 9 位处理器或仅使用 MSB(第 9 位)作为另一个处理器的级联输入的 9 位以上的处理器。

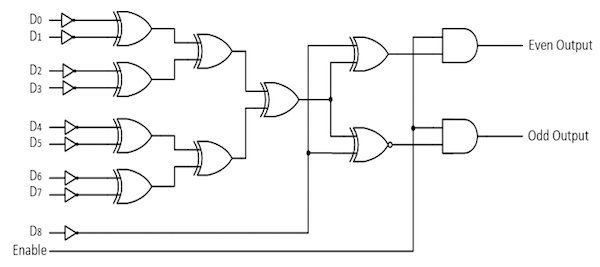

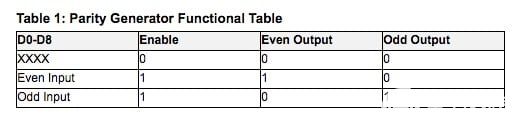

图 4 显示了 9 位长度并行输入奇偶校验器的逻辑图。

图 4.奇偶校验生成器逻辑图。

表 1 显示了奇偶校验生成器和校验器的功能表。

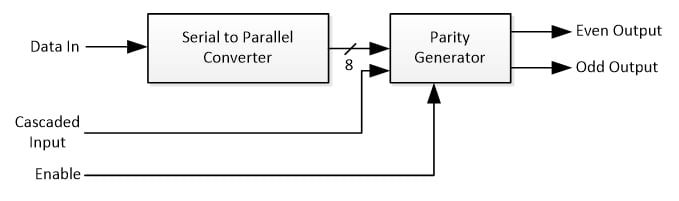

在串行变体中,输入级包括串并转换,因此转换器的输出连接到奇偶校验发生器电路。该方案如图 5 所示。

图 5.串行输入奇偶校验发生器示意图

此变体还包括一个额外的级联输入,因此可以使用多个 8 位奇偶校验检查器处理更多位。

串行到并行数据转换基于 Dialog 的 AN-1120。

当串行输入引脚上没有数据时,串行总线保持高电平。当要发送一个字节时,会在该字节之前发送一个逻辑低起始位以指示传输。之后,发送八个数据位,最后发送一个停止高电平位。这个序列可以在图 6 中看到。

图 6. 串行数据帧

在几个 GreenPAK IC 中,SPI 模块可用于实现串并转换。串行通信的波特率必须为 9600。

实施下降沿检测以检测起始位。当检测到它时,会设置一个连接标志位,以便触发两个计数器/延迟。其中一个名为 Bit Timer,被配置为具有等于位持续时间 (1/9600) 的周期。另一个名为帧延迟的计数器被配置为具有等于 10 位帧周期 (10/9600) 的延迟时间。

使用这些定时器,SPI 模块被连接,因此串行数据输入引脚连接到 MOSI 输入,位定时器输出连接到 CLK。八个数据位由 SPI 模块接收。

附加逻辑用于控制时钟信号,因此当帧周期过去时,SPI 时钟停止,数据保存在寄存器中。

有关 SPI 到并行转换器的更多详细信息,请参阅 Dialog 的 AN-1120。

实现和配置

如前所述,奇偶校验生成器和检查器有两种变体,使用两个不同的 Dialog GreenPAK 实现。

并行输入变体使用 SLG46536V 实现。

为了实现位反转,如图 4 所示,使用了 9 个 LUT,配置为反相器。这可以在图 7 中看到。

图 7.位反相器

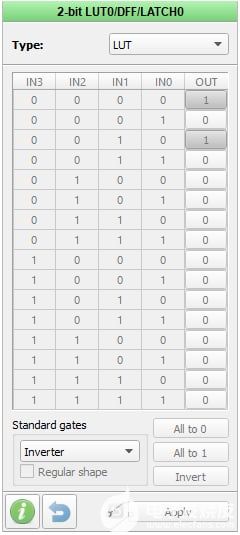

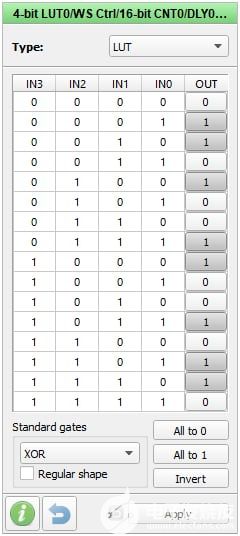

通过使用两个 4 位 LUT,实现 XOR 以获取每个半字节数据的结果位。它们的配置如图 8 所示。由于没有更多的 2 位 LUT 可用,两个半字节之间的 XOR 由 3 位 LUT3 处理,第三个输入连接到 GND。

图 8. XOR 处理器

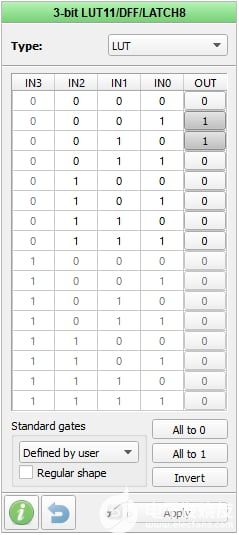

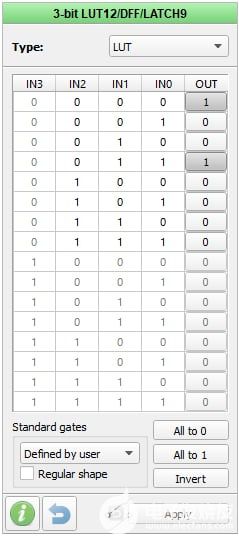

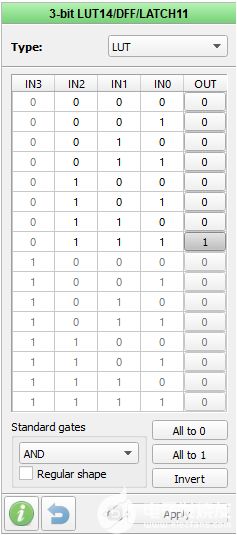

为了获得处理第 9 位输入的结果位,通过将输入 2 连接到地来使用 3 位 LUT11 和 3 位 LUT12。它们的配置如图 9 和图 10 所示,分别处理 XOR 和 XNOR。

图 9.第9 位 XOR

图 10.第 9 位 XNOR

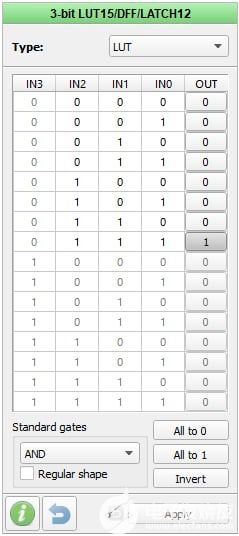

最后,偶数位和奇数位分别使用 3 位 LUT14 和 3 位 LUT15 分别与使能位和 VDD 相乘。这些配置可以在图 11 和图 12 中看到。

图 11.偶数输出控制

图 12.奇数输出控制

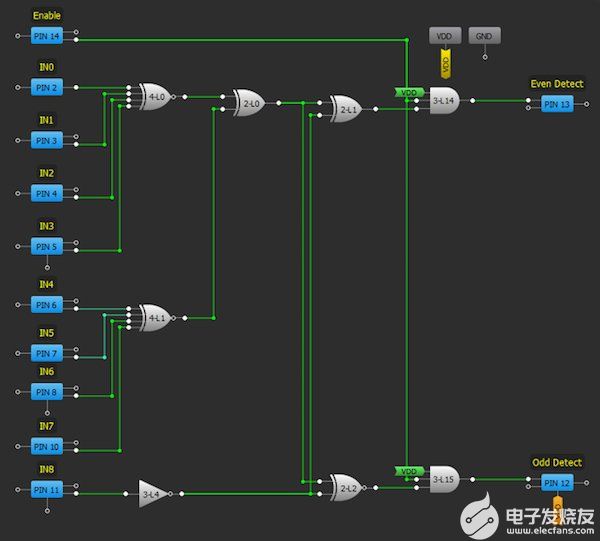

整个并行输入奇偶校验生成器和检查器设计如图 13 所示。

图 13.并行输入奇偶校验生成器和检查器

串行输入变体通过 SLG46536V 实现。它有两个可以互连的矩阵,因此其中一个用于实现串并转换器,另一个用于实现奇偶逻辑。

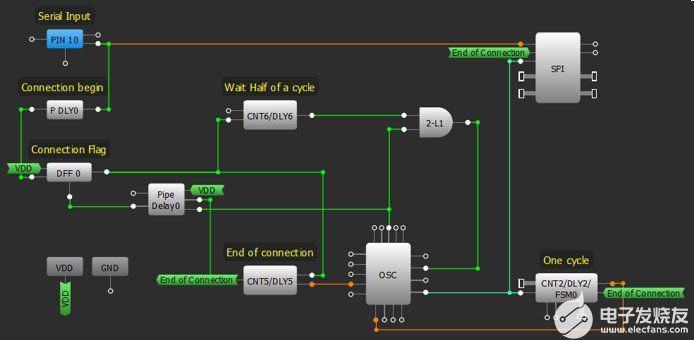

在图 14 和图 15 中,可以看到 SLG46536V 的矩阵 0 与实现的串并转换器。

图 14.串并转换器(矩阵 0)

图 15. 串并转换器(矩阵 1)

引脚 10 用作串行数据输入。如前所述,具有延迟输出的下降沿检测器通过 P DLY0 实现。该信号用于指示接收开始,由 DFF0 和 DLY6 保持。

一旦传输开始,CNT2 产生一个频率等于 9600 的信号。这是通过对振荡器的输出时钟进行分频来完成的,该时钟对应于由 2 位 L1 控制的内部环形振荡器。CNT2 配置如图 16 所示。

图 16. CNT2 配置

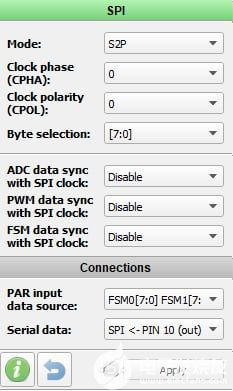

数据由 SPI 模块接收,配置为 S2P 模式,数据长度为 8 位。这可以在图 17 中看到。

图 17. SPI 配置

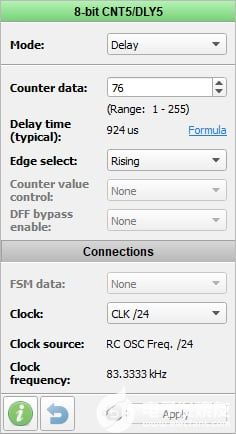

接收使能,直到 CNT5 达到最大计数,该最大计数被配置为 8/9600 以接收 8 个数据位。计数器使用内部 RC 振荡器 (2 MHz) 除以 24。其配置如图 18 所示。

图 18. CNT5 配置

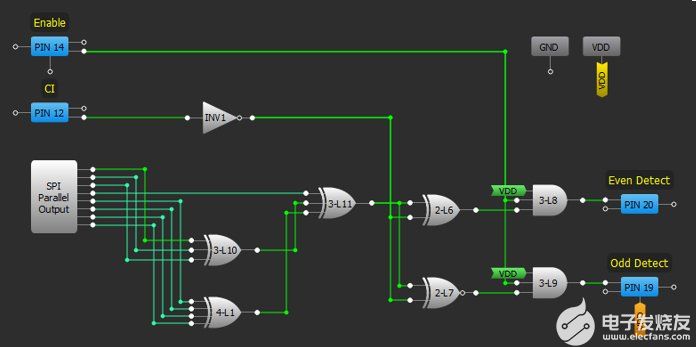

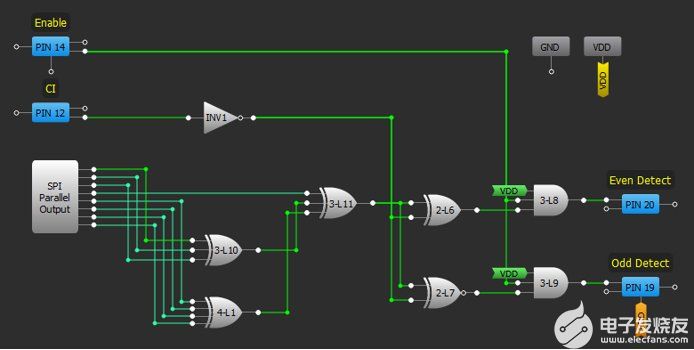

接收到数据后,将由矩阵 1 中实现的逻辑进行处理。矩阵 1 可以在图 19 中看到。

图 19.串行输入奇偶校验器

数据位来自 SPI 模块的并行输出。8 位的 XOR 使用 3 位 LUT10、4 位 LUT1、2 位 LUT4 和 2 位 LUT5 实现。最后,2 位 LUT6 和 2 位 LUT7 分别使用级联输入(引脚 12)实现 XOR 和 XNOR。启用控件由 3 位 LUT8 和 LUT9 进行“与”运算。

结果

为了测试实现,分别分析了二进制奇偶校验生成器和校验器的两个变体。

通过生成要由生成器处理的已知数据来测试并行输入奇偶校验生成器,以便检查输出。在这种情况下,使用的数据是

数据

0X1110011

X 会周期性地从 0 变为 1。这样,当 X 为 0 时预期为奇数结果,而当 X 为 1 时预期为偶数结果。

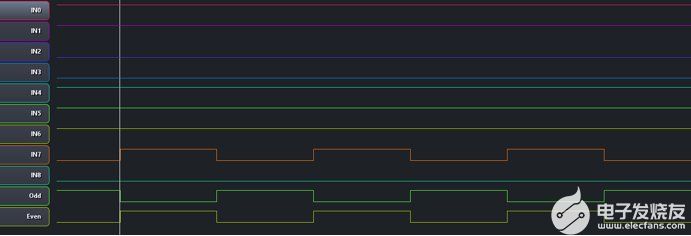

使用逻辑分析仪测量的输入信号和奇偶检测输出。在图 20 中,记录的信号显示为正确运行。

图 20.并行输入奇偶校验发生器测试

通过独立传输两个字节、处理它们并验证结果来测试串行输入奇偶校验生成器变体。选择传输的字节来分析奇数字节和偶数字节。

在奇数数据情况下,使用的数据是

奇数数据

11001101

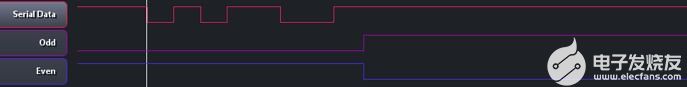

图 21 显示了使用逻辑分析仪记录的串行输入数据和奇偶检测输出。

图 21.串行输入奇偶校验发生器奇数测试

奇数输出为低,直到收到奇数数据。之后,奇数检测输出为高电平,偶数检测输出为低电平。

在偶数数据情况下,使用的数据是 10011001。

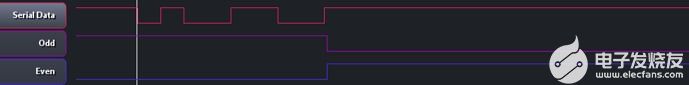

图 22 显示了使用逻辑分析仪记录的串行输入数据和奇偶检测输出。

图 22.串行输入奇偶校验发生器偶数测试

在这种情况下,先前的奇数数据被重新发送,因此奇数输出为高电平,而偶数输出在接收偶数数据之前为低电平。接收到偶数数据后,奇数检测输出为低电平,偶数检测输出为高电平。

结论

在本应用笔记中,我们实现了二进制奇偶校验生成器和检查器的两种变体,用作数据传输的错误检测技术。将奇偶校验位添加到传输的数据中,以使 1 的数量为偶数或奇数。该位用于检测二进制数据传输过程中的错误。一些商用 IC 可以用 Dialog GreenPAK 代替,从而可以降低应用规模和成本。这两个变体显示了数据输入方法如何可以是并行或串行的。这对于在不同的应用程序中应用奇偶校验生成器很有用。

-

什么是奇偶校验 奇偶校验的基本原理 奇偶校验电路什么意思2023-10-17 6108

-

芯教程|平头哥助力昊芯HX2000系列芯片专题SCI串口通讯奇偶校验(二)SCI增强FIFO2022-11-08 1913

-

增强FIFO模式下的奇偶校验2022-11-02 1983

-

数字二进制计数器的设计和实现2022-07-28 2887

-

串口通信的奇偶校验位的两种类型介绍2020-09-04 4051

-

嵌入式里数据差错控制技术之奇偶校验2020-04-16 3013

-

奇偶校验是什么2019-07-31 4193

-

奇偶校验器_奇偶校验设计程序2011-11-11 6115

-

奇偶校验码,奇偶校验码原理是什么?2010-03-17 63717

-

什么是二进制计数器,二进制计数器原理是什么?2010-03-08 32036

-

二进制编码和二进制数据2009-10-13 5269

全部0条评论

快来发表一下你的评论吧 !