汽车显示器接口设计关键技术分析

汽车电子

描述

IMS Research的调查显示,带有视频功能的汽车音响主机的数量将会由2006年的850万台增长到2015年的2660万台。为了既能向驾驶员提供信息,又不分散其注意力,显示器需要安装在远离汽车音响主机的位置,并将画面投影到挡风玻璃的背面。这种结合了图像源和面板的视频接口正在越来越多地从模拟视频技术转向质量更高的RGB(红绿蓝)数字视频格式,后者已成为LCD显示器中使用的标准接口。前端显示应用的电缆长度通常保持在1到3米的范围内,而后座娱乐(RSE)单元的电缆则需要达到8米甚至更长。这种连接支持千兆位/秒的数据传输速率,远超过传统车载网络的波特率,并可以利用点对点串行器/解串器(SerDes)解决方案完美实现。与传输一路较宽的并行视频总线相比,这种芯片组大大降低了传输线和连接器的引脚数量,从而实现了出众的系统级优势。

为满足汽车显示器接口方面的严苛要求,比如高数据吞吐量、超薄布线、高级信号调节、可检测性以及超低EMI(电磁干扰)等。美国国家半导体(NS)公司开发出DS90UR905/6 和DS90UR907/8 SerDes芯片组,该产品是能将分辨率从QVGA(400 x 240)扩展到24位色深的XGA(1024 x 768)的嵌入式时钟SerDes解决方案。宽范围的像素时钟频率使汽车制造商只需在其整个车型系列中采用一个数字视频显示接口方案,即可覆盖从双画面的小仪表盘面板、中控台的LCD到更大尺寸的RSE显示器应用。

视频应用和SerDes概念

SerDes组件的目标应用领域是平板显示器链路接口,它可以通过一根较长的串行电缆把图像主机与显示器连接起来。典型的例子包括:中央信息显示器(CID)、仪表盘、头枕上的娱乐显示器或为后座乘客准备的车顶下降式显示模块,如图1所示。这些新型芯片组是NS推出的"FPD-Link II"系列产品中的一组,它们可以将一个视频源的27位数字RGB色彩信息和时间控制信号转换成一个嵌入了时钟信息的单一串行数据流在双绞线上传输。芯片组在I/O(输入/输出)层采用高速的差分信号,也就是说,在"真"(正)端子上传输实际信号的同时,"互补"(负)端子上传输与之对应的相反极性信号。

图2在系统层面上描述了视频传输的概念。除了颜色和时序位外,还有一个可选的I2C控制接口,它可替代通过常规引脚带选项实现的组件配置。芯片组支持18bpp(每像素位)或24bpp的色深。彩色显示器使用3个子像素(红、绿、蓝)来定义一个单独的像素。由于每个像素有18位(6位红,6位绿和6位蓝),我们可以得到26.2万种颜色。大多数人的眼睛可以看到1000万种以上的颜色,这也就解释了为什么使用24bpp已成为趋势:它能提供超过1600万种颜色,可实现更丰富的用户体验和平滑的颜色梯度。像素时钟范围现已极宽:频率可从5MHz 到65MHz,这使得串行链路速率从140Mbps提高到1.82Gbps,涵盖了汽车显示器的全部主流分辨率。

并行LVCMOS输入和输出信号可以分别灵活地对准同步发射器输入及接收器恢复输出时钟(PCLK)的上升沿或下降沿,这一特性大大简化了串行器至图像控制器以及解串器至LCD计时控制器的接口连接。在发射器并行时钟周围的一定频段内,SerDes芯片组在"预同步"接收器的PLL时无需外部参考时钟(石英或振荡器)。甚至在一切可能的随机数据模式传输过程中该同步都能得到保证,这被称为"随机数据锁定"特性。这不仅节省了参考组件系统的成本,而且消除了另一个潜在的电磁干扰源。该性能还可以实现"热插拔",即在不需要任何特殊排序或训练模式的情况下,就可以对送往解串器的串行数据流执行断言/取消断言操作。

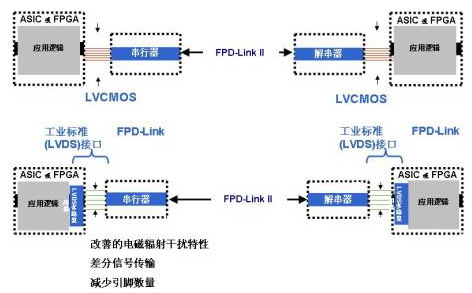

一旦接收器PLL锁定在发射器的频率下,即可由LOCK输出标志引脚显示这一状态,确保接收器输出的数据完整性。DS90UR907/8芯片组具有DS90UR905/6芯片组的一切特性,两耳区别在于输入输出不再是发送LVCMOS信号的并行总线,而是遵照开放的工业标准"FPD-Link"。很多现代化的图像控制器、显示定时控制器、ASIC和FPGA都支持这种"一级串行化"技术,它采用适合18bpp的3个数据通道,或者适合24bpp的4个数据通道,每一个都有一路并行时钟通道。电信号的发送遵循开放的ANSI/TIA/EIA-644A标准,该标准又称作"LVDS"(低压差分信号传输)。使用该接口技术代替常规LVCMOS的优势在于:采用差分信号可降低电磁干扰,并减少组件的引脚数量,如图3所示。

图3 FPD-Link系统接口选项的优势

FPD-Link II有效负载

在每一个像素时钟周期内,28个"次符号"在差分I/O上经过时分多路复用,转换成一个串行数据流。嵌入的有效负载包含24个颜色位、3个定时信号(水平同步-HS、垂直同步-VS和数据使能-DE)以及附加位。互连线路速率为28x像素时钟。在65MHz下,该速率转化为1.82Gbps。串行数据流由前端的"CLK1"HIGH 位和末尾的"CLK0"LOW位限定,由此可在每一个帧之间实现高低电平的平稳过渡,令串行器的PLL可以参照其进行同步并提取嵌入的时钟信息。两个附加位("DCA"和"DCB"位)位于每一个帧中间,它们包括嵌入在DCA 和 DCB位过渡过程的定时信号。有效负载位为了降低谐波电磁干扰和改善信号质量,经过了随机化、平衡和加扰处理,同时为交流耦合建立了直流平衡。

由于电缆连接越长,发射器和接收器模块之间越有可能出现接地电位漂移,交流耦合接口方案则可通过在传输线中采用串联电容实现电势解耦。串行器中的直流平衡编码器和相应的解串器中的直流平衡解码器可在串行链路上实现高低位之间的均匀分布,以防止ISI(符号间干扰)效应和由电容引起的静态模式的阻塞。通过在两端配置电容,该方案也可以在电缆损坏或者对地或板上净电压出现短路时提供输入/输出短路保护。随机化和不规则性不仅能保证良好的眼图开度,同时还能最小化互联线路的电磁干扰,总体来说其编码效率高于85%。

增强的信号调理能力

信号调理技术在推动长距离高速连接方面发挥了至关重要的作用,在串行器端采用了信号还原特性,图4是一个信号还原操作的例子。这一串转换的比特流,依次为0、1、000和1,图形顶部给出了单端(SE)波形,可以在真值和输出端子处相对于地电位进行测量。图形底部给出了差分(DIFF)信号,相当于在其端子范围内接收器输入端的差分电压摆幅。对于第一次转换,发送的第一个信号是0,形成全差分摆幅。下一次转换是一个1,同样是全电压摆幅。接下来在C、D和E时间帧中是一系列0,其中第一个0是全电压摆幅。随着之后时隙D和E中第二个和第三个0的到来,幅值将会下降,表示被信号"还原"了。因此电缆中的静电荷将受到限制,否则它将会随着时间增强。这使得在时隙F发送的末位1又形成全差分摆幅。信号还原特性通常是在传输线路中平衡高低频信号的内能。总体效果就是清晰的信号眼图张开,在由1或0组成的长序列之后是以一个单独的比特位转换。信号还原层是可编程的,以便为特定电缆媒介调整至最佳补偿水平。

此外,信号还原特性在可调差分输出电压(Vod)方面有不错的效果,即它可以使长电缆传输的差分输出电压(Vod)加倍。信号还原不需要大幅降低接收器输入的信号幅度就能做到信号恢复。解串器的输入端集成了一个电缆均衡器,在再生全部信号波形时,此功能相对输入信号而言等同一个高通滤波器,可以部分消除由传输媒介引起的低通滤波器效应。均衡器在1.5dB到12dB的增益之间具有可编程性。当然,所有增强的信号处理特性也可以协调使用,为长电缆传输中的无差错数据恢复建立足够的眼图开度。

扩频时钟

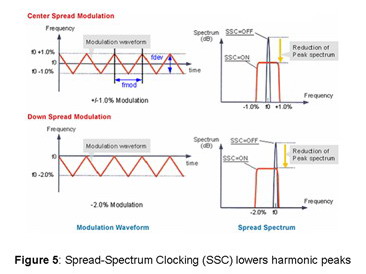

解串器通过一块集成可配置的扩频时钟(SSC)生成器得到增强。在接收器输出总线端,这会导致输出时钟频率和数据频谱随着时间推移而以几十KHz的低调制率产生轻微变化。如图5所示,频率变化可以发生在名义像素时钟中心频率附近("中心扩频调制"),或朝向更低的频率("向下扩频调制")。频谱扩展百分比可高达±2%。扩频时钟将峰值能量分散在更宽的频谱范围内,从而大大降低了电磁干扰噪声水平,而不是在同一时间点上、以恒定频率来转换所有输出,此时的辐射噪声集中在一个窄频段内,所有输出数据都与输出时钟同步,这使得数据和时钟得到有效扩展。特别是DS90UR906接收器输出具有低压(LV)CMOS接口选项,可以大大降低电磁辐射。

增强的诊断能力

另一个特性是内建自测试(BIST)功能。在这种模式下,发射器发送伪随机码序(PRBS)。接收器内部产生同样的序列,并与接收的位模式进行比较。为了在整体测试时间和需要验证的最低比特误码率之间找到最佳折衷方案,用户可以控制BIST的持续时间。在遇到有误码的有效负载时,PASS引脚会以时钟方式进行切换。PASS引脚存放BERT(误码率测试)的最终结果。如果测试失败,说明出现了一个或多个负载错误;如果测试通过,说明PRBS序列的传播和接收均无差错。在链路远端,BIST无需任何数据发生器、数据记录或测量系统。汽车生产商可使用BIST模式来测试系统和检查链路运行。它还可以用作系统开发阶段的试验台,在没有视频源的情况下向整个链路发送数据,同时仅在发射器上施加时钟信号。在服务或故障排除阶段,可利用系统测试来验证链路正常工作,以此在主机或显示端上锁定问题范围。最终当汽车启动后,显示接口可进行例行检查并验证连接性。

更多增强功能

更多增强功能包括集成的终端电阻,它降低了电路板设计的复杂性,使成本更低,板极空间更小。解串器的输入端提供了一个终端共模滤波器引脚。建议用户将共模引脚通过电容接地以确保稳定,并保证频率滤除共模电压。这将减少对外界的电磁辐射水平,同时可以提高对外界噪声源的抵抗能力。通常通过大电流注入(BCI)测试对数字视频链路对外部干扰的抵抗能力进行研究,利用电感将高达300mA的侧电流调制到电缆屏蔽罩上。I/O 库通过VDDIO供电,1.8V或3.3V均可。这样的灵活性可以利用低接口电平的优势,并提供与下游器件的兼容性。

一般来说,当在1.8V电压下操作组件时,电磁干扰水平也随之降低。断电情况下,解串器的输出电压状态可以设置为三态(高阻)或低阻。像素时钟(PCLK)状态也可设置为三态或低阻,以选择停止内部振荡器。在后者的情况下,无论是否有输入信号,时钟输出会一直存在。当接口仅与短距离的轻负载总线连接时,接收器驱动强度(RDS)特性可以最小化输出总线的电流消耗,减慢输出边缘转换率并最终降低电磁干扰。芯片组支持-40℃ 到 +105℃的超宽温度范围,可适用于不同工作环境下的各种汽车电子系统。这些芯片组采用LLP封装,占用的空间很小,并通过了RoHS认证和AEC-Q100 Grade 2标准的全面汽车应用认证。

本文小结

新型DS90UR905/6 和DS90UR907/8 FPD-Link II型芯片组具有许多系统优势和增强特性。并行视频总线通过一个嵌入式时钟串行化到一个单组中,这降低了系统成本,消除了时钟/数据偏斜问题,减少了噪声,并将链路延伸至远途电缆距离。芯片组支持从QWVGA到24位色深XGA的所有普通汽车LCD分辨率。为了促进系统设计、合格审定和批准,设计人员能将更多注意力集中到如何降低EMI的特性上。这样可以在不牺牲可靠性的情况下尽可能降低防护要求的成本。诊断BIST模式有利于工厂测试和实际应用,对故障排除的测试和诊断也有益处。作为FPD-Link II系列产品中的第三代芯片组,其组件基于已验证和可信赖的IP协议,并且与前几代芯片组后向兼容。FPD-Link II芯片组系列代表了针对汽车行业进行优化并支持真正即插即用的方案,因为它与低密度线路结合使用时不影响性能,且带宽高、功耗低、低EMI、耐用并可实现自主链路同步。

- 相关推荐

- 显示器接口

-

LCD显示的关键技术2021-09-10 0

-

汽车总线及其关键技术的研究2012-07-10 0

-

嵌入式系统关键技术分析与开发应用2012-08-09 0

-

CDMA原理与关键技术2012-08-16 0

-

【视频】智能家居系统关键技术分析与应用2016-02-26 0

-

新能源汽车电机驱动关键技术及发展趋势2016-05-12 0

-

无人驾驶汽车的关键技术是什么?2020-03-18 0

-

无人驾驶分级及关键技术2021-01-21 0

-

智能网联汽车的关键技术2021-07-27 0

-

明白VPP关键技术有哪些2021-08-31 0

-

介绍汽车区域控制器的一些关键技术和MCU解决方案2022-10-26 0

-

三星:空中投影是未来显示器的关键技术2016-05-30 2112

-

显示器接口2016-12-16 644

-

反激变压器分析与设计关键技术2022-06-09 492

-

汽车区域控制器的关键技术和MCU解决方案深度分析2023-10-18 1896

全部0条评论

快来发表一下你的评论吧 !