推挽输出电路工作原理以及注意事项(推拉输出电路)

推挽输出电路工作原理以及注意事项(推拉输出电路)

描述

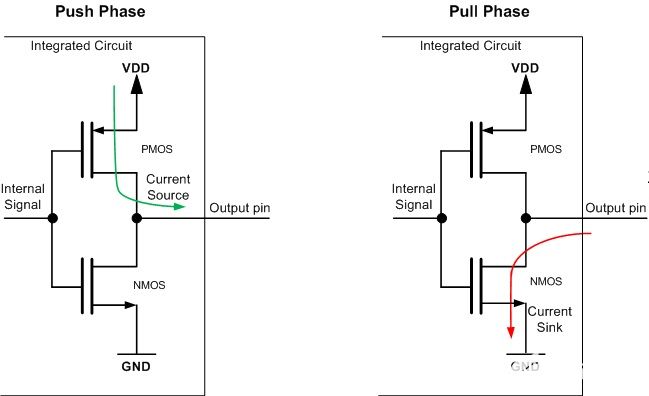

推挽输出又叫推拉输出,是最常见的输出配置了,正如它的名字那样,推拉输出能够驱动输出两种电平。一种是拉接到地(从负载灌入电流),另一个被推到电源电压(输出电流到负载)。推挽输出可以使用一对开关来实现。在集成电路中一般使用两个晶体管搭建。在下图中,我们可以看到使用 PMOS 和 NMOS 晶体管构建推挽输出配置。左侧显示的是推阶段的电路状态,右侧显示的是拉阶段的电路状态。

1.推挽电路工作原理

推动阶段——当连接到晶体管栅极的内部信号设置为低电平时,PMOS 晶体管被激活,电流从 VDD 流经它到输出引脚,NMOS 晶体管处于非活动状态(开路)且不导通。

拉动阶段——当连接到晶体管栅极的内部信号设置为高电平时,NMOS 晶体管被激活(关闭)并且电流开始从输出引脚流过它到 GND。同时,PMOS 晶体管处于非活动状态(开路)并且不传导电流。这种类型的输出不允许在总线配置中将多个设备连接在一起,推挽配置最常用于具有单向通信线上(线路上的信号传输仅在单一方向,比如SPI、UART等)。

2.电路应用注意事项

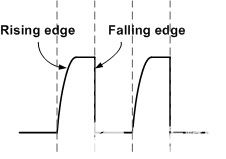

推挽输出在生成的输出数字信号的斜率方面提供了更好的性能,现在很多IC甚至可以配置信号上升或者下降的斜率,从而允许我们在传输速度和EMI方面找到最佳的平衡点。上升沿斜率——上拉电阻与线路的固有电容相结合,形成一个低通滤波器。从而我们可以根据电阻器的值和线路的电容来调整上升沿斜率,上升沿的斜率与下降沿的斜率可能存在明显差异。一般来说下降沿更尖锐,因为它是使用具有非常低内阻的晶体管实现的。而上升沿是由上拉电阻形成的,前面提到的低通滤波效果更加明显。

图 1 开漏输出产生的方波信号边沿

功耗和噪声干扰——在选择上拉电阻值时我们需要权衡。当线路上的设备驱动输出低电平时,它会导致较高的电流流过较低值的上拉电阻,这会增加功耗的问题。但是,选择较高值的电阻器会反过来导致流过电阻器的电流较低,这将使线路上的外部干扰(噪声)更容易影响信号状态。应该注意的是,在很多MCU中,配置为推挽的输出引脚在大多数情况下可以动态重新配置为输入,这是通过关闭两个晶体管来实现的,从而在线路上实现高阻抗状态。然后可以从其他外部设备采集输入信号。

-

555电路调试技巧和注意事项2024-11-12 3037

-

推挽输出电路的工作原理2023-12-26 4598

-

什么是推挽输出 开漏输出和推挽输出的区别2023-08-31 25862

-

探讨高输出电流应用时的注意事项 其12023-02-23 1674

-

推挽放大电路的工作原理及电路图讲解2023-01-31 15466

-

新手求助开漏输出与推挽输出有什么不同?2021-04-19 2163

-

电路PCB布局注意事项2021-03-01 4241

-

空气加湿器的特征、注意事项以及工作原理2020-10-14 3890

-

全程图解MOS管工作原理及注意事项2019-07-27 3578

-

设计高速电路板的注意事项2017-01-28 1235

-

电路设计注意事项2016-06-17 1281

-

PLC输出电路(继电器,晶体管,晶闸管输出)区别和注意事项2012-08-20 3528

-

电容降压的工作原理、容抗计算以及注意事项2011-10-31 9425

-

关于PLC输出类型的选择及使用中的注意事项2009-06-20 1599

全部0条评论

快来发表一下你的评论吧 !