DRAM命令到底是什么

描述

DRAM命令到底是什么

本文将仔细研究用于控制和与 DRAM 交互的命令。

我之前的文章介绍了动态随机存取存储器,即 DRAM。DRAM 是一种需要经常动态刷新的 RAM。这是因为 DRAM 使用一组电容器来存储数字信息。当存在电荷时,存储二进制“1”,而没有电荷表示二进制“0”。DRAM 被组织成多个存储体,这些存储体进一步分为行和列。电容器位于这些行和列的交叉处。

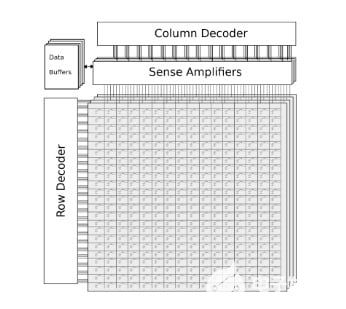

图 1 显示了上一篇文章中介绍的 x4 DRAM bank。

图 1. 带有读出放大器和解码器的存储器阵列

但是如何实际使用 DRAM 呢?处理器或内存控制器如何告诉 DRAM 在特定位置返回或存储特定数据?了解发送到 DRAM 芯片的命令是实际设计使用 DRAM 的系统的第一步。

基本 DRAM 命令

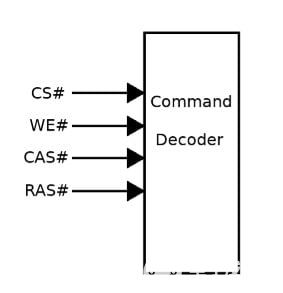

虽然 DRAM 可能因制造商而异,但大多数 DRAM 芯片使用一组基本命令来执行操作。为了执行命令,内存控制器会将值写入 DRAM 中的一组输入。这些输入属于 DRAM 的命令解码器。该解码器有一个 4 位输入,根据位的组合,请求不同的命令。

图 2. 带输入的 DRAM 解码器(# 符号表示这些是低电平有效信号)

这些低电平有效输入都有名称,通常定义为 CS、CAS、RAS 和 WE:

CS:片选(启用或禁用命令解码器)

RAS:行地址选通

CAS:列地址选通

WE: 写使能

这四个输入允许将多达 16 个命令内置到 DRAM 中。

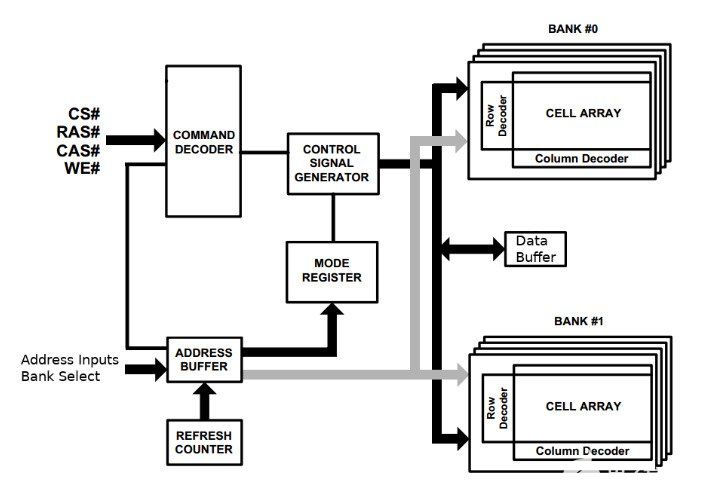

图 3 显示了 DRAM 芯片的简化视图。它可以用作参考,以更好地理解列出的不同命令。

图 3. DRAM 参考。图片由Alliance Memory提供

命令禁止

命令禁止,或有时称为设备取消选择,禁用在 DRAM 上执行命令的能力。要使用该命令,请将 CS 输入拉高(忽略其他输入,即“不关心”)。如前所述,CS 代表芯片选择并禁用命令解码器。因此,这将被拉高以抑制命令是有道理的。

启用

激活本质上是行访问命令。意思是,它打开一行并将电荷从电容器移动到感应放大器。访问一行总是在 DRAM 中的一列之前完成。该命令与存储体地址寄存器(选择当前存储体)和行地址寄存器(选择所需行)的输入配对。关于激活命令的一个重要注意事项是,当前打开的行保持打开状态,直到发出预充电命令(稍后将详细介绍预充电)。要使用此命令,大多数 DRAM 需要将 CS 和 RAS 拉低,而将 CAS 和 WE 拉高。

预充电

预充电会停用当前在银行中打开的行。当发出预充电命令时,DRAM 被告知恢复从电容器行读取的值。这是由读出放大器完成的,当完成时,为另一行访问做好准备。通过将 CS、RAS 和 WE 拉低并将 CAS 拉高来执行预充电。

读

读取命令也可以被认为是列读取命令。当与适当的存储体地址和列地址相结合时,最近从激活命令(行访问)移入读出放大器的数据现在被推送到数据总线上。DRAM 通常包含“读取和自动预充电”命令,该命令执行列读取,然后关闭/预充电行。这样,不需要发出单独的预充电命令。如果需要访问同一行但不同的列,则根本不会发出预充电,并且该行将保持打开状态。要使用读取命令,CS 和 CAS 被拉低,而 RAS 和 WE 被拉高。

写

除了数据的方向之外,写入命令实际上与读取相同。在写入命令期间,数据从数据总线中拉出并放入选定的存储区、行和列。自动预充电可以像读取一样执行,并在写入完成时关闭当前激活的行。为了执行写操作,CS、CAS 和 WE 被拉低,而 RAS 保持高。

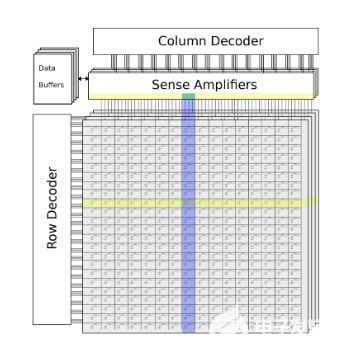

图 4 以黄色显示激活命令(行访问),随后以蓝色显示读/写命令(列访问)。行列交叉处的数据(以绿色显示)在读出放大器和数据缓冲器之间移动。

图 4. 突出显示激活和读/写命令

刷新

DRAM 与其他类型的随机存取存储器的不同之处在于,用于存储器存储的电容器会随着时间的推移而泄漏电荷。因此,DRAM 是动态的,因为它需要定期刷新。这就是刷新命令的用武之地。在 DRAM 中,刷新命令每隔一段时间就会发出一次。刷新的一个重要方面是任何活动的银行都应该在发出命令之前进行预充电。为了执行刷新 CS、RAS 和 CAS 被拉低,WE 为高。

刷新后,DRAM 跟踪最后刷新的行并递增刷新计数器,以便下一个刷新命令对下一行进行操作。请记住,当发出刷新命令时,会刷新每个 bank 中的当前行。大多数 DRAM 将每 64 毫秒执行 8192 次刷新周期。那是每 7.813 μs。尽管设备密度不断增加,但这种情况一直保持不变。

其他命令

其他常见的 DRAM 命令包括 NOP(无操作)、突发终止和加载模式寄存器。NOP 用于强制 DRAM 什么也不做。这在 DRAM 需要等待时很有用,例如当前正在刷新时。实际上,对 DRAM 的读取和写入是在短时间内完成的。Burst terminate 将截断读或写命令,即在完成之前将其停止。DRAM 可以置于不同的模式。这些模式通过加载模式寄存器命令进行更改。

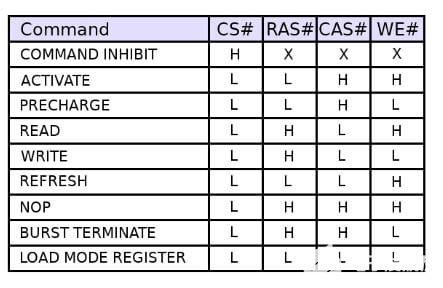

图 5 显示了一个真值表,列出了用于执行不同 DRAM 命令的解码器输入组合。

图 5. DRAM 命令——真值表

结论

本文讨论了 DRAM 能够执行的不同命令。这些命令由与 DRAM 交互的内存控制器或 CPU 发起。

通过写入 DRAM 命令解码器的输入来执行命令。任何需要认真工作的系统都将具有板载内存。如果您了解这些命令,那么在您的下一个项目中实现 DRAM 将会容易得多。

-

PLC到底是什么呢?2014-10-10 5283

-

这是到底是什么元件?2016-05-26 5103

-

请问CKFA到底是什么2018-08-20 2516

-

这个到底是什么电路2019-01-20 1286

-

DSP到底是什么?DSP的要素是什么?2021-03-05 3329

-

QPainter到底是什么?2021-09-28 1862

-

PID控制算法到底是什么?2021-10-11 1701

-

STM32时钟树到底是什么?2021-11-11 1861

-

STM32固件库到底是什么?2021-11-30 2259

-

RGB屏到底是什么?2022-02-14 1952

-

看看芯片到底是如何设计的2022-03-02 3022

-

AT指令,AT固件,这个AT到底是什么意思?2023-09-26 1164

-

“电感饱和”到底是什么意思?2021-01-28 2088

-

单片机的“性能”到底是什么?2023-10-24 1635

-

IEC 到底是什么?为什么它能影响全球?2025-09-04 4040

全部0条评论

快来发表一下你的评论吧 !